二次雷达双门限检测接收机的研究及FPGA 实现*

2019-09-17严玉国杨宾峰

李 雷,严玉国,杨宾峰

(空军工程大学信息与导航学院,西安 710077)

0 引言

随着航空运输事业的发展,二次雷达在空中交通管制中发挥的作用越来越大,保障二次雷达的可靠工作对于空中交通事业的安全具有十分重要的意义。为了对二次雷达进行快速检测维护需要开发便携式二次雷达检测仪。便携式二次雷达检测仪不仅要求能够发射和接收处理二次雷达各种信号,而且要具有体积小、功耗低的特点。软件无线电技术和超大规模集成电路的发展为二次雷达检测仪的小型化提供了硬件基础。

AD9361 是ADI 公司推出的一款射频捷变收发器,内部集成了滤波器、混频器、AGC、以及ADC、DAC 等,通过配置寄存器就可以实现射频信号到基带信号的转变,直接提供零中频数据给FPGA 进行数据处理。因此,基于AD9361+FPGA 的硬件结构来实现二次雷达检测仪的开发。AD9361 主要完成射频信号到基带的转变,FPGA 对AD9361 输出的数据进行进一步的分析和处理。

1 双门限检测方法

传统的接收机只经过一次门限判决,大于门限的信号判定为“1”,小于门限Gate1 的信号判定为“0”。对于这种结构,在信号的接收过程中,如果杂波或噪声等干扰信号强度大于判决门限,那么就有可能造成误判,对于接收机正常接收信号造成影响,因此,需要剔除这部分干扰信号带来的影响。

对二次雷达接收机来说,干扰信号强度大于门限只是突发的,接收到的干扰信号与真实的信号不同,正常接收到的二次雷达信号应该是满足一定宽度的脉冲信号,为了剔除干扰信号,可以根据二次雷达信号格式以及FPGA 的工作时钟,确定真实信号对应的时钟数。对于满足时钟数限制的信号,判定为二次雷达信号,不满足的信号,则判定为噪声干扰,通过数字滤波进行剔除。如果FPGA 信号处理的时钟频率是f,真实信号的持续时间是t。那么对应的N 为:

根据计算出来的N,设定判决门限Gate2,判决门限的设定应该允许一定的误差,可以减小接收机的漏警概率,Gate2 与计数值N 的关系为Gate2=N-m,其中m 对应的是容许的误差值。对经过一次门限判决的信号,如果信号为“1”持续时间对应的计数值超过判决门限2,信号正常输出,否则认为是干扰信号,将信号输出为“0”。

2 双门限检测接收机系统组成

图1 接收机系统框图

双门限检测接收机的系统构成如图1 所示。具体工作过程为:

1)通过AD9361 实现信号的下变频,输出I、Q两路数字信号;

2)幅度提取模块根据I、Q 两路输入信号提取出信号的幅度;

3)根据信号幅度大小对接收增益进行调整,并对信号进行对数放大;

4)将经过对数放大的信号送入门限电路1 中,得到信号的判决门限Gate1;

5)将判决门限和经过对数放大的信号同时送入峰值提取电路中,首先进行峰值检测,然后完成半幅度检测,提取到接收的信号;

6)最后在门限电路2 中对半幅度检测结果与Gate2 进行比较,完成干扰脉冲的剔除,提取有用信号;

7)最后在信号处理模块中,根据二次雷达信号格式和相关协议对数据进行分析处理,提取信号中的信息。

以上步骤中,步骤1)是在AD9361 中完成的,步骤2)~步骤7)都是在FPGA 中完成。

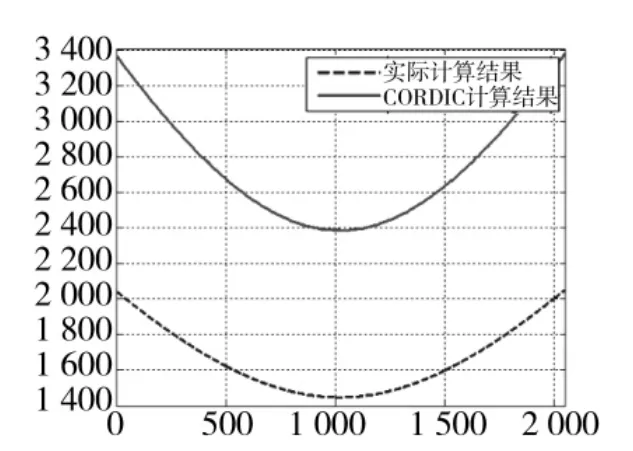

2.1 幅度提取

因为FPGA 是由逻辑门组成的硬件芯片,适合完成各种复杂逻辑运算,不擅长进行复杂的数学运算,所以需要根据实际运算需求,将复杂的运算近似为适合逻辑器件完成的运算。文献[1]中提出了一种适合硬件实现的开方近似算法,FPGA 实现简单,但是存在精度较低、误差大的缺点。图2 是文献[1]中的算法与实际结果的比较图,开方输入的两路信号,一路是从0 到2 048 递增,另一路是从2 048 到0 递减。图中实线对应的是实际的开方结果,虚线对应的是文献[1]中近似算法的计算结果。从图中可以看出,该近似算法与实际结果的误差较大。

图2 近似算法结果与实际结果比较图

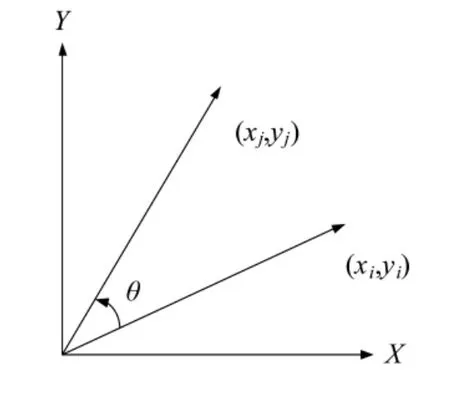

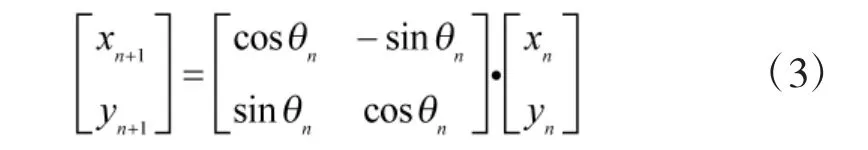

文献[2-6]中指出用CORDIC 算法完成超越函数的硬件实现。CORDIC 算法是Voder 在1959 年提出的。1971 年,Walther 对该算法的形式进行了统一,Meyer-base 第1 次利用FPGA 实现了该算法。CORDIC 算法可以将开方运算转化为简单的移位和相加运算,通过连续的角度旋转来实现,只需要一定的约束条件就可以在FPGA 平台上实现开方运算,完成I、Q 两路信号的求模运算。该算法的基本原理是从起点按照一定的角度不断旋转,逐步逼近终点[6]。图3 是CORDIC 算法的向量旋转示意图。

图3 CORDIC 算法坐标轴旋转示意图

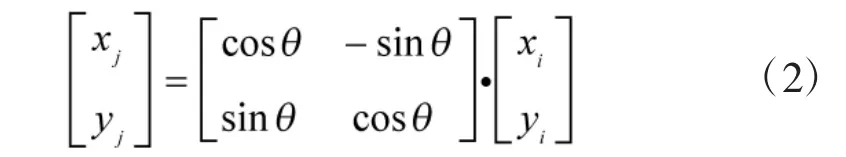

(xi,yi)是坐标旋转起点,(xj,yj)是坐标旋转终点。(xi,yi)和(xj,yj)的关系为:

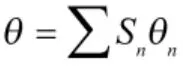

经过N 次迭代,得到(xi,yi)和(xj,yj)的关系:

其中

文献[5]中指出用CORDIC 算法实现开方、对数等运算的方法。文献[7]给出了CORDIC 算法的具体推导公式。可以得到开方的计算公式为:

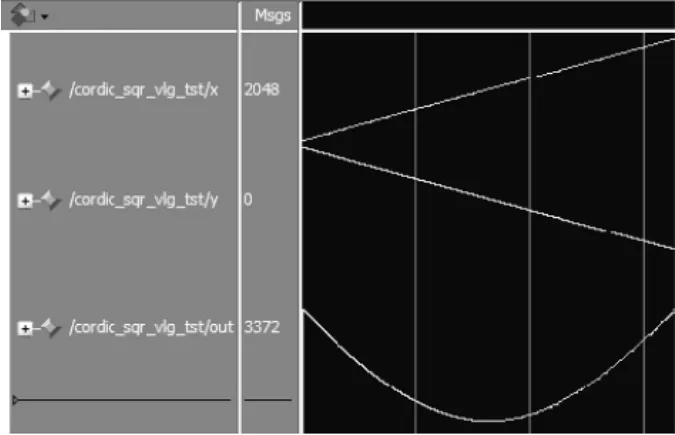

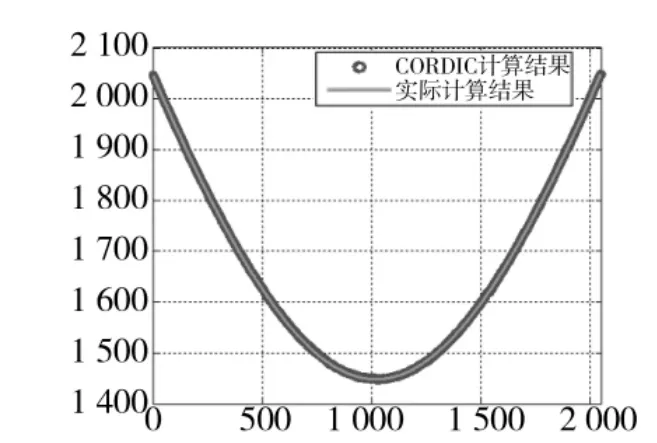

根据以上分析,在Modelsim 上仿真对CORDIC算法求开方进行仿真,图4 是在Modelsim 上仿真得到CORDIC 结果,其中x,y 分别是两路输入信号,x是从0 到2 048,y 是从2 048 到0,out 是CORDIC算法计算开方的结果,out 与实际开方结果之间的关系如式(8)所示。为了进一步对比分析CORDIC 计算结果与实际结果之间的关系,把计算结果导出到MATLAB 中进行分析处理。图5 中实线是CORDIC在硬件平台上的计算结果,虚线是实际的结果。图6中,对CORDIC 算法的计算结果乘以修正因子K,可以看出CORDIC 算法计算结果与实际结果基本一致。图7 是CORDIC 算法计算结果与实际结果的误差图,可以看出,最大误差不超过3,相对于12 位信号来说非常小,可以忽略不计,因此,在接收机中采用CORDIC 算法计算I、Q 两路信号的开方,完成信号幅度的提取。

图4 Modelsim 仿真结果

图5 CORDIC 计算结果与实际计算结果比较图

图6 CORDIC 修正结果与实际计算结果比较图

图7 CORDIC 算法误差图

2.2 自动增益控制

为了使接收机有较大的接收动态范围,需要根据信号的功率对接收机的增益进行动态调整。幅度提取电路输出的是接收信号的幅度,可以根据幅度的大小,进行相应的增益调整。文献[8]中提出了全数字AGC 的设计方案,该方案适用于连续信号的自动增益控制,因为二次雷达信号是不连续的脉冲信号,无法按照连续波自动增益控制的方式进行增益调整。文献[9]中提出通过统计接收端信号过门限瞬时值次数的方法,判断是否要对接收机进行增益控制,这种方法对微弱信号的检测有一定困难。根据二次雷达信号特点,先对幅度提取电路的输出结果与噪声电平进行比较,大于噪声门限一定值的信号,认为存在雷达接收信号,对这部分信号进行对数放大,小于门限部分,认为信号不存在,这部分信号不进行对数放大。

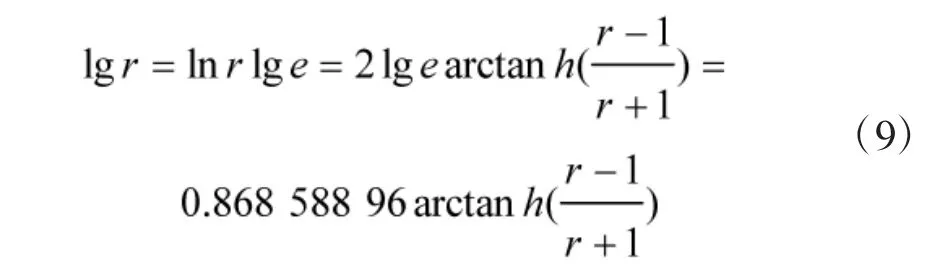

对数放大的特点是对小信号放大的倍数大,大信号放大倍数小,可以将接收信号的幅度压缩在一定的范围之内。CORDIC 也可以完成对数运算,根据对数和反双曲正切函数之间的关系,可以得到:

当CORDIC 算法,工作在向量模式下时,如果输入为(x0,y0,z0),那么输出为[10]:

在这种情况下,要计算r 的对数结果,需要令:x0=r+1、y0=r-1、z0=0,那么CORDIC 算法输出的zn就是对信号取对数的结果。借鉴文献[11]中提到的两级DAGC 方案,对幅度提取电路的输出结果进行对数放大,同时,还可以根据信号的幅度大小,调整AD9361 的接收增益,实现接收增益的两级调整,第一级是调整硬件的增益,第二级是在数字域对接收信号进行调整。

根据对数放大的特点,对接收信号进行对数放大。输入信号和输出信号之间的关系为:

其中,x(i)是输入信号,y(i)是输出信号,A 是一常数,V 是噪声门限,对于大于V 的信号,进行对数放大,小于V 的信号,认为是噪声,直接输出,不作任何处理。

图8 中蓝色信号是原始输入信号,从图中可以看出,经过一级对数放大之后,小信号得到放大,大信号得到缩小,但是差距还是很大。因此,提出一种多级放大的处理方式,在信号经过一级对数放大之后,将输入信号送到第二级放大器中,可以进一步缩小大小信号的差距。图8 中黑色实线是三级对数放大的结果,通过三级对数放大器之后,幅度相差很大的信号压缩到很小的范围,可以将小信号放大,减小漏警概率,而且可以将大信号压缩,方便后期的分析处理。

图8 多级数对数放大

2.3 门限电路1

门限电路对于信号的有效接收判决具有十分重要的意义,门限电路有两种形式,一种是固定门限,另一种是动态门限。考虑到接收机要求较大的动态范围,因此,选用动态门限。采用平均值法来求动态门限。

平均值法是一个求平均电路,对相邻的N 个信号求平均值,然后乘以门限检测因子K,作为判决门限。门限检测因子的选定与电路结构、信号特征等因素有关,需要在具体的电路中进行调试,找到合适的门限检测因子。

2.4 峰值检测

峰值检测电路包含3 部分,峰值提取电路、半幅度提取电路和二值化电路。峰值提取电路从大于判决门限的信号中提取出信号的最大幅度值;半幅度提取电路根据峰值检测结果,求出半幅度点对应的幅度值;二值化电路根据半幅度值对输入信号进行二值化,输出“0”、“1”信号。

图9 峰值检测电路

峰值检测电路的结构如图9 所示。将信号和门限1 同时送到判决器中,进行比较,大于门限部分进行峰值检测和半幅度提取,同时对信号进行延时,最后将延时后的信号与求出的半幅度值进行比较,大于半幅度值的信号输出为数字“1”,小于半幅度值的信号输出数字“0”。完成信号的二值化,即将12 位的有符号数字信号转为“0”、“1”序列,提取出二次雷达应答信号对应的脉冲序列。

2.5 门限电路2

门限电路2 也可称为数字滤波电路,经过峰值提取电路输出的脉冲信号,可能存在因为干扰、噪声带来的杂波脉冲,通过数字滤波电路,剔除这些干扰信号,只保留满足一定宽度的有用信号。门限电路2 的结构如图10 所示,由累加器和门限判决电路两部分组成。累加器的作用是对峰值提取电路输出的N 个相邻的“0”、“1”序列进行累加。门限判决电路将累加器的输出结果与门限2 进行比较,如果大于门限2,则将信号直接进行输出,否则,认为该信号是干扰或噪声信号,将其剔除,输出全“0”。

图10 门限电路2

3 实验测试结果与分析

根据图1 中接收机的结构,使用Verilog HDL语言在Quartus II 环境中完成电路的开发与设计,开发完成后对FPGA 进行编程。最后通过矢量信号源模拟产生不同强度的信号对接收机性能进行测试,通过Signal tap II 对接收机接收处理数据的过程进行在线分析。图11 和图12 分别对应了-20 dBm和-60 dBm 输入信号时的接收机性能。

图11 -20 dBm 时测试结果

图12 -60 dBm 时测试结果

其中,I、Q 是AD9361 输出到FPGA 的两路信号,Amplitude 是求模电路的输出,Gate1 是门限电路1 输出的门限,Peak_value 是峰值提取的峰值信号,Half_out 是半幅度检测的输出结果,Signal 是Half_out 经过门限电路2 进行数字滤波之后的输出结果。图11 对应的是-20 dBm 时的测试结果,可以看出,经过峰值提取电路之后输出的信号Half_out存在一个毛刺干扰,经过门限电路2 之后,毛刺干扰得到抑制。对于传统的单门限检测算法,输出将会是Half_out 对应的信号,而在双门限检测结构的接收机中,经过二次门限判决,抑制了杂波等干扰带来的信号,有效地提取出有用的信号。图12 对应的是-60 dBm 时的测试结果,可以看到,在-60 dBm时,仍能有效接收信号,提取出基带信号。

4 结论

提出了一种双门限检测接收机,并在Altera FPGA 上完成了硬件开发,最后通过矢量信号源产生二次雷达信号,对双门限检测接收机性能进行分析。实验测试结果表明,本文设计的双门限检测结构接收机具有硬件实现简单、动态范围大的特点,可以有效地接收信号,剔除干扰信号,提取有用的基带信号,满足二次雷达接收机的需求,为后期的基带信号处理打下基础。双门限检测接收机的设计方法还可以拓展到其他数字接收机的设计中去。