PSD4235G2可编程逻辑芯片测试与应用

2019-09-11翟莉

翟 莉

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引 言

PSD4235G2 是ST 公司设计生产的一款基于快闪存储器的在线可编程外围器件,可为MCU 提供存储系统。基于在系统编程(ISP)的快闪存储和可编程逻辑技术,给嵌入式设计带来一种简单而灵活的解决方案。PSD4235G2 器件整合了诸多基于单片机的外围功能应用,包括整合优化的宏单元逻辑构架。为了满足嵌入式系统设计的独特要求而被创造的宏单元,能支持系统地址/数据总线和内部PSD4235G2寄存器之间的直接连接,简化了MCU 和其他支持设备之间的通信[1]。利用这些特征,可在实际应用中获得很大程度的便利。因此,有必要对该产品芯片的模块构成及测试特性有所了解。

2 PSD4235G2芯片结构

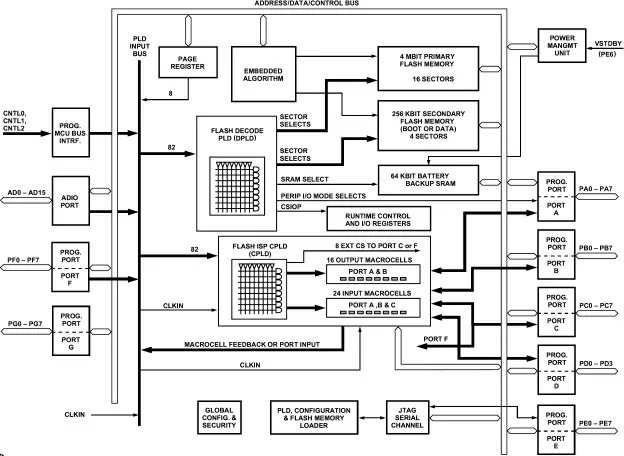

从逻辑结构而言,PSD4235G2芯片包含MCU应用所需要的多个外设功能模块如下:

4Mbit Flash 存储器,地址、数据存储二级Flash,3000 多个Flash 可编程逻辑单元,64kbit SRAM,可重配置I/O 端口和可编程电源管理模块等。

芯片主要性能的发挥,是基于以下配置:

两个闪存记忆存储;

64 千字节的SRAM;

附带有宏单元的可编程逻辑器件(PLD);

附带有52 个输入输出引脚的7 个I/O 接口;

JTAG 端口的在系统编程(ISP);

内部页寄存器;

高可靠的闪存存储。

PSD4235G2芯片整体结构框图如图1 所示。

图1 PSD4235G2 结构框图

3 PSD4235G2芯片测试

由PSD4235G2芯片构成的系统,因其电路规模大,存储容量大,功能复杂,因此在测试精度、速度、测试覆盖率等方面对测试提出了更高更严的要求[2]。芯片测试包括功能测试、直流参数测试和交流参数测试[3-4]。

3.1 功能测试

对PSD4235G2芯片的功能测试可以用两种方法来编程:在系统编程(ISP)和在应用编程(IAP)。表1 显示了哪些编程方法可以编程PSD4235G2 的不同功能块。

表1 不同功能模块的编程方法

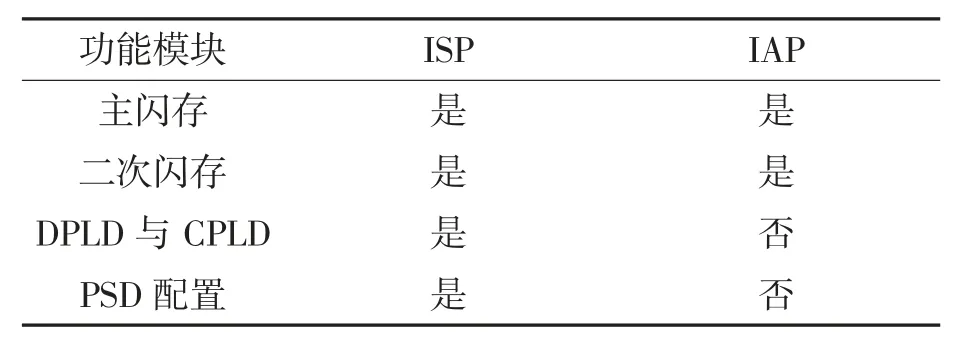

(1)在系统编程

当端口E 使用JTAG 信号时,整个PSD4235G2芯片,包括闪存、PLD、相关配置等,皆可迅速实现ISP。这就意味着,PSD4235G2 能够在任何时间,即使是完全空白的条件下进行编程,MCU 完全不参与。PSD4235G2芯片可通过端口E 的JTAG 信号在PSDsoft 软件开发工具上得到编程支持。图2 给出了软件设计流程图。

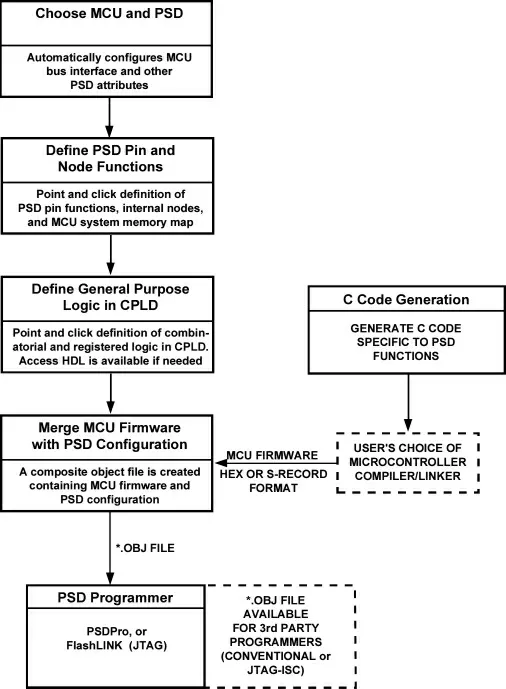

(2)在应用编程

图2 软件设计流程

IAP 可以通过MCU 对芯片编程。MCU 可执行二次闪存或SRAM 中的代码,对主闪存编程,也可擦除和重新编程主闪存。MCU 可以执行在主闪存中的代码对二次闪存进行擦除和编程。Flash 可以由MCU 进行读写操作,也可被擦除和编程。MCU 不能直接写单字节到Flash 中,故此Flash 需要MCU 发送特定指令到特殊地址去实现编程和擦除。一旦MCU 发出指令,它必须检查完成态。PSD4235G2 引用嵌入式算法支持三种方式去提供状态给MCU。检查状态有三种方式:Data Polling、Data Toggle 和Ready/Busy output pin。图3 给出Data Polling 流程图,其余两种方式与此同理可推。

图3 Data Polling 流程图

3.2 直流参数测试

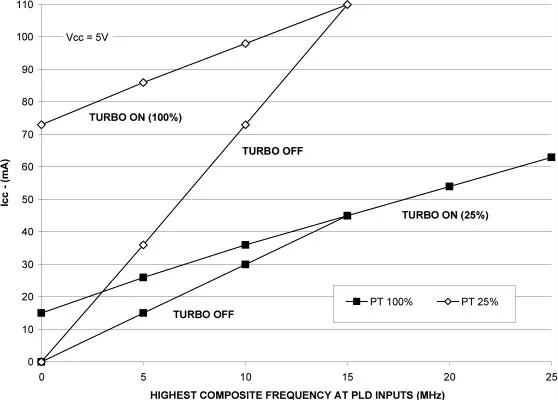

直流参数测试包括输入高、低电平,输出高、低电平,输入漏电流、输出漏电流、电源电流等项。其中电源电流ICC 是PSD4235G2 电路直流参数测试的重点,可以定量地反映器件功耗,以发现器件存在的质量问题。

PSD4235G2 在不同工作模式下其电源功耗是各不相同的。图4 给出了不同频率不同工作模式下的电源功耗。

图4 不同频率不同工作模式下的ICC

3.3 交流参数测试

PSD4235G2 的交流参数测试项目繁多,不仅需要测试各种功能模块的时序,还要对模块下Turbo、Slew Rate、PT Aloc 等多种配置进行全面的时序测试。图5 给出AC 参数测试电路。

图5 AC 测试电路

在对交流参数的测试中,包括以下时序:

- PLD 时序

组合时间;

同步时钟模式;

异步时钟模式;

输入microcell 时间

- MCU 时序

读时序;

写时序;

关机和复位时序

- ISC 时序

在Teradyne 公司的J750HD 集成电路测试系统上编制PSD4235G2 的测试程序,并对样品电路进行了测试。部分测试数据详见图6。

图6 PSD4235G2 部分测试数据

4 PSD4235G2芯片应用

PSD4235G2 将MCU 系统外围器件高度集成在一起,并与MCU 之间实现无缝连接。只需要两颗芯片,MCU 和PSD4235G2 即可代替众多的外围器件组成一套完整的MCU 系统。除此之外,还集成了优化的“微控制器单元”逻辑结构,使系统的地址/数据总线可以与内部寄存器直接互联,简化了控制总线的设计[5-6]。

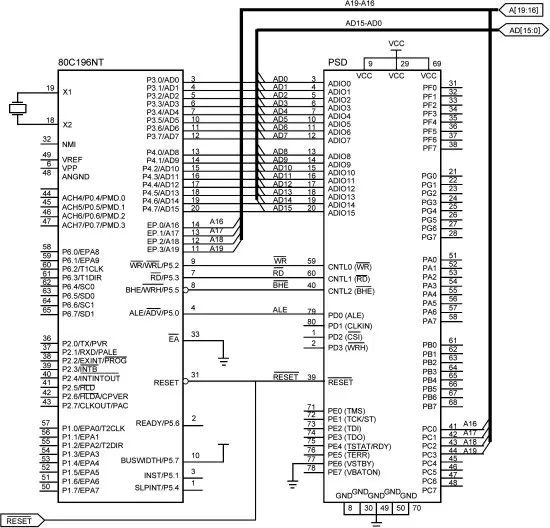

在图7 中展示了一个具有16 位多路复用地址/数据总线的Intel 80C196 MCU 连接到PSD4235G2的应用例子[7-8]。

图7 PSD4235G2 与80C196 连接图

读取Flash(RD, CNTL1)和写入Flash(WR/WRL,CNTL0)的控制信号连接在CNTL 引脚上。当BHE不使用时,PSD4235G2 可以配置为从MCU 接收WRL 并使能高位字节(WRH/DBE, PD3)。较高的地址输入位(A16~A19)可以作为PLD 的输入连接到端口A、B 或C。采用16 位单片机和PSD4235G2芯片构成了一套通用系统,可在实际应用中完成数据采集、控制和编程。

此系统的另一优点是简化了MCU 外围电路的设计,增加了可靠性和稳定性,可以此缩短产品开发周期,降低产品维护和升级成本,有助于产品抢先占领市场。

5 结束语

PSD4235G2芯片独特的结构简化了硬件接口电路,以其设计灵活、资源丰富和极高的性价比在嵌入式系统领域得到广泛应用。通过对实际芯片构成系统的测试,以及对系统的实际应用的分析,加深了对PSD4235 芯片潜力的挖掘,可为该芯片的同类测试和应用研究工作提供经验和借鉴。