一种射频前端数字接收机中的低中频下混频器

2019-09-10梁晓峰叶晖

梁晓峰 叶晖

摘 要:文章对比了射频前端接收机中傳统的低中频数字下混频器结构,提出了另一种数字下混频结构,把传统结构中的抗混叠滤波器和抽取模块用积分梳状滤波器(CIC滤波器)替代,并把积分梳妆滤波器放到下混频器之前,把CIC滤波器的输出信号去和数字本振进行混频,使下混频器的工作频率降低,大大减少了下混频所需的乘法次数,并显著地减小了查找表的大小,有助于节省芯片的硬件资源。

关键词:低中频;下混频;积分梳状滤波器

中图分类号:TN722.3;TN773 文献标识码:A 文章编号:2096-4706(2019)13-0037-04

A Low IF Down-converter in RF Front-end Digital Receiver

LIANG Xiaofeng1,YE Hui2

(1.Guangzhou Zhono Electronic Technology Co.,Ltd.,Guangzhou 510630,China;

2.Guangzhou Letswin Microelectronics Co.,Ltd.,Guangzhou 510663,China)

Abstract:This paper compares the traditional low-IF digital down-converter structure in RF front-end receivers,and proposes another digital down-converter structure. The anti-aliasing filter and decimation module in the traditional structure are replaced by an integral comb filter (CIC filter). The integrated dressing filter is placed before the down-converter,and the output signal of the CIC filter is mixed with the digital local oscillator. It reduces the frequency of the down-converter,greatly reduces the multiplication times required for down-converter,and significantly reduces the size of the lookup table,which helps to save the hardware resources of the chip.

Keywords:low intermediate frequency;down-converter;integral comb filter

0 引 言

软件无线电的概念是由Joseph Mitola等人在1992年的全美远程系统会议上提出的[1],其核心思想就是将数模转换器(ADC/DAC)尽可能地靠近射频天线端,从而将传统上由模拟技术实现的功能尽量搬移至数字域,利用数字电路灵活的可编程特性来实现射频芯片的可重配置功能,同时以数字电路区别于模拟电路的工艺实现方法和低电压工作特点,有效地降低了实现成本和功耗[2,3]。

根据软件无线电的核心思想,可以将射频前端定义为模拟前端(AFE:Analog Front-End)和数字前端(DFE:Digital Front-End),两者之间通过模数/数模转换器(ADC/DAC)连接[3]。数字前端是指位于ADC/DAC和基带处理器之间的数字信号处理电路,其基本功能包括采样率转换、信道滤波、各种补偿校准电路和数字增益控制等。对于低中频接收机,数字前端的基本功能还应包括下混频。

当前主流的射频接收机结构包括超外差接收机、零中频接收机和中频接收机,这几种接收机结构各有优缺点。其中,低中频接收机兼具了零中频接收机和中频接收机的优点,既把射频信号变到接近直流的低频信号,避免了直流成分对信号的影响,又具有零中频接收机集成度高所占面积小的优点。数字中频在低中频接收机中是非常重要的一部分。数字中频具有以下几方面的优点:首先,数字下混频可以坐到绝对正交;第二,利用数字滤波器可以灵活切换选频通道,易于处理多带宽信号;第三,数字电路元件的一致性好,可消除温漂和非线性失真问题。

1 数字下混频器原理

数字下混频与模拟下混频的基本原理是一致的,输入信号与本振信号相乘。在模拟混频器中,有多种因素影响着混频器输出信号的性能,如混频器的非线性和本振的频率稳定度、边带、相位噪声、温度漂移等等。这些在数字下混频中都得以规避,在数字电路的实现中,下混频器的频率、相位等都能得到严格的控制。除此以外,数字下混频器的灵活性远远优于模拟下混频器。传统的数字正交下变频结构[4]如图1所示。

其中数控振荡器NCO的作用是产生正交的正余弦数字本振信号,数字本振信号可以通过即时计算的方法产生,但这将大大增加设计的复杂性,给芯片的面积和功耗也会带来额外地增加。此外,实时计算也会增加数字前端的通道延时,因此数控振荡器NCO是不会采用实时计算的方法的。目前NCO最常见的实现方法就是查表法(LUT),即事先根据各个本振信号的正弦波相位计算对应的正弦值,并按相位角度作为地址存储该相位的正弦值。在系统时钟的控制下,由相位累加器对相位步进不断累加,得到当前相位值,将该值作为取样地址值进行查表获得正弦信号值,输出到数字下混频器进行运算。

输入的I/Q信号在下混频器中分别与NCO产生的數字本振信号相乘,首先获得混频后的I/Q信号。然后经抗混叠滤波器,避免在抽取时候产生频谱混叠。最后对信号进行抽取以降低速率。然而,这种结构下混频器在高速时钟下工作,对数字本振的采样点数将大大增加,导致下混频所需的运算量也随之增加,额外的增加了芯片的面积和功耗。

2 设计方案与实现

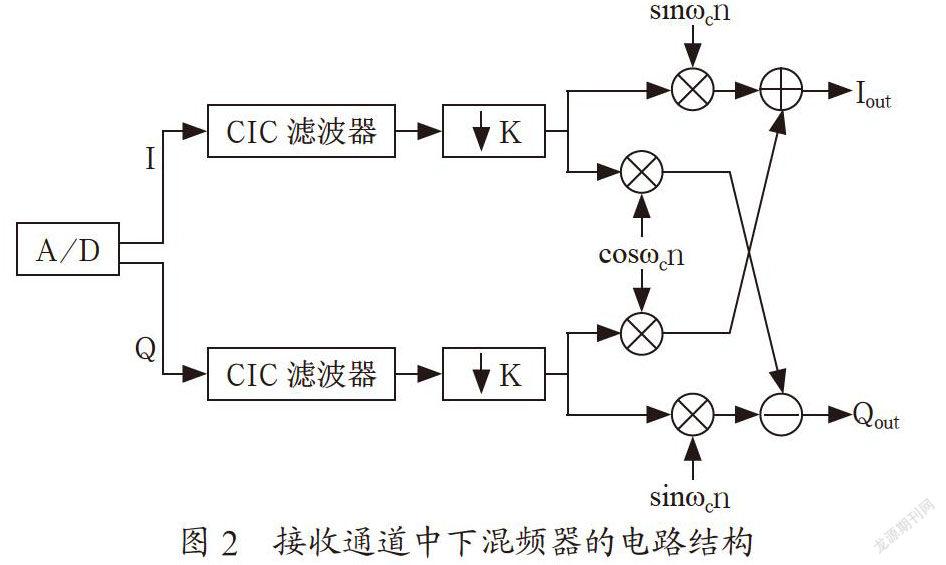

本文根据上述的内容,提出另一种数字下混频结构,抗混叠滤波器和抽取模块用积分梳状滤波器(CIC滤波器)替代,并把积分梳妆滤波器放到下混频器之前,把CIC滤波器的输出信号去和数字本振进行混频,如图2所示。

上述结构用于多信道带宽的设计时,优势尤为突出。根据软件无线电的思想,数字前端的可编程性和可重配置能力十分重要。由于每种信道带宽不会同时工作,基于功耗和面积的综合考量,期望能尽量共享电路模块,因此在设计时还需要考虑电路的兼容性。CIC滤波器在硬件实现上结构简单,无需乘法器,且具备良好的抗混叠特性[5]。另外,CIC滤波器因具备极佳的抽取率可编程特性,非常适用于多种信道带宽并存的通信系统[6]。

对于数字下混频器的结构,本文提出的方案中也进行了修改,如图3所示。

图3中输入的I/Q信号假设为sinα和cosα,两个正弦波发生器分别代表产生两路正交正弦信号的数字本振sinβ和cosβ,应用三角函数运算公式,如式(1)和式(2),则可获得下混频后的差频分量,频率为输入信号频率减去本振信号频率,形式为cos(α-β)和sin(α-β)。

在旧有方法中混频时产生的和频分量则在这种结构中被消去了,最终输出的I/Q信号,则为下混频后的去掉中频的基带信号。

采取上述的方法,下混频器可以对抽取后的信号进行运算,对于抽取率为N的CIC滤波器,下混频器所需的乘法运算只需抽取模块后置时的1/N,对于查找表中所需的数字中频正弦值的储存量也只为旧方法的1/N。

在同一系统中,射频前端与基带之间的接口速率都是约定好的,射频前端中接收信号的频率是根据通信协议所定的。数字下混频器中每个时钟周期进行一次乘法运算,每两次乘法运算之间的本振信号值由其相位步进决定,也即数字本振的相位步进与下混频器的工作时钟相关。因此,只要选择合适的工作时钟、数字中频频率和抽取倍数,使数字中频频率与系统工作时钟为整数的倍数关系,则对于数字中频的正弦本振值就是周期性的。

每个数字中频周期所需的采样点也是周期性的,只需有限的几个采样值即可实现下混频器中数字中频的作用。由此可以简化接收通道中NCO的结构,原本需要通过CORDIC算法计算信号相位,然后再进行查表才能得出的数字中频信号,简化成了固定的几个数值。并由于中频信号的周期与系统工作时钟是整数倍关系,因此每个抽取后的时钟节拍到来时,只需自动选取下一个查找表中的值即可,省略了相位计算的处理。

电路实现中,使输入的I/Q信号与当前对应的数字本振信号分别代入式(1)和式(2)中,就可得到混频后的结果。考虑到正弦波的对称性,查找表中只需存正弦波相位0-的波形数值,即可根据当前相位还原出完整周期的正弦波信号出来。

影响数字下混频器性能的主要因素有两个[7]:一是表示数字本振、输入信号以及混频乘法运算的样本数值的有限字长所引起的误差;二是数字本振相位的分辨率不够而引起数字本振样本数值的近似取值。对于第一个因素,本文提出的方法对数字本振的采样数值进行足够多位宽的量化,可把误差降至极小而不会对混频器性能产生影响。对于第二个因素,本文提出的方法对于数字本振的一个完整周期采取的是整数倍等分采样,所以不存在相位分辨率不够的问题。

3 应用实例

下面将举例说明本文提出的方法对下混频器资源减少的效果。设定数字前端的系统时钟为30.72MHz,接收机中数字中频的频率为160kHz,积分梳状滤波器的抽取率为12。

3.1 对运算量的影响

若采用抽取滤波器放于下混频器之后的传统方法,则下混频器的工作时钟频率也为30.72MHz,在这个时钟频率下,数字中频的一个正弦波周期需要30.72MHz/160kHz=192个采样点,也即需要192次乘法运算才能完成一个周期的下混频。

若采用本文提出的方法,把积分梳妆滤波器放到下混频器之前,经过积分梳状滤波器12倍抽取后的接收信号去参与下混频,则数字中频的一个正弦波周期变成只需要30.72MHz/160kHz/12=16个采样点,即完成一个输入信号周期的下混频只需经16次乘法即可完成,可见下混频所需的运算量极大地减少了。

3.2 对查找表的影响

经过CIC滤波器对信号进行16倍抽取,对于数字中频的正弦波信号来说,每次运算的相位步进为 。因此,完成一个周期的下混频运算需要16个对数字中频波形的采样点的值即可,数字中频的正弦波值可以通过 和 计算得出,其中i=0,1,2…15。如表1所示,经量化后,去掉因符号位或波形形状重复的系数,只有16384、15137、11585、6270、0共5个系数,其中16384即214可通过简单移位运算实现,因此实际需要进行乘法运算的只有15137、11585和6270三个系数。

考虑到正弦和余弦仅在相位上不同,数值实际相同,因此只观察表中正弦波(sin)的数值。从表1可见,经214量化后,一个数字本振正弦波周期的16个系数,前八个和后八个的绝对值是一样的,只是符号不同。数值上不重复的系数实际上只有0、6270、11585、15137和16384五个,其中乘法运算中0可以忽略不计,16384在设计实现中可以通过向左移位运算来实现,因此需要参与乘法运算的系数实际上只有三个。系数中正负符号位的不同,只需在乘法运算后选择加还是减即可,不需要把符号位参与乘法中。

由上述3.1章节可见,对于例子中的下混频器,把0和1的系数考虑在内,若用传统的实现方法共需要用到192次乘法运算,查找表中也需要有192个系数,考虑到对称性,去掉因符号位或波形形状重复的系数,也还是有49个系数。而采用本文提出的实现方法的下混频器,如上文所述,最多只需16次乘法运算,其中只需要用到3个用于乘法的系数,这种实现方式极大地简化了数控振荡器NCO的结构,节省了大量的硬件资源。

4 仿真结果

仿真环境设置如下:输入数字下混频器的接收信号为频率是187kHz的单载波信号,数字中频信号的频率为160kHz。如图4为输入信号的频谱,经抽取率为12的积分梳状滤波器以及下混频器后,转换为27kHz的基带信号,如图5所示。

5 结 论

本文提出一种数字下混频电路结构,用积分梳状滤波器(CIC滤波器)替代传统的抗混叠滤波器和抽取模块,并把积分梳妆滤波器放到下混频器之前,使下混频器的工作频率降低,大大减少了下混频所需的乘法次数,并显著地减小了查找表的大小,有助于节省芯片的硬件资源。

参考文献:

[1] 杨小牛,楼才义,徐建良.软件无线电原理与应用 [M].北京:电子工业出版社,2001.

[2] Tuttlebee W . Software Defined Radio: Enabling Technologies [M].New Jersey:John Wiley & Sons,Ltd.,2002.

[3] Hentschel T,Henker M,Fettweis G. The digital front-end of software radio terminals [J].Personal Communications IEEE,1999,6(4):40-46.

[4] Rupert B. The DSP bottleneck [J].IEEE Communications Magazine,1995,33(5):46-54.

[5] Rajendra V Babar,Manik S Gaikwad,Dnyaneshwar Mantri.CIC filter and FFT implementation to improve power efficiency in Software Defined Radio [C].Wireless Computing and NETWORKING.IEEE,2015:125-128.

[6] Luo,Fa-Long. Digital front-end in wireless communication and broadcasting [M].England:Cambridge University Press,2011.

[7] 孫丹丹,杨莘元,赵大勇.数字下变频器在软件无线电接收机中的应用 [J].信息技术,2002(7):2-4.

作者简介:梁晓峰(1982-),男,汉族,广东广州人,数字IC设计工程师,电子技术工程师,硕士研究生,研究方向:射频/数字集成电路;叶晖(1976-),男,汉族,湖南湘阴人,数字IC设计工程师,电子技术工程师,博士研究生,研究方向:射频/数字集成电路。