三维集成电路中内存的经时击穿分析与检测

2019-08-20贾鼎成王磊磊

贾鼎成,王磊磊,高 薇

(1.上海科技大学 信息科学与技术学院,上海 201210;2.中国科学院 上海微系统与信息技术研究所,上海 200050;3.中国科学院大学 电子电气与通信工程学院,北京 100049)

动态随机存取存储器(Dynamic Random Access Memory,DRAM)作为冯诺依曼架构中的主存储器(即内存),通常与片上系统分离,通过总线与中央处理器进行通信。随着摩尔定律的发展,特征尺寸缩小的过程中,内存易受到金属层中信号线或电源线的耦合噪声、存储电容的电荷泄漏、MOS管器件(Metal-Oxide Semiconductor Field Effect Transistor,MOSFET)或金属线的老化等影响。尤其是在电路处于高偏置电压以及高运行温度的条件下,偏置温度不稳定性(Bias Temperature Instability,BTI)和经时击穿(Time Dependent Dielectric Breakdown,TDDB)是由器件老化导致电路发生故障的潜在威胁。目前,深度学习、云服务和数据挖掘等新兴应用需要大量的算力,使得处理器与内存之间的通信瓶颈成为主要问题,严重制约了计算机系统性能。三维集成电路是一种针对此“内存墙”问题的解决方案,利用三维垂直空间优势来缩短芯片之间的通信距离。然而,在降低通信时延和增加带宽的同时,由于存在严重的热密度以及散热问题,电路可靠性遭遇挑战。文献[1]对三维集成电路中内存的偏置温度不稳定性效应及解决措施进行了分析。静态随机存取存储器中的击穿问题在文献[2-3]中进行了全面的研究。文中将针对三维集成电路中内存的击穿问题展开进一步研究探索。

经时击穿通过击穿MOS管器件的栅氧化层从而影响电路的可靠性,当击穿发生后,电路可能会在运行中立刻出错,也可能在击穿发生之后的一段时间才导致电路产生错误。因此,在击穿发生的初始阶段通过检测电路向存储电路控制系统发出预警信号,成为了笔者关注的重点。文献[4]中提出了基于系统级的经时击穿检测电路,缺乏对电路中击穿的细粒度检测能力以及对制造工艺过程中器件差异性的考虑。文献[5]中针对经时击穿效应的年龄传感器,同样不适用于大规模存储电路集成以及细粒度的电路击穿检测。

笔者主要对经时击穿引入的初次击穿以及后续击穿过程进行了模拟,基于统计学的方法对三维集成电路中内存外围电路的击穿问题展开研究,并针对灵敏放大器结构提出了适用于大规模存储电路集成的细粒度击穿检测电路。

1 模型与问题描述

1.1 三维集成电路模型

图1(a)为一个三维集成电路系统,该系统包含两层芯片,考虑到散热设计的合理性,处理器层被放置在内存层的上方。根据McPAT[6]中多核处理器的芯片结构和面积,顶层由8个集成L2缓存的类SPARC核组成;底层是匹配了处理器面积的内存芯片。硅通孔负责处理器层与内存层之间的互连,散热器覆盖顶层多核处理器。系统总功耗参考McPAT和Micron DDR3 DRAM功率参数表。

图1 三维集成电路结构及热分布图

基于上述三维集成电路结构[1],HotSpot[7]仿真可以得到两层芯片的热分布情况,如图1(b)和图1(c)所示。根据热分布图结果,处理器和内存运行时温度可能达到120 ℃/110 ℃,甚至更高;相比较,在传统二维芯片结构下,内存运行时温度通常只达到55 ℃。文献[8]证实了温度与经时击穿寿命的强相关性。因此,在三维集成电路结构中,电路更易受到可靠性问题的困扰。

1.2 经时击穿模型

摩尔定律的发展,伴随而来的不仅是MOS管尺寸缩小,而且致使生产工艺过程中引入的器件差异性恶化。同时栅极氧化层变薄,增加了其对击穿问题的敏感性。对于超薄氧化层(氧化层厚度Tox< 2 nm),初次氧化物击穿引起的栅极漏电流IG_BD具有很大的差异性[9],并且通常不足以引起电路的故障。随着栅极偏压的持续作用,栅极氧化层内的陷阱密度逐步增加[10],最终导致了栅极漏电流的激增,这表明在氧化层中形成了初次击穿路径。栅极漏电流的激增主要来自于初次击穿和连续击穿(Successive BreakDown,SBD)所引起的氧化层击穿电流。此外,通过氧化层内局部击穿的路径,后续击穿(Progressive BreakDown,PBD)也促使了栅极漏电流的增加。当流经氧化层的栅极漏电流趋于饱和,并最终导致MOS管器件发生短路故障时,称为硬击穿(Hard BreakDown,HBD)。

1.2.1 连续击穿电流模型

为了探究击穿在不同阶段对三维集成电路中内存的影响,需要合适的初始阶段击穿电流模型来模拟电路中器件发生击穿后的现象。因此,引入量子点接触模型[11],初次击穿电流IG_BD可表示为

(1)

其中,e为元电荷的电荷量,h为普朗克常数,V0为两端电极上的电压降,VGS为栅极与源极间偏置电压,Φ为势垒高度,α是与能量势垒形状相关的参数,而β是穿越氧化层和势垒高度的电压降的比值。根据量子点接触与温度相关的模型[12],若晶格受到高温产生应力的影响,原子热运动就会引起势垒高度的振荡;势垒高度Φ与温度T的关系可表示为

Φ(T)=Φ0-γT,

(2)

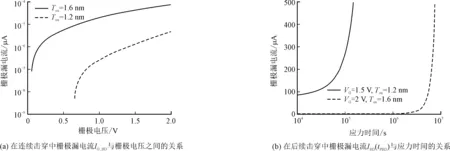

其中,γ是温度系数,Φ0为原始势垒高度。由此,文中分别在氧化层厚度Tox=1.2 nm以及Tox=1.6 nm的两种MOS管配置,且运行温度皆设定为125 ℃的条件下,评估了连续击穿事件中的IG_BD电流,结果如图2(a)所示。其中,Tox=1.2 nm的情况对应内存中灵敏放大器电路,且源、漏端电压皆为0.6V,电路运行偏置电压为VG=1.5 V;Tox=1.6 nm的情况对应局部字线驱动电路,电路运行偏置电压为VG=2 V。

图2 MOS器件在发生经时击穿后栅极漏电流的情况

1.2.2 后续击穿电流模型

为了对击穿的后续阶段进行模拟,文献[3]采用后续击穿与偏置电压、氧化层厚度、初次击穿电流IG_BD以及偏置时间相关联。后续击穿电流IBD(tPBD)可表示为

(3)

图3 SPICE等效击穿模型

其中,tPBD是发生初次击穿后栅极电压继续偏置的时间;GD是时间增长参数,取决于IG_BD发展为设备故障电流IF_BD的时间和缺陷电流增长率。文献[3]中的实验表明,后续击穿模型在45 nm特征尺寸下的参数与实验数据相拟合。图2(b)展示了在偏置电压VG=1.5 V(对应Tox=1.2 nm)以及VG=2 V(Tox=1.6 nm)的两种晶体管的后续击穿电流与时间的关系。

1.2.3 SPICE等效击穿模型

文献[13]中提出的SPICE等效击穿模型采用了电压控制电流源来模拟仿真中发生击穿器件的短路情况,如图3所示。经时击穿的形成机制使得氧化层发生击穿的位置将有很大的差异性,而IBD(tPBD)到MOS管源极和漏极的电流大小,通常与击穿的位置(xBD)密切相关。因此,根据击穿发生的位置,等效击穿模型将IBD分为栅极到源极IGD(VGD)的电流源和栅极到漏极IGS(VGS)的电流源,可表示如下:

(4)

其中,xBD是沟道内从源端到击穿位置的距离,L为等效沟道长度,VGS和VGD分别为栅极到源极和漏极的电势差。通过模拟电路中器件各个击穿阶段的电流以及SPICE等效击穿模型,下节将采用蒙特卡罗仿真的方法对内存中外围电路的经时击穿效应进行统计学分析。

2 内存中外围电路的经时击穿分析

2.1 字线驱动电路

2.1.1 电路结构及功能

在内存的存储阵列[14]中,最小的存储单元由访问控制MOS管和存储电容(1T1C)组成。其中,访问控制NMOS管栅极连接着字线(WL),当某行字线处于高电势时,子阵列中与之相联的所有访问控制NMOS管都会被选通,并将其存储电容中的电荷分享到各自的位线/位线补(BL/BLB)上。全局字线驱动电路负责传递地址的选通信号给不同的子阵列;局部字线驱动电路则负责驱动当子阵列的地址选通信号。当存储电容中的电荷被分享到位线上时,灵敏放大器将负责数据差分放大等工作,子阵列的结构如图4(a)所示。

图4 内存阵列结构与字线驱动电路

内存中不同电路的驱动电压不同[15-16],这造成了氧化层击穿对于不同电路的影响不同。通常DDR3内存的存储阵列电压(Varray)为1.2 V,外围电路的驱动电压(Vperi)为1.5 V,而字线的驱动电压(VWL)高达2 V。其中,外围电路中字线驱动电路在数据的读写操作中,起着重要的存储单元选通作用。只有当数据存储单元被选通后,访问控制才会开启并将存储数据电荷分享到位线上,灵敏放大器捕捉位线/位线补的电势差,并进行差分放大。值得注意的是,存储电容由单个NMOS管进行控制选通,而设计过程中考虑到内存的存储单元的泄漏电流会对存储数据造成可靠性的威胁。因此,通常访问控制管采用的是高阈值NMOS管,以进一步控制漏电流现象。与之相对应,为了在选通阶段充分开启访问控制NMOS管,字线驱动电路必须提供足够高的选通电压(VWL=2 V),这样的设计给字线驱动电路中经时击穿效应留下了隐患。

2.1.2 经时击穿分析

如图4(b)所示,在情况1中,当某地址长时间未选通时,局部字线驱动电路输入端Vin=0 V,中间节点维持在Vperi,输出端Vout=0 V。其中,MP1与MN2长期处于选通电压VWL偏置开启状态,更易诱发氧化层陷阱数量的增加以及击穿路径的生成,造成中间节点和输出端电势的变化。基于SPICE等效击穿模型和蒙特卡罗仿真,对各击穿阶段中字线局部驱动电路进行模拟,得到了基于统计学意义的内存可靠性分析。图5(a)为10 ms时间段内,存储单元中的平均等效电势(μ1)和字线上平均电势(μ2)在不同击穿阶段的状态,同时柱状图中表明了标准差(σ)范围。从结果来看,字线受驱动电路的栅极漏电流累积电荷的影响,电势升高;当位线保持在Varray/2电势情况下,位线将补偿存储单元中部分泄漏的电荷。当字线局部驱动电路发生硬击穿时,无论此地址行是否被选通,字线上的电势都将被上拉,使得该地址一整行存储单元都处于电荷分享状态。此时,此子阵列中该地址行的存储单元将永久失效。

观察图4(c)情况2,当此地址行长时间、高频次地被选通时,局部字线驱动电路输入端Vin=Vhigh,中间节点被下拉到0V,输出端Vout=VWL。其中,MN1与MP2处于电压偏置开启状态,与情况1相反。图5(b)展示了单次选通操作中,存储单元中的平均等效电势(μ1)、字线上平均电势(μ2)以及对应标准差(σ)。结果显示,当未进入硬击穿阶段,选通状态下字线电势低于VWL正常值,但仍能正确激活存储单元。

图5 基于蒙特卡罗仿真对局部字线驱动电路的经时击穿分析

基于上述蒙特卡罗仿真对于局部字线驱动电路的经时击穿分析,由于内存中整个激活操作的周期足够长,且对于激活中单个阶段延迟的差异性不敏感,故局部字线驱动电路在击穿前期导致的电路衰退并不会影响内存正常的读写操作,仅对存储单元中的电荷量造成轻微影响,这是由于受影响字线电势的变化远不足以影响访问控制NMOS管。在HSPICE仿真模拟中,仅考虑击穿致使破坏性的选通错误对于读写操作的影响,结果如图5(c)所示。当发生硬击穿时,存储单元出错以及选通操作失败概率显著提升。

除此之外,图4(a)中全局字线驱动电路控制着整个区域阵列簇中某地址行的选通电压。因此,当字线的全局驱动电路发生击穿时,整行地址都会引入选通错误,直接造成大面积数据读写错误。所幸,由于驱动电路通常由两个反相器组成, 字线的全局驱动电路与局部驱动电路组成了反相器链结构,利用反相器链的信号再生性,在牺牲选通过程中较少延迟性能的条件下,字线的全局驱动电路可以采用较低的选通电压(Varray=1.2 V)或适当增加MOS的氧化层厚度以降低击穿发生的概率。

2.2 灵敏放大器电路

2.2.1 电路结构及功能

内存存储单元中数据的读写操作通常通过三个阶段(预充电、激活和读写)完成[14],灵敏放大器作为读写操作的核心电路,如图7所示。其中,Eq信号控制预充电阶段,SA_N/SA_P端负责激活阶段的电源控制。而MN1/MP1和MN2/MP2组成了交叉耦合反相器,通过识别位线/位线补之间的电势差,从而确定正确的激活方向。例如,在预充电阶段,位线/位线补将被预充电至Varray/2。在激活阶段, 字线上的选通信号将会开启存储单元的MOS控制管,并将存储的电荷分享至位线,抬高位线的电势至Varray/2+ΔVcell。在此过程中,MN1将进一步下拉位线补的电势,从而激活MP2上拉位线的电势。同时MN2与MP1将配合关闭,使位线/位线补趋于稳定。最后,整个灵敏放大器电路会通过I/O外围电路将数据传输至数据总线,并回到预充电阶段。每次读写操作都可视为对存储阵列中的某行地址对应存储数据的电荷恢复,与内存的刷新操作作用相同。当没有激活操作发生时,灵敏放大器将长时间维持预充电状态。其中,灵敏放大器的NMOS宽度为1.33 μm,PMOS宽度为1.9 μm,栅极L=160 nm[15]。

由于灵敏放大器在内存的数据读取和写入过程中起着相当重要的作用,并且在击穿初始阶段就可能造成数据读取错误。因此,分析电路中经时击穿对于灵敏放大器的影响,就显得格外重要。

2.2.2 经时击穿分析

若灵敏放大器的预充电电路中MN3发生了击穿,如图7(a)所示,那么在预充电阶段,Eq信号将无法确保位线/位线补电势相等。根据图中SPICE等效击穿模型,Eq信号上的1.5V高电势将拉升位线上的电势,从而使得位线与位线补在预充电阶段就产生了电势差ΔVTDDB1。从另一方面来看,栅极漏电流也会对电流源Varray/2造成一定程度的影响,然而由于Varray/2的电源引脚直接与外接电源相连[17],故假设在文中影响可以忽略不计。

图6 基于蒙特卡罗仿真对灵敏放大器的经时击穿分析

当灵敏放大器进入激活阶段时,Eq信号下拉至0 V。此时,通过栅极氧化层中的短路路径,位线上的电势将被下拉,使得位线与位线补产生新的电势差ΔVTDDB2,当位线上电荷分享的ΔVcell无法抵消由击穿导致的电势差ΔVTDDB2时,灵敏放大器的差分放大操作将失效,并导致数据误读以及对应的存储数据被破坏。

通过蒙特卡罗仿真对于灵敏放大器在发生击穿的各个阶段进行了模拟,仿真结果如图6所示。在预充电阶段,位线的平均电压(μ)和标准差(σ)与位线补相比随时间增量较大,表明预充电电路失去了平衡位线/位线补的作用,经时击穿效应破坏了内存预充电电路功能,并使得位线/位线补在激活阶段引入不可逆的电势差ΔVTDDB2,致使电路发生可靠性问题。

2.2.3 经时击穿检测电路

通常由于击穿发生后器件的不可逆性损坏,往往简单地将传统芯片废弃。然而,考虑到三维集成电路制造工艺的特殊性以及极高的维护成本,当检测到存储系统中的击穿发生后,将内存中少量存储模块关闭,利用冗余的存储列[15,18]或存储模块转移数据。这需要在击穿导致电路可靠性出错之前,捕捉到击穿前期的现象。由于灵敏放大器工作模式以及电路结构的特殊性,可以通过检测预充电状态下位线/位线补的非法电势差ΔVTDDB1,实现内存存储模块的经时击穿预警。

笔者提出了一种简单有效的检测电路,在牺牲极少空间的基础上,能够在灵敏放大器发生连续击穿和后续击穿的过程中,对尚未影响电路功能的击穿问题进行预警,并将检测信号传递给外围控制电路。通过隔离发生击穿的存储列或局部存储阵列,并将数据转移到冗余存储区域中,在延长三维集成电路中内存使用寿命的同时,降低了后期使用维护的成本。检测电路的布尔逻辑表达式为

(5)

对位线/位线补上的电势(XBL/YBLB)进行采样并协同选通信号Eq_P(ZEq_P)实现经时击穿预警的功能,预警信号为ALARM(FALARM)。为了增加检测电路的精度,需要对预充电阶段位线/位线补上采样的电势信号进行增强,故将式(5)转化为与非式结构,目的在于将反相器链设计加入布尔逻辑中,同时权衡检测电路的复杂度。基于反相器链的信号再生性,三级反相器链对预充电阶段中位线/位线补上的采样信号进行增强,此信号经过三级反相器链后逐渐收敛至稳定信号值,检测电路如图7(a)中虚框所示。其中基于45 nm工艺预测技术模型(PTM),检测电路参考最小尺寸,NMOS管宽度W=90 nm,PMOS管W=155~165 nm,MOS管的长度皆为L=50 nm。同时检测阶段被添加入内存操作中,位于预充电稳定后的时段内,确保剔除非预充电阶段数据和噪声的影响,如图7(b)所示。

考虑到三维集成电路在长时间运行状态下,偏置温度不稳定性老化可能对MOS管阈值电压造成的偏移,以及检测电路对灵敏度和功能可靠性的需求,笔者对检测电路的主要采样部件反相器链进行了老化模拟。基于三维集成电路中内存灵敏放大器电路的老化研究[1],将内存灵敏放大器的访问频率、与激活阶段的占空比以及Long-term BTI模型[19]相结合,可以得到灵敏放大器中交叉耦合反相器的老化情况。其中,由于检测电路的输入端与位线/位线补相连,故交叉耦合反相器的老化模拟可被拓展到检测电路的反相器链中。同时检测电路中用于偏置温度不稳定性老化模拟的温度条件(125 ℃)和应力条件(1.2 V)与上文中灵敏放大器的经时击穿仿真一致,且与文献[1]一致。因此,基于内存灵敏放大器中98%的负载偏差的理论[1],反相器链中互补MOS管的阈值电压将分别偏移35.3 mV和12 mV。最后通过HSPICE对检测电路中反相器链的电压传输特性(Voltage Transfer Characteristics,VTC)曲线进行偏置温度不稳定性老化模拟,仿真结果如图8(a)所示。

图7 灵敏放大器电路中发生的经时击穿效应、检测电路与击穿检测阶段

在反相器链的电压传输特性曲线中,触发阈值(VMx)将影响检测电路的灵敏度与电路功能,只有当VMx略大于Varray/2时,检测电路才能在经时击穿故障发生之前准确预警。基于仿真结果,当反相器链中主要老化部分为PMOS管时,检测电路的触发阈值变小,将会影响检测功能的可靠性;而NMOS管中的偏置温度不稳定性老化,则会增加触发阈值,对检测的灵敏度造成影响。因此,中文通过调整PMOS管宽度来满足合适的触发阈值裕度,一般情况下宽度取值范围为155~165 nm。

基于蒙特卡罗仿真的统计结果如图8(b)所示,当反相器链中PMOS管的宽度较宽时,抗偏置温度不稳定性老化和噪声影响的能力越强;反之,PMOS管宽度越小,检测电路的灵敏度越高,更易受可靠性问题影响。同时灵敏放大器在连续击穿发生后并未出错,随着时间推移,后续击穿增大了栅极漏电流,而检测电路在电路尚未出错时已经对击穿进行了预警。统计结果表明,此检测电路(155 nm ~165 nm)的经时击穿预警将完全覆盖灵敏放大器中数据激活出错的情况。

图8 针对灵敏放大器的经时击穿检测电路中偏置温度不稳定性老化分析及仿真结果

3 结束语

笔者研究了三维集成电路中内存的经时击穿效应,基于蒙特卡罗仿真对内存读写操作中外围电路的可靠性进行了讨论,并针对灵敏放大器电路,提出了适用于大规模存储电路集成的细粒度经时击穿检测电路。根据仿真统计结果,灵敏放大器相比于局部字线驱动电路,更易在后续击穿阶段受到由于击穿引发的电路错误的影响。笔者提出的检测电路的检测概率可以完全覆盖灵敏放大器激活出错的概率,并实现击穿预警功能。同时文中对检测电路中主要采样部件反相器链进行了偏置温度不稳定性老化分析,确定了合适的触发阈值裕度,满足了三维集成电路中内存对击穿检测预警和可靠性的需求。