基于FPGA的主动声呐相控发射信号生成技术

2019-07-26倪东波

倪东波

(第七一五研究所,杭州,310023)

SPWM 是一种调制脉冲的占空比按正弦波规律变化的幅度调制技术,相比常规脉宽调制(PWM)可降低负载电流谐波。该调制信号常作为主动声呐D类功放模块驱动信号,在满足大功率发射同时实现功率可控。常见的 SPWM 信号实现主要有两种方式:采用专用 SPWM信号生成芯片或自然采样法。自然采样法是通过数字或模拟方法产生三角波和正弦波,再对产生的三角波和正弦波通过比较器比较得到SPWM信号。

NCO(Numerically Controlled Oscillator)是一种成熟IP[1],通过设置频率字控制生成不同频率的输出信号,由其产生的正弦波与三角波进行比较,进而产生数字的 SPWM 波形,利用该方法可以灵活生成所需的任意调制比和载波比的SPWM信号。利用大容量的FPGA芯片内置NCO、大容量内存及灵活接口配置,通过单片或多片FPGA级联,可同步产生多达几百个通道幅度、时延可控的SPWM信号,由该信号驱动发射功放,可灵活实现主动声呐相控发射。

1 系统硬件组成

相控发射信号源由1台上位机、1块网络接口模块、8块信号生成模块组成,每个信号源模块可独立生成32通道的相控发射信号,8个模块可同步生成256通道发射信号,组成框图如图1。

图1 相控发射信号源组成及信息流程框图

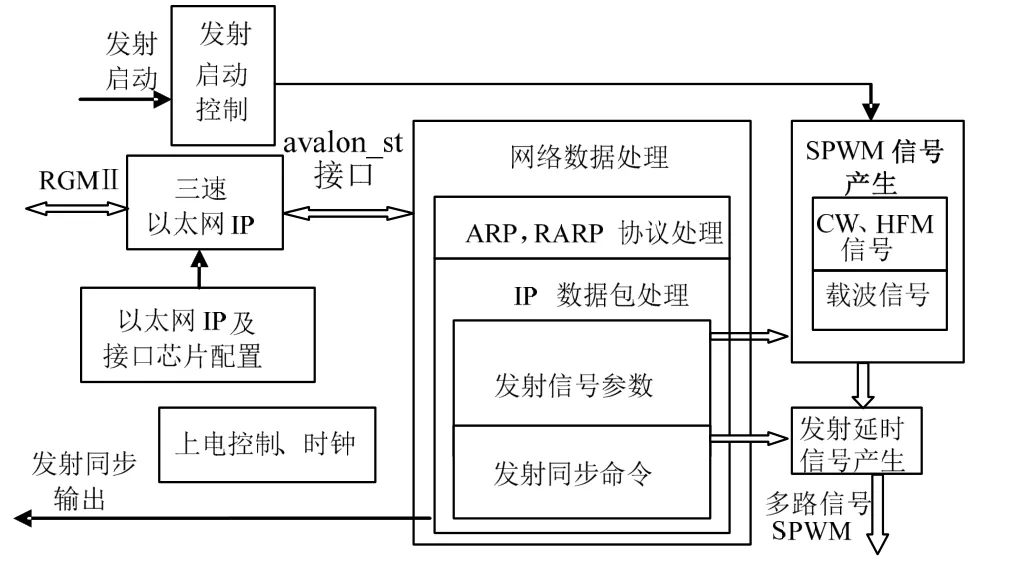

单个信号生成模块的硬件构成框图如图 2,主要工作流程为:信号生成模块通过以太网接收上位机的控制指令,包括各通道发射脉冲信号的频率、脉宽、时延、调制幅度等,实现发射波束控制。为实现通道扩展,板内带有发射同步电路。

图2 SPWM信号生成模块组成框图

2 FPGA片内信号源设计

本设计在 Altera 公司 CycloneⅢ 系列芯片EP3C120F484C7上实现[2],该芯片内部含有 4个PLLs,3 981 312 bit RAM,119 088 个 Logic Elements,内部资源能够满足系统需求。片内包含上电控制和时钟产生、网络接口配置、网络数据处理、发射启动控制、发射同步信号产生、SPWM信号产生、信号延时产生等功能模块部分,信号源生成软件系统框图如图3所示。

图3 发射信号源软件系统框图

发射信号源需产生多个独立时延的单频(CW)和双曲调频脉(Hyperbolic Frequency Modulated,HFM)脉冲信号,以保证定向发射对安装平台纵横摇的修正,实现发射波束稳定和波束俯仰。SPWM信号产生以 NCO为基础,通过即时计算频率字来实时计算需要的参数。根据芯片的资源、设计要求、时序要求,设置NCO相位分辨率为24 bit,采样时钟为 10 MHz,以流水线的方式并行产生多通道SPWM信号。

2.1 SIN信号生成

单频脉冲信号可表示为:

式中,a(t)为调幅信号,f0为工作频率,T为脉宽。

脉宽为T的双曲调频信号可表示为:

对于NCO电路,本设计中频率字由下式确定:

2.2 三角波信号和幅度调制信号生成

由于三角波信号较简单,可以直接用VHDL语言编写[3]。在设计时应处理好起始相位和NCO输出的SIN波同步。幅度调制信号a(t)对脉冲信号进行幅度包络调制,根据需要可设置为钟型、 cos2θ型等,以最简单的线性为幅度调制为例,量化后:

式中,Tx为调制结束时间,A为输出功率调制参数。SPWM信号产生框图见图4。用Signal TapII采集的NCO模块SIN和三角波信号数据流数据见图5。用SignalTapII采集SPWM信号数据波形见图6。

图4 频率幅度时延可控SPWM信号生成框图

图5 用SignalTapII采集的SIN和三角波信号数据流(采样率200 MHz)

图6 SPWM信号波形(采样率200 MHz)

2.3 SPWM信号时延处理

用DSP或CPU实时生成多通道相控发射信号时,数据读写速度是制约其信号生成能力的主要因素。为了实现多通道高精度时延,一般采用提高处理芯片时钟频率或提高存储器容量的方法。而FPGA逻辑电路具有并行处理能力,合理安排运算时钟,充分发挥其内部高速时钟和流水线并行处理功能,在多通道信号生成中有独特优势。

SPWM时延电路功能模块见图7所示。其中接口电路完成参数读写和时钟分配,采用分时独立运行的“wr、wr_addr”和“rd、rd_addr”信号生成电路。数据存储器长度由设计中的最大延时需求来决定,如SPWM信号采样率为10 MHz,在最大延时不超过200 μs时,存储器长度可取为2 048。当收到有效的 SPWM 信号时,将其按顺序循环写入数据存储器,根据预先设置的延时参数,延时启动数据读操作,从数据存储器中读取 SPWM 信号。每个数据存储区可用于生成4个或8个 SPWM信号,扩展通道数主要受片内存储器容量制约。

数据存储器“读/写”控制“读/写地址”数据流见图8。图9中显示部分多通道延时输出信号细节,设置各通道间的延时间隔1 μs, Signal TapII采样时钟为200 MHz,及每个采样点间隔为5 ns,其中CH3和CH15输出与设置值偏差20个采样点(0.1 μs),其他均与设置值一致。SPWM输出信号延时偏差不大于0.1 μs。

图7 SPWM信号时延电路实现

图8 读/写控制及地址数据流

图9 多通道延时输出信号(采样率200 MHz)

3 SPWM信号生成验证

图10(a)显示了生成的单周期频率为8 kHz、载波为60 kHz的双极性SPWM信号,图10(b)显示了脉宽4 ms前后沿进行线性幅度调制后的SPWM信号驱动功放,在换能器输出端观察信号。图11(a)显示生成的单频8 kHz、脉宽100 ms的SPWM信号进行FFT分析结果,其幅度调制为1;图11(b)信号幅度调制为0.71,其驱动信号幅度衰减约3 dB。图12显示中心频率为8 kHz、带宽为2 kHz、脉宽100 ms的SPWM信号进行FFT分析结果,图12(a)、图12(b)的幅度调制分别为1、0.1,下图幅度衰减约10 dB。

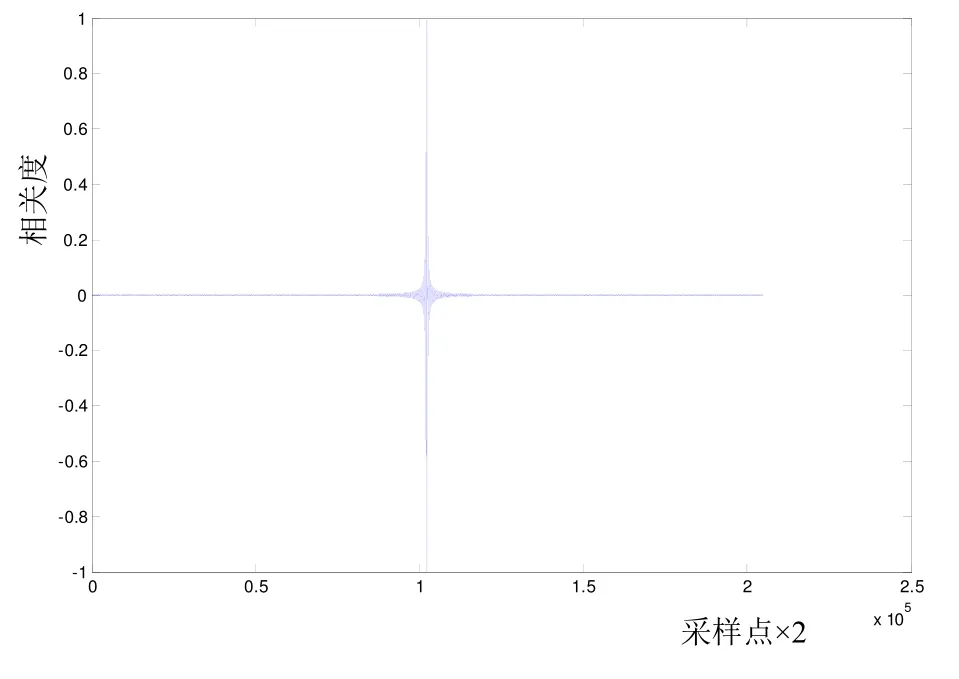

利用采样率为102.4 kHz的CoCo80信号采集仪对中心频率为4.0 kHz、脉宽1 s、HFM带宽1 kHz的 SPWM 信号进行数据采集和相关性分析,测得与理论设计参考信号的相关性达到99.2%,结果见图13。图中横轴为采样点数量的2倍值。

图10 (a) 8 kHz 双极性4 ms脉宽SPWM信号

图10 (b )8 kHz 双极性4 ms脉宽功放输出信号

图11 (a) 调制度为1单频8 kHz脉冲信号谱图

图11 (b) 调制度为0.71单频8 kHz脉冲信号谱图

图12 (a ) HFM 7~9 kHz脉宽100 ms调制度1的谱图

图12 (b) HFM 7~9 kHz脉宽100 ms调制度0.1的谱图

图13 脉宽1 s采样信号带通滤波后互相关分析

4 结束语

本文提出了一种基于单片 FPGA的多通道SPWM信号产生方法,通过分时独立控制信号数据读写实现的多通道信号时延精度可达0.1μs,并进行硬件和软件开发,对生成信号进行测试分析和与理论比对,验证结果满足理论设计要求。通过信号生成模块的同步级联,可方便实现几百通道的独立时延 SPWM信号生成,具有集成度高、接口灵活、适装性好等特点,可广泛用于主动声呐多通道相控阵发射信号源生成。