基于Quartus Ⅱ的数字逻辑电路功能设计

2019-07-20范舒颜

范舒颜

(南京工业大学,南京 210000)

在学生参与硬件实验操作过程中,一般借助实验箱连线这一方式,完成对电路功能的测试及验证[1]。但是由于存在学生实验中的误操作,以及线路连接错误所致损坏芯片等多种情况,再加上传统实验的过于枯燥单一,导致无法提高学生的实验分析及功能设计能力。QuartusII作为综合性CPLD/FPGA软件,能够实现VHDL、原理图以及AHDL和VerilogHDL不同输入形式,且基于设计输入至配置硬件完成完整的PLD设计流程[2]。对此本次研究探索基于QuartusII的数字逻辑电路功能设计。

1 QuartusII软件简述

QuartusII作为综合性CPLD/FPGA软件,由Altera公司研发生成,采用了层次结构法实现对电路描述,提供了电路功能设计结构无关的集成开发环境,并具备了电路仿真的完备工具,包括功能仿真及时序逻辑仿真[3]。且具备了全部数字逻辑电路功能设计这一特性,在设计数字逻辑电路功能过程中,主要包括五大组成:新建工程项目、完成对文件源程序的编辑、对综合设计文件的编辑、模拟仿真以及元件符号生成。QuartusII作为综合性CPLD/FPGA软件,在运用过程中极为简便,除了无法支持少数实验此外,几乎可以对所有数字逻辑电路实验支持[4]。因此在展开对数字逻辑电路功能设计实验研究中,可以直接运用QuartusII,依据其电路原理输入功能及仿真实验功能,完成对数字逻辑电路的功能仿真。因此本次研究提出基于QuartusII的数字逻辑电路功能设计,可以改变传统电路设计实验的单一,满足对数字逻辑电路功能设计的仿真验证需求。

2 功能设计方法

2.1 模型分析

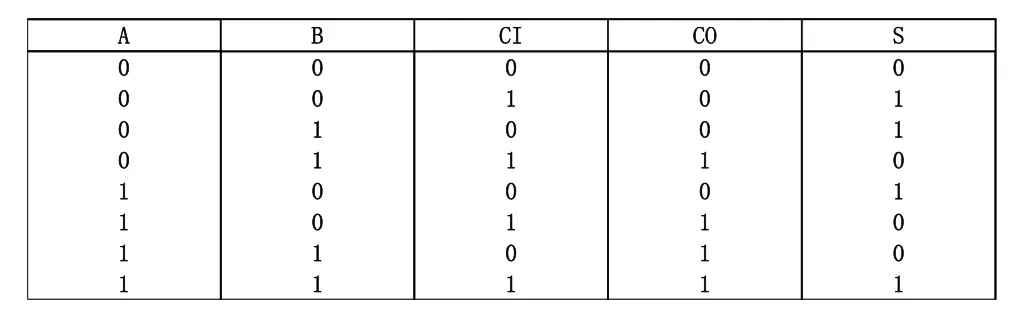

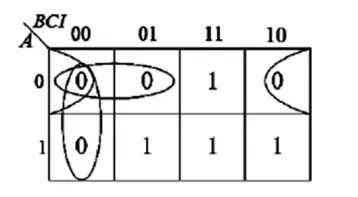

全加器作为对一位二进制总和完成计算的电路,包含了多种不同的设计方法,本文采用最为简单的逻辑表达式完成,对全加器独立元件符号的表达,用于四位串行加法器设计。为了进一步提升全加器设计便捷性,结合(见表1)全加器的真值表,画出本次研究的输出本位、S及高位进位 卡诺图(见图1、2)。

表1 全加器真值表

图1 本位及卡诺图

图2 想高位进位卡诺图

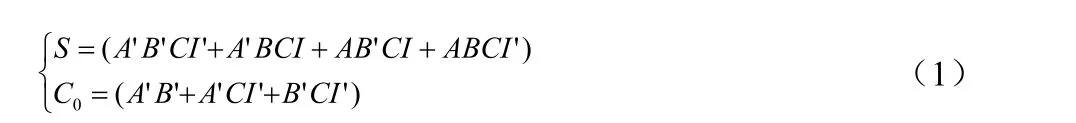

根据上图可以得出全加器的输出端最简表达式,以及非逻辑表达式如下:

2.2 仿真设计

通过为本次数字逻辑电路功能设计,构建工作库专用文件夹,在文件夹中新建一个未完成的工程项目,对该工程项目拓展名设置为“.bdf”文件。本文根据如上部分分析所得的全加器的输出端最简表达式,以及非逻辑表达式,参照公式(1)具体要求,完成逻辑电路单元模块的逐一输入,具体包括非门模块、两输入与门模块、三输入与门模块、三输入或非门模块、四输入或非门模块,针对不同模块借助信号线完成彼此连接之后,即可得到原理模型图设计。之后借助QuartusII编译器统一完成,检查本次逻辑电路功能设计的逻辑是否一致及是否完整。经过综合逻辑之后仿真测试所输入的原理图,对该原理是否达到电路功能的设计需求加以验证,仿真图(见图3)。

图3 仿真波形示意图

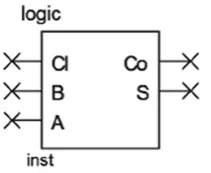

通过对最终仿真结果分析发现电路功能设计逻辑无误,封装本次设计电路生成元件符号,以便能够基于原理图编辑器实现功能设计过程中有效调用。经过封装生成的元件符号(见图4)。之后借助元件符号完成对串行四位加法器的设计,验证本次设计的基于QuartusII编译器的数字逻辑电路功能设计,最终得出的输出波形图(见图5)。证实QuartusII软件设计,能够达到较好的设计性能,且仿真结果符合预期,具备较强的可移植性,减少了资源占用量。不仅如此还有效提升了数字逻辑电路功能设计的整体质量及灵活性,对设计进程及效率有效加快。

图4 封装生成的元件符号

图5 仿真输出波形图

3 结束语

在本次研究中通过探索基于QuartusII的数字逻辑电路功能设计。利用QuartusII原理图及硬件描述语言VHDL,仿真设计本次研究的数字逻辑电路功能,仿真结果证实QuartusII软件设计,能够达到较好的设计性能,且仿真结果符合预期,具备较强的可移植性,减少了资源占用量。不仅如此还有效提升了数字逻辑电路功能设计的整体质量及灵活性,对设计进程及效率有效加快。