基于FPGA的无线充电接收芯片验证平台的设计

2019-07-16刘彬彬

刘彬彬

摘要:本文以一款基于dw8051的无线充电接收芯片为例,阐述了搭建FPGA原型验证平台的几个步骤,以及设计验证过程中的出现一些问题的分析及解决。

[关键词]SoCFPGA原型验证验证方法学

随着IC设计技术的发展,目前芯片的设计已进入到Soc的时代。Soc就是将微处理器,数字IP,模拟IP,各类存储器及胶合逻辑集成在单一芯片上。随着设计规模及复杂度的提升,成功设计一款芯片的时间和成本也成倍的增加,因此,如何在保证功能的情况下,缩短时间减低成本成了我们关注的焦点。随着FPGA日趋成熟的工艺技术,不断降低的功耗和成本,以及不断增强的规模和速度,使得其在原型验证有着不可替代的地位。用FPGA作为原型验证硬件模块的载体,有两方面的优势:一方面是FPGA是逻辑器件,仿真的速度比软件仿真速度快,另一方面,硬件的物理特性跟实际芯片比较接近,有利于我们比较真实的评估验证。利用FPGA搭建的验证平台,通过模块级和系统级的验证,能快速的缩短开发时间,降低开发成本,提高流片的成功率。

本文通过一款以dw8051处理器为核心的无线充电接收芯片,阐述了如何构建和验证FPGA原型验证的软硬件平台,包括硬件资源的整合,IP替换,测试仿真,综合实现及软硬件联调等。

1基于dw8051无线充电接收芯片的设计

本文所述的是一款应用于无线充电接收系统,满足WPCQi标准的无线接收芯片,该芯片采用MCS-51系列精简指令集处理器dw8051作为微控制器。DW8051是由Synopsys提供的可综合的微控制器IP核。它兼容标准的8051,但为了便于集成,采用了新的外部接口。DW8051除了使用loop进行精准延迟的设计外,兼容大部分的标准51软件。

基于dw8051的无线接收芯片架构如图1所示,包括了数字部分和模拟部分,数字部分除了dw8051和SFR总线外,还包括了接口单元,定时器模块,I2C总线,串口uart,复位及看门狗单元等多个模块,模拟单元包括fsk解调,ask调制,12位的ADC,LDO,PLL,基准源及驱动mos等,除了这些数字模拟模块还有RAM及flash等。

2FPGA原型验证软硬件平台的设计

近年来随着集成电路工艺技术的发展,芯片规模越来越大,应用在RTL代码验证的时间,及软件开发验证时间越来越多,这都需要借助FPGA原型模拟芯片的行为,来帮助硬件开发和软件开发者来提高效率,相对于软件仿真,FPGA硬件结构更接近于真实地芯片,更能有效真实地配合软件开发,有效真实地反映存在的问题,提高芯片的正确性。但是由于FPGA及ASIC两者结构的不同,在做FPGA对应ASIC的验证时,还需要进行相应的修改,才能完成对应的功能验证。

本文主要就从硬件及软件两个方面进行描述。硬件方面主要包括了,FPGA的选型,开发板的购买,ASIC代码转换装入FPGA,调试启用FPGA原型。软件方面包括了,软件程序准备,软件载入FPGA协同運行。

2.1FPGA选型

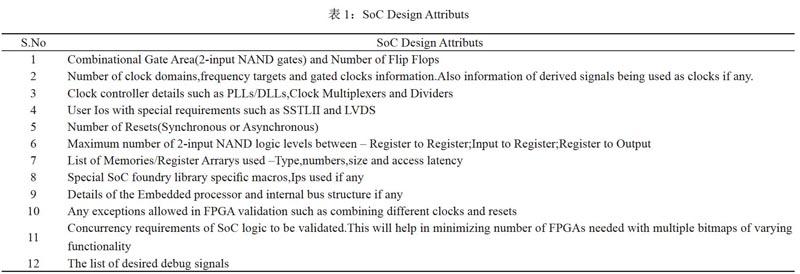

FPGA选型需要根据ASIC设计的实际需求进行,如表1所示,ASIC设计通常包括以下一些内容:

(1)容量:包括了纯逻辑容量,存储容量,dsp单元容量等。

(2)内置IP:包括时钟IP,存储控制器IP,cpu等。

(3)接口:普通的IO接口及专用的高速接口如PCIE,LVDS接口等。

(4)速度:资源占用率在50%左右时的速度,一般被用来评估原型。

针对以上内容进行分析,其中纯逻辑容量,即ASIC中组合电路与触发器的容量,直接替换成FPGA的逻辑资源。需要内置存储单元,比如单双端口的ram,rom,ffo等来对asic中的存储IP进行替换。需要有dsp器件来替换asic中的乘加运算。还需要一些内置的IP,比如分频模块PLL,时钟模块MMCM等,对于接口的要求,一般FPGA足够多的I0口都能满足要求,除非一些特定的专用口。影响速度的因素较多,包括设计规划,代码风格,资源情况等等,这些可以再选择一款容量足够的FPGA后,经过代码替换,编译综合后得到一个大概的数据,根据这个数据再来选择速度更合适的FPGA。综上所述,根据以上的限定信息来进行FPGA的选型。

2.2FPGA原型板选择

本课题的原型验证硬件平台结构如图2所示,该验证平台的主芯片采用altera公司高性价比FPGA:cycloneII系列EP2C8Q208C8N,此芯片资源丰富,价格适中,非常适合中小型芯片验证,板载EPCS16N串行配置芯片,同时支持jtag和as模式;系统的工作时钟由50M的有源晶振提供,IO口3.3V电压由电源管理芯片1085提供,FPGA的1.2V的内核电压由1117稳压芯片提供,板子预留有足够的IO口,可以通过扩展IO,将验证板与子板相连,进行系统级的验证。本课题采用的是主板加子板的验证模式,主板是FPGA原型板,子板是AD采集及mos驱动管子等分立元件搭建的板子,尽量使搭建的FPGA原型验证平台跟真实芯片一致。

2.3ASIC代码转换

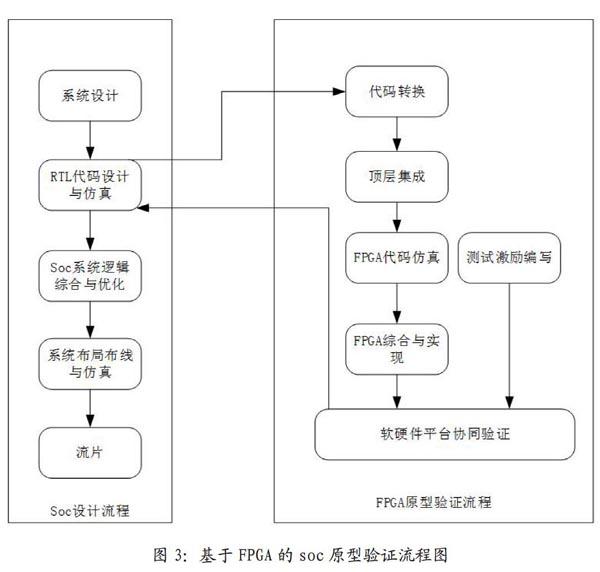

FPGA原型验证的关键是尽可能的使FPGA模拟真实芯片的功能,尽可能的接近真实的芯片,但在实际的使用过程中,由于FPGA与ASIC自身工艺及结构的不同,以及一些规模,速度,功耗上的限制,使得在使用FPGA作为芯片原型验证时,需要对ASIC的源代码进行一些修改,替换才能完成对应的功能。整个验证流程如图3所示的,本文只对右边FPGA原型验证流程进行分析。

2.3.1存储单元的替换

在本设计中使用的两个ram一个用来运行程序,一个用来存储数据,都需要转换成FPGA内部同样大小的RAMIP核,本设计中使用了一个rom存储单元用来存储BootLoader的程序,同样在验证的过程中需要换成同样大小的ROMIP核。

2.3.2时钟单元的处理

时钟门控clockgating一般在ASIC中广泛使用,一般会在clk模块中例化成由latch与门组成的门控单元,对某个模块进行时钟控制。这些门控单元,如果直接在FPGA中例化为相同逻辑的latch与门,逻辑功能是没有问题的。但是这时与门出来的受控时钟,则不能再FPGA的专用时钟网络中走线,而是走普通的信号网络,这样FPGA能达到的频率很差。为了纠正这样情况,可以把对寄存器的门控,放在寄存器端,也就是选用FPGA中行如FDCE这样带门控的寄存器。

2.3.3模拟单元的替换

FPGA原型验证只能验证数字部分,模拟部分的功能只能通过外部器件,分立元件来实现,本系统中的ASK,FSK,AD,LDO等模拟模块都是通过一个子板连接到验证主板上的,而整个系统的电源,复位,时钟等,也是由主板提供的。其中内核电压,IO电压,存储单元的电压由验证板电压转换电路提供,而时钟则有板上的晶振通过PLL模块转换提供。

2.3.4其他数字IP的替换

如果使用到一些计算的乘法器,除法器,乘加运算等,还需要一些其他的IP来替换。

2.4代码的ModelSim仿真

由于对代码进行了替换,为了保证验证的等效性,以及便于验证出差检查,需先对转换后的代码进行仿真验证,再进行原型板的调试验证。本设计使用Mentor公司的ModelSim仿真工具进行仿真,modelsim提供了友好的界面,可以很方面的观察仿真波形信号,并且modelsim可以通过运行脚本文件,方便仿真。Modelsim还提供了仿真覆盖率的功能,能够标识此测试激励仿真验证了哪些模块。这些功能有助于提高代码功能验证的覆盖率。

为了验证代码替换的正确性,对一些相应的模块进行仿真测试。本设计中有对RAM,ROM核进行替换,为了验证这两个模块及对这两个模块操作运行模块是否正确,设计了一个激励,该激励通过运行8051处理器的程序,来仿真验证8051对RAM,ROM的数据存储是否正确。仿真结果可以通过ModelSim查看仿真波形。图4所示RAM模块的仿真波形。图5所示是mcu加载的程序实际的数据。从图4可看出,运行程序时,从RAM中读出的mcu程序的数据跟图5显示的程序数据是一致的,通过ModelSim仿真不仅可以验证代码替换是否等效,功能是否正确,还可以检查出一些基本得语法错误。

2.5原型板的调试

在完成modelsim的仿真后,就可以将编译综合后的文件加载到FPGA中,进行原型板的调试。原型板的调试主要一下几个步骤:确认下原型板电压电流是否正确是否稳定;确认下输入时钟的频率,相位,偏移,分频是否正确;确认下FPGA的配置及复位系统是否正确;确认编译综合文件是否能加载到FPGA中。3FPGA的原型验证的实现

在原型板调试完成后,验证的基本平台已搭建完成,可以对芯片进行系统完整的验证。

本文描述的验证工作主要包括两部分,一部分是针对芯片内部各个模块的功能验证,即模块级的验证,另一部分是结合软件,运行整个mcu系统,进行完整功能的验证,即系统级的验证。

3.1模块级验证

模块级的验证一方面调试时间短,查找问题容易,针对性强,另一方面,分工明确,便于多人合作,效率高。模块级验证主要根据功能要求编写测试激励,通过modelsim仿真,及板子调试,示波器查看等手段来验证。本设计的测试激励主要有两种方式,一种是直接通过verilog描述语言编写,一种是通过c语言编写软件程序,加载到mcu中,运行meu进行测试。在进行验证时,根据具体的模块选择适合的方式来进行验证,所有的验证结果都可以通过modelsim观测到。图6所示为测试uart模块时modelsim捕获的波形。将串口0接到串口1上,从串口0定时发送数据0xaa,0xa9,0xa8,0xa7,从仿真图6可以看出在串口1上接收到了同样的数据:0xaa,0xa9,0xa8,0xa7。

3.2系统级验证

完成模块级的验证后,就可以进行系统级的验证。整个系统的验证需要软硬件协调验证,包括软件的编写,程序的下载,整个系统的运行,系统功能的实现,系统级的验证包括了大部分的模块,以及模块之间的通讯。系统级的验证能够验证出模块级没有验证出的问题,比如模块之间通讯出错,模块之间运行的冲突等等。

本文仅以接收芯片的下载系统原型验证为例,通过keil软件编写一个串口代码,功能为:固定向pc端发送0xaa的数据,编写完代码,编译生成.hex的文件,将文件存储到RAMIP核中,经过FPGA进行编译综合实现,通过jtag下载到板子上。此时整个验证环境就搭建好了。此时如果打开串口调试助手,可以看到一直接受到数据0xaa,现在通过keil软件编写一个不同功能的串口代码,看功能是否切换过来,新的串口功能为:将串口从pc端接收到的数据再通过串口发送回pc端,编写完代码,编译生成.hex的文件。如图7所示,打开上位机,将程序通过上位机软件下载到meu里面,可以看到下载成功,此时通过PC端的串口调试助手发送数据:676869123456,可以看到串口調试助手也接收到了同样的数据676869123456。

4结论

文中以验证基于dw8051无线充电接收芯片为例,详细的介绍了如何FPGA软硬件验证平台的设计,包括了FPGA的选型,原型板的选择,ASIC代码的转换,modelsim的仿真,原型板的调试及原型的验证。在验证的过程中,先从硬件模块的原型验证到模块级的验证,最后到系统级的验证,保证原型验证具有较高的覆盖率,提高整个平台的可靠性。应用FPGA原型验证的方法既可以验证功能提高流片的成功率,又能缩短开发周期。

参考文献

[1]张跃玲,张磊,汪健等.FPGA的验证平台及有效的SoC验证方法[J].单片机与嵌入式系统应用,201616(03):8-11.

[2]冯凌霄,张冰,基于FPGA的SoC原型验证方法研究[J].电子设计工程,2014,22(16):44-47.

[3]李维汉,赵韩,张坤,江昊,电动汽车无线充电系统的分析与设计[J].昆明理工大学学报(自然科学版),2015,40(06):66-70.

[4]胡江浩,张中炜。基于QI协议的无线充电通信系统[J].中国新通信,2016(03):106-106.

[5]邓良禹。手机无线充电技术的研究[J].移动信息,2017(09):7-8.

[6]苏艺端,虞致国,顾晓峰。一种基于可重用激励发生机制的SoC验证平台[J].计算机工程与科学,2016(07):1309-1315.

[7]程冀胜.SoC芯片FPGA原型的软硬件协同验证[J].单片机与嵌入式系统应用,2017(11):7-13.

[8]李璐,周春良,冯曦,周芝梅,朱承治.基于DPI-C接口的可扩展SOC验证平台[J].电子设计工程,2018(04):136-140.

[9]虞致国,魏敬和,基于FPGA的ARMSoC原型验证平台设计[J].电子与封装,2007,7(05):25-28.

[10]丰玉田,付字卓,赵峰,大规模SoC设计中的高校FPGA验证技术的研究与实现[J].电子技术应用,2006(02):110-112.

[11]夏飞,刘光明,基于FPGA组的ASIC验证原型系统和逻辑分割算法的研究与实现[J].计算机工程与科学,2006,28(09):83-87.

[12]Thomas L, Anderson.Design intents raise verification level [M].Electronic Engineering Times, 2001.

[13]孙海平,丁健,系统芯片(SoC)验证方法与技术[M].北京:电子工业出版社,2005.

[14]虞致国,魏敬和,基于JTAG的SoC软硬件协同验证平台设计[J].微电子学与计算机,2010(10):166-168..

[15]張术利,刘忻,基于FPGA的SoC原型验证的设计与实现[J].电子技术,2011(05):71-73.

[16]杨安生,黄世震,基于ARMSoC的FPGA原型验证[J].电子器件,2011,34(03):247-251.