一种超宽带频率综合器设计与实现

2019-07-08胡佳旺李文杰张贵福杨玉彬

胡佳旺 李文杰 张贵福 杨玉彬

摘 要: 介绍频率综合器指标要求,在比较频率合成常用方法的基础上描述一种具有三通道输出的小步进超宽带频率综合器实现构架,推导和分析关键设计参数表达式,计算理论性能指标,给出各个通道的详细实现方案。基于国产器件完成样机设计和测试。测试结果表明该频率综合器具有超宽带频率输出、低相位噪声、低杂散、低谐波、细步进输出等特点,满足指标要求。

关键词: 超宽带频率综合器; 样机设计; 实现方案; 频率合成方法; 指标分析; 参数推导

中图分类号: TN02?34 文献标识码: A 文章编号: 1004?373X(2019)13?0152?04

Design and implementation of an UWB frequency synthesizer

HU Jiawang, LI Wenjie, ZHANG Guifu, YANG Yubin

(Institute of Electronic Engineering, China Academy of Engineering Physics, Mianyang 621900, China)

Abstract: The indicator requirements of the frequency synthesizer are introduced. On the basis of the common methods of frequency synthesis, the framework of a small stepping UWB frequency synthesizer with three output channels is described. The expressions of the key design parameters are deduced and analyzed, and theoretical performance index is calculated. The detail implementation scheme of each channel is given. The prototype design and test were completed, which relyed on the domestic devices. The test results show that the frequency synthesizer has UWB frequency output, low phase noise, low stray, low harmonic, small stepping output, etc, which meet the indicator requirement.

Keywords: UWB frequency synthesizer; prototype design; implementation scheme; frequency synthetic method; index analysis; parameter derivation

0 引 言

頻率综合器在现代雷达、通信和导航等领域被广泛应用,是射频与微波系统的关键部件,是影响电子系统性能的关键因素之一。低相位噪声、低杂散、细步进、高稳定度、捷变频已成为频率合成器发展的主要趋势。频率合成的基本方法主要有:直接频率合成、间接频率合成、数字频率合成三种。本文综合采用以上三种基本方法实现了一款基于国产器件的超宽带频率综合器。

1 指标及总体方案

1.1 主要技术指标

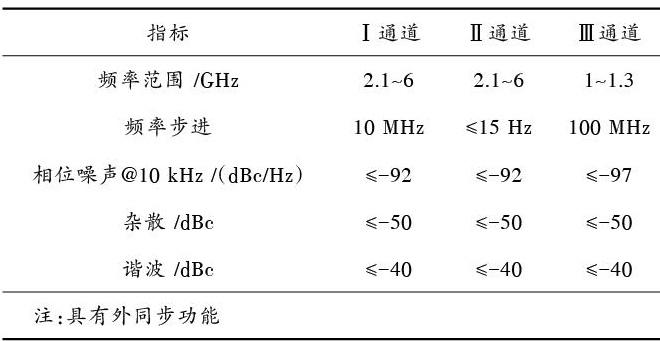

该频率综合器需要对外输出三种跳频信号,并具有外同步功能,其三种输出信号的指标要求如表1所示。

1.2 总体构架

直接频率合成通过对基准频率混频、倍频、分频等运算得到一系列频点输出,该方法主要用于产生固定数目较少的频率输出,其体积和功耗较大,输出相位噪声一般可接近理论极限值;间接频率合成则是利用锁相技术实现频率合成,其输出频率宽频点多,频率步进一般较直接合成小但比数字频率合成大,其结构简单,相噪较直接合成差;数字频率合成输出频率分辨率最高,转换时间快,适用于生成各种波形的信号,但其输出频率较低。

表1 指标要求

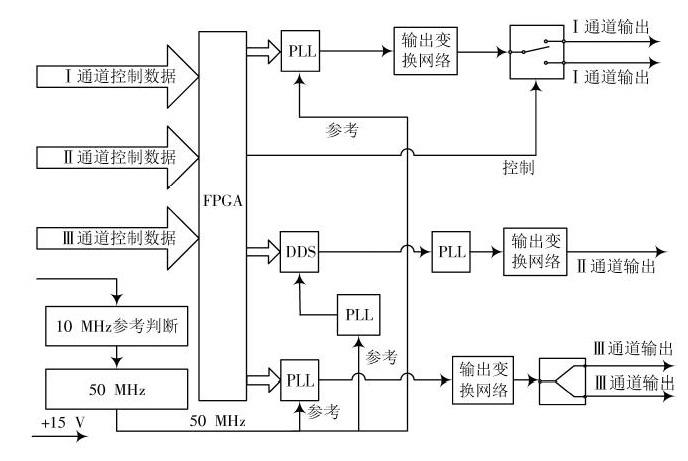

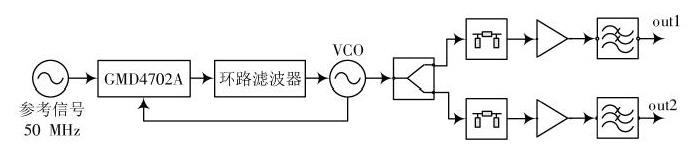

基于以上三种合成基本方法,结合指标要求,频率合成器采用以下构架实现:中控部分收到系统输入串行频率控制数据后,将各个通道放置到相应的频率。I通道采用间接合成锁相技术输出3~6 GHz频率范围的信号,再采用直接合成中的分频方式实现2.1~6 GHz全频率范围信号覆盖;Ⅱ通道采用数字频率合成DDS做参考,通过锁相由VCO输出3~6 GHz信号,再分频实现2.1~6 GHz频率覆盖和小步进频率要求;Ⅲ通道以50 MHz为参考,直接采用间接频率合成的锁相方式实现1~1.3 GHz频率覆盖。总体架构框图如图1所示。

图1 总体构架框图

2 设计实现及指标分析

2.1 Ⅰ通道设计及指标分析

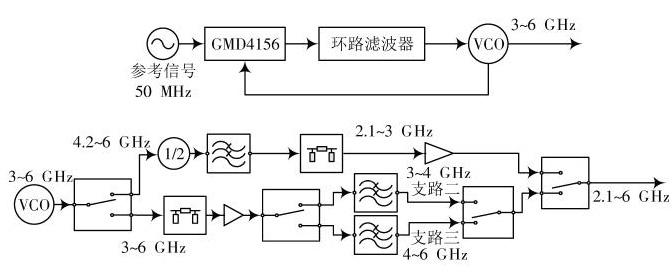

I通道输出为最小频率步进10 MHz,鉴相器选用成都振芯公司的产品[1]GMD4156。VCO选择中电十三所超宽带产品,输出频率为3~6 GHz,对应调谐电压1.5~18 V,故采用有源四阶环路滤波器。

忽略环路滤波器噪声,根据锁相环相位模型[2?3]可得锁相源输出相位噪声为:

图2 Ⅰ通道实现简图

支路一对VCO信号进行二分频,然后滤波放大,这样锁相环输出4~6 GHz频段时,Ⅰ通道可以获得2.1~3 GHz频段输出,支路二和支路三采用分段滤波方式,获得低谐波的4~6 GHz和3~4 GHz两个频段输出。某一支路进行工作时对其他支路的电源进行相应控制,既可以节约功耗又能控制其他支路产生不必要的杂散和谐波。输出变换网络中的器件全部采用国产器件。

2.2 Ⅱ通道设计及指标分析

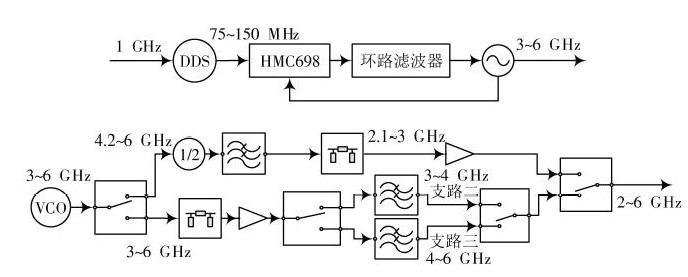

Ⅱ通道输出频率范围与Ⅰ通道一致,但其输出步进有10 MHz大步进要求也有10 Hz级别的小步进要求,用单个鉴相器通过改变分频比难以实现。因此,Ⅱ通道采用DDS输出做参考,再通过锁相环的倍频作用实现。DDS芯片采用中电58所的JDDS9910[4],该DDS芯片工作时钟可达1 GHz,输出最小分辨率为0.23 Hz,近端杂散可达-80 dBc以上。由于此处使用的是DDS做参考,其相噪较晶振差,为控制最终输出信号相噪,满足高鉴相频率要求,减少控制线,此处采用低噪底的高鉴相频率的HMC698直接置位鉴相器,该芯片归一化噪底可达-233 dBc/Hz,鉴相频率高达1 300 MHz。

根据DDS时钟和频率调节字位数,可得工作在1 GHz时钟下JDDS9910输出的频率分辨率为:

Ⅱ通道输出频率范围和谐波要求与Ⅰ通道一致,故VCO输出后需级联与Ⅰ通道一致的变换网络,这里不再赘述。Ⅱ通道实现简图如图3所示。

图3 Ⅱ通道实现简图

由于锁相环等效窄带滤波器,因此此处只需关注DDS近端杂散。根据JDDS9910说明书,该芯片输出窄带(输出频率±500 kHz)杂散典型值为-87 dBc,由它作参考,根据倍频关系,计算锁相环输出杂散指标在DDS杂散基础上的恶化量为:

2.3 Ⅲ通道设计及指标分析

根据指标要求,Ⅲ通道功分两路输出1~1.3 GHz信号,步进100 MHz,选择成都振芯国产鉴相器芯片GMD4702A[7],Ⅲ通道实现方案如图4所示。

图4 Ⅲ通道实现简图

在VCO輸出端,两路信号进行衰减、放大、滤波处理。

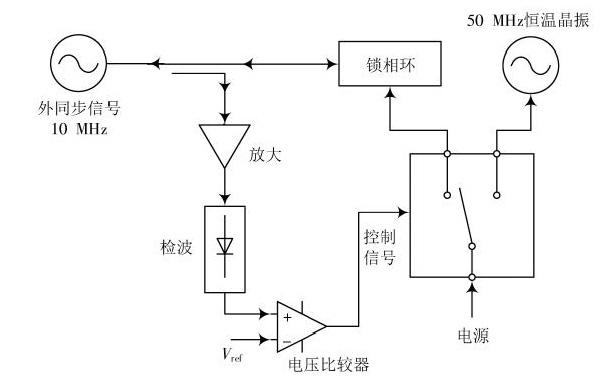

2.4 电源及同步功能设计

频率源要求电源纹波低,供电一般采用LDO以减小低频纹波并需对开关电源的频率进行合理设置。系统提供的15 V电源需要变换为24 V,12 V,5 V,1.8 V,3.3 V等电压,主要采用LYM8025[8]及SW1764[9]等国产器件实现。同步功能采用图5方案实现。外同步10 MHz信号经检波后与门限电压比较并输出控制信号,当有外同步信号时,启动同步锁相环,并关断晶振电源;当无外同步信号时,关断同步锁相环,打开50 MHz恒温晶振电源。该晶振选用中电13所频率稳定度为0.02 ppm的OXLN254系列产品。

图5 外同步实现原理

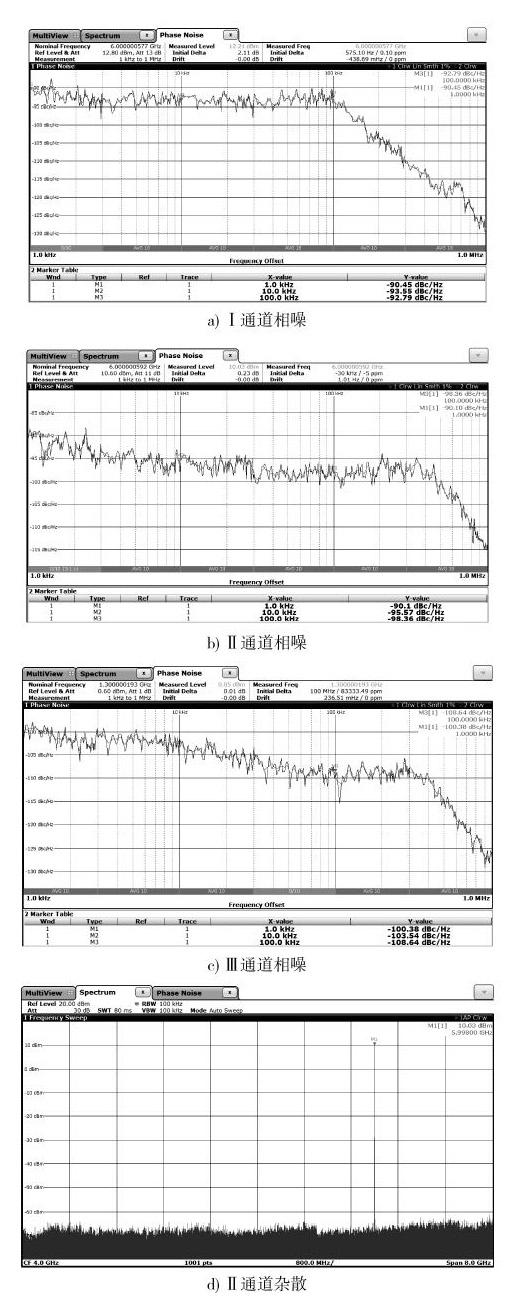

3 测试结果

采用上述设计方案,基于国产器件完成该超宽带频率综合器样机,经测试该频综输出电性能信号指标均达到或优于指标要求,指标与计算结果一致性较好,其Ⅰ,Ⅱ,Ⅲ通道输出相噪噪声分别达到了-93 dBc/Hz@ 10 kHz,-95 dBc/Hz@10 kHz和-103 dBc/Hz@10 kHz。关键指标测试结果如图6所示。

图6 关键指标测试结果

4 結 语

本文在分析基本频率合成方法的基础上综合采用三种频率合成方法,基于国产器件实现了一款超宽带频率综合器,并对关键指标进行分析、推导和计算。样机测试结果表明,该频率综合器具有超宽带、细步进、低相噪、低杂散、低谐波等特点,符合指标要求。

参考文献

[1] 成都振芯公司.振芯科技产品手册[Z].成都:成都振芯科技,2017.

Chengdu Corpro technology Co., Ltd. Corpro product manual[Z]. Chengdu: Chengdu Corpro technology Co., Ltd, 2017.

[2] 白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1995.

BAI Juxian. Low noise frequency synthesis[M]. Xian: Xian Jiaotong University Press, 1995.

[3] 方立军,徐光争,马骏.低相噪数字锁相间接频率合成器的研究[J].现代雷达,2000(5):77?82.

FANG Lijun, XU Guangzheng, MA Jun. Research on low phase noise digital phase?locked indirect frequency synthesizer[J]. Modern radar, 2000(5): 77?82.

[4] 中电58所.JDDS9910说明书[Z].无锡:中电58所,2017.

CETC 58. JDDS9910 product manual [Z]. Wuxi: CETC 58, 2017.

[5] 陈翘.宽带频率源的研制[D].南京:东南大学,2015.

CHEN Qiao. Development of a Broadband Frequency Source System [D]. Nanjing: Southeast University, 2015.

[6] 王家礼,孙璐.频率合成技术[M].西安:西安电子科技大学出版社,2000.

WANG Jiali, SUN Lu. Frequency synthesis technology [M]. Xian: Xidian University Press, 2000.

[7] 成都振芯公司.GMD4702A数据手册[Z].成都:成都振芯科技,2017.

Chengdu Corpro technology Co., Ltd. GMD4702A datasheet [Z]. Chengdu: Chengdu Corpro technology Co., Ltd , 2017.

[8] 中电24所.集成电路产品手册[Z].重庆:中电24所,2018.

CETC 24. Integrated circuit product mannual [Z]. Wuxi: CETC 24, 2017

[9] 济南半导体元件实验所.厚膜混合集成电路及微电路模块产品手册[Z].济南:济南半导体元件实验所,2017.

Jinan semiconductor research institute. Thick film hybrid integrated circuit and micro circuit module product manual [Z]. Jinan: Jinan Semiconductor Research Institute, 2017.

[10] 中国电子科技集团公司第十三研究所.集成晶体振荡器产品手册[Z].石家庄:中电13所,2017.

CETC 13. Integrated crystal oscillator product manual [Z]. Shijiazhuang: CETC 13,2017.

[11] 郑继禹,张厥盛,万心平,等.锁相技术[M].西安:西安电子科技大学出版社,1994.

ZHENG Jiyu, ZHANG Juesheng, WANG Xinping, et al. Phase lock technology [M]. Xian:Xidian University Press, 1994.

[12] 邓贤进,李家胤,张健.C频段频率合成器设计[J].电讯技术,2006(3):20?23.

DENG Xianjin, LI Jiayin, ZHANG Jian. Design of C?band frequency synthesizers [J]. Telecommunication engineering, 2006(3): 20?23.

[13] VADIM Manassewitsch.频率合成器原理与设计[M].3版.北京:电子工业出版社,2008.

VADIM Manassewitsch. Frequency synthesizers: theory and design(third edition) [M]. Beijing: Publishing House of Electronics Industry, 2008.