印制电路板去耦电容摆放位置分析

2019-07-08宋晓锋

宋晓锋

(上海市可扩展计算与系统重点实验室(上海交通大学),上海 200240)

李德恒

(高效能服务器与存储技术国家重点实验室(浪潮电子信息产业股份有限公司),山东 济南 250101)

0 引言

开关电源为服务器和存储电路板设计中的常用电路,为了降低电路中电源噪声,在用电芯片端会加入去耦电容。理想情况下,去耦电容要尽量靠近芯片放置,且要与芯片用电PIN放在同一层面,以保证去耦效果。随着芯片引脚设计越来越密集,信号走线越来越多,放置去耦电容的空间越来越有限。如何在有限的空间里,找出合理的去耦电容放置位置,变得尤为重要。

1 电容去耦理论

1.1 电容去耦原理

电容去耦的原理,可以从两方面来解释[1],储能的角度和阻抗的角度。从储能的观点来看,当负载需要瞬间的一个大电流时,开关电源无法满足瞬间的电流需求,这时负载电压就会有一个跌落,而如果电路中加有电容,电容储存的电荷则可以在此时快速供给负载芯片,从而避免了负载电压大的波动。从阻抗的角度来说,从负载芯片端看,将开关电源模块及其电容等效为一个阻抗值Z,其计算公式见公式(1),要保证负载电流变化时负载电压的波动在允许的范围内,就要设计合理的阻抗Z,一般情况下,Z的数值越小越好。

1.2 PCB寄生电感

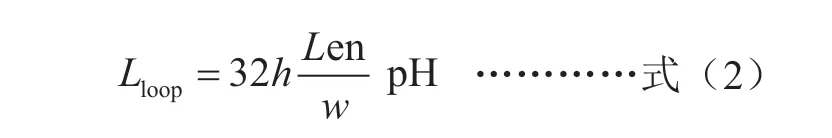

一般寄生电感的计算为单纯的平面或导体寄生电感,但是对于PCB来说,电源平面附近总有地平面存在,其电感的计算为电源与地的回路电感,根据[2]可知,其计算公式为式(2)。

其中,Lloop表示回路电感,h表示电源面与地的距离(单位为mil),Len和w分别表示平面长度和宽度(单位为in)。

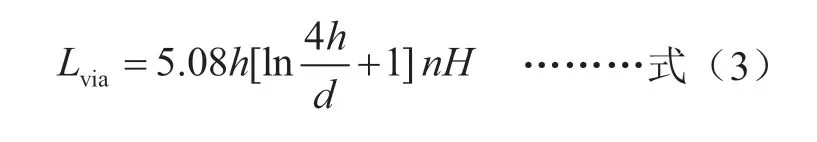

1.3 过孔寄生电感

去耦电容的焊盘附近都会有过孔的存在,过孔也存在寄生电感,其会减弱去耦电容的作用,根据[3]可知,过孔寄生电感的计算公式为式(3)。

其中,Lvia为过孔寄生电感,h为过孔长度,d为过孔直径,单位为in。

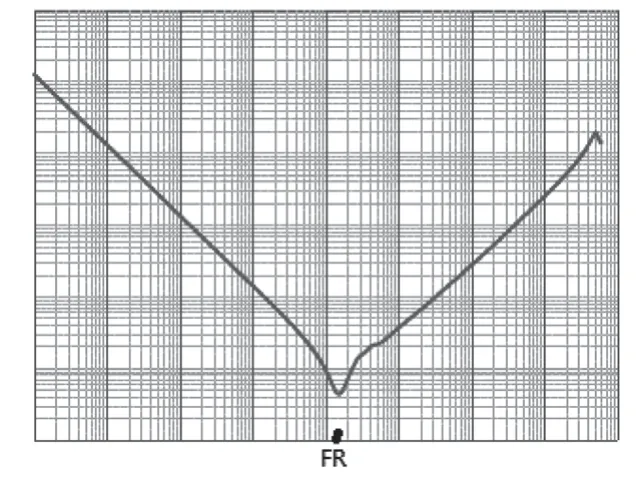

1.4 电容等效模型

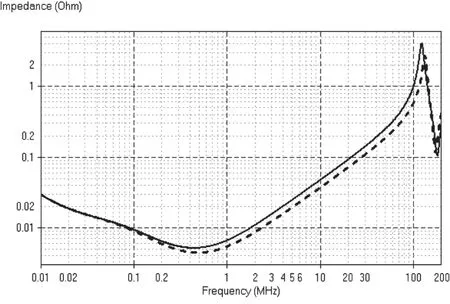

电容的模型可以用S参数,高阶等效模型,RLC等效模型等形式,在实际的应该中经常使用由串联等效电阻ESR、串联等效电感ESL、电容组成的RLC模型。根据RLC模型画出电容的阻抗曲线(如图1)。

图1 电容阻抗曲线

从图中可知,在谐振频率之前,电容表现为容性;在谐振频率之后,电容表现为感性。也就是说它的阻抗随着频率的增加先减小后增大,等效阻抗的最小值发生在串联谐振频率时,这时电容的容抗和感抗相互抵消,表现为阻抗大小恰好等于寄生串联电阻ESR。在实际应用中,我们选择电容的时候要尽量选择低ESR、尽量小的ESL的电容。

实际设计过程中,电容看到的电感不仅仅包含自身的寄生电感,还包含PCB寄生电感、过孔的寄生电感等,实际分析电容的去耦效果时,以上寄生电感都要予以考虑。

2 去耦电容摆放位置分析

1.1 设计方案1分析

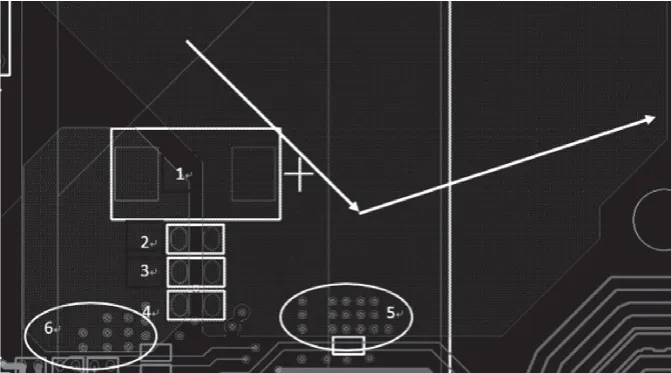

如图2所示为Layout设计方案1,其中箭头所示为电源传输路径的方向,1、2、3、4为去耦电容,5为电容的电源孔,6为电容的地孔。因负载芯片端没有足够的空间放置电容,所以去耦电容1、2、3、4放到了传输路径的中间位置,并遵循传统设计规则,电容都放在了与芯片相同的层面TOP层。因此处高速线密集,只有在5和6的位置有打过孔的空间。

图2 Layout设计方案1

根据公式(2),计算电容1的PCB寄生电感(包含电源和地电感两部分)约为0.14 nH,电容2的PCB寄生电感约为0.112 nH。

2.2 设计方案2分析

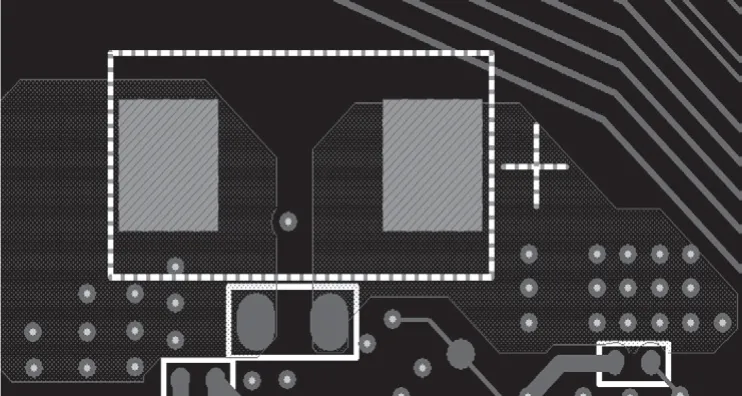

设计方案2如图3所示,其将电容1和2放到了距离过孔更近的BOT层,电容3和4的位置不变。对电容1和2来说,因其距离过孔位置更近,其PCB寄生电感将会相应减小,但是因电容位置BOT层,也会带来额外的过孔寄生电感。

根据公式(2),计算电容1的PCB寄生电感约为0.09 nH,电容2的PCB寄生电感约为0.06 nH。

根据公式(3),电源过孔簇5带来的寄生电感约为0.013 nH,地过孔簇6带来的寄生电感约为0.017 nH。

总体来看,方案2的寄生电感小于方案1,方案2的去耦设计会带来更好的去耦效果。

图3 Layout设计方案2

3 仿真验证

为了验证上述的理论分析的正确性,对方案1与方案2的设计进行仿真分析,其仿真结果如图4所示。其中实线为方案1的阻抗曲线,虚线为方案2的阻抗曲线。可以看到虚线所示的阻抗小于实线所示阻抗,且其主要区别位于寄生电感作用区域,从而验证了以上理论分析的正确性和优化方案2的设计可行性。

4 结语

对开关电源设计过程中,PCB空间有限情况下去耦电容的摆放位置进行理论分析,并进行仿真验证。结果表明,在无法保证去耦电容都拥有过孔的情况下,将去耦电容分别放置于TOP和BOT层将比传统的将电容放置于芯片同层TOP层,具有更小的寄生电感,从而具有更好的去耦效果。

图4 方案1与方案2阻抗比较分析