基于FPGA的UART的设计实现

2019-06-15罗春梅肖顺文王涌

罗春梅 肖顺文 王涌

摘要:本设计采用Verilog_HDL语言设计实现UART系统。该系统由波特率时钟生成模块、数据发送模块和数据接收模块等三个模块组成。经Modelsim模拟仿真显示,各模块设计均满足要求,数据传输速率高、数据传输准确。

关键词:FPGA;UART;异步串行通信;Modelsim仿真

中图分类号:TN92 文献标识码:A 文章编号:1007-9416(2019)03-0150-02

0 引言

通用异步收发传输器UART(Universal Asynchronous Receiver and Transmitter)使用非常广泛,只需一根数据传输线和几根信号线就可以完成计算机与外部设备的通信,并且支持全双工通信,节约了传输成本[1]。本文采用Verilog_HDL语言设计实现UART,这种接口比专用的UART器件更加简单、资源利用率更高,能够完成数据的发送和接收。

1 异步串行通信原理

异步串行通信是以字符为单位进行传输的,传输时,严格按照UART帧格式来进行传输。UART数据帧格式包含1位起始位、数据位(可以设置为5~8位)、1位奇偶校验位(可有可无)、停止位(可以设置为1、1.5或2位)[2]。发送方就是按照此顺序一位一位的来进行发送,再通过数据传输线逐次被接收方接收。UART数据帧格式如图1所示。

由于异步通信两端的时钟不同,所以设置起始位和停止位可以保证发送和接收同步。本系统采用1位起始位、8位数据位、1位停止位的帧格式,即一帧数据共有10位。

2 UART系统设计

本系统基于FPGA实现UART系统,包括三个主模块:波特率生成模块、数据发送模块和数据接收模块。

2.1 波特率时钟生成模块

波特率是指每秒传送的字节数,是收发双方共同约定的系统传输速率。本系统的系统时钟设为50M,对系统时钟进行分频就可以生成想要的波特率时钟[3]。为了能从外部来修改波特率,设置了一個波特率选择端口,设置该端口的值就可以选择自己想要的波特率,它的原理其实就是设置了一个数据选择器,端口取不同值时,使得分频系数取不同值,由此便改变了波特率。端口取各值时,对应波特率为:00对应9600HZ;01对应19200HZ;10对应38400HZ;11对应115200HZ。

2.2 数据发送模块

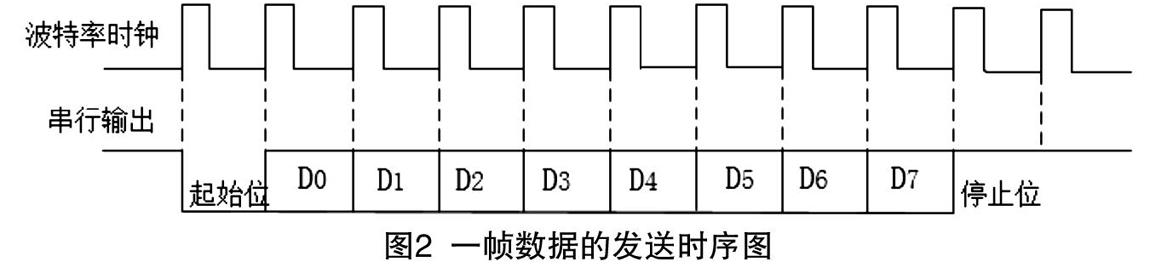

该模块的采样时钟即为波特率时钟,假设波特率设置为115200HZ,系统时钟是50M,则分频系数[4],完成一帧数据的发送,需要10个波特率时钟周期,即为。则一帧数据就需要11个波特率脉冲来进行传输,第11个时钟到来就意味着一帧数据发送完成。一帧数据的发送时序图如图2所示。

从图2中可以看出,波特率时钟到来之前,数据线一直置“1”,在时钟的第一个上升沿到来时,开始发送第一位即起始位“0”,之后的每一个时钟上升沿就发送一位,而特别需要注意的是,数据位的发送是由低到高依次发送。

2.3 数据接收模块

数据接收过程中,在对传输线上的数据进行采样时,通常将每一位的中间时刻视作是最稳定的,所以中间点的采样电平就被认为是该位的电平。然而在数据接收时,有可能发生外部干扰促使电平反转的情况,所以只采样一次是不准确的[4]。为了解决这个问题,对每一位数据都设置了六次采样,根据这六次采样结果来判断该位的电平状态,将出现次数较多的采样电平当作该位的真实电平,若是两者一样多,则视为数据不可靠,不执行任何操作[5]。一位数据的接收原理图如图3所示。

从图3中,把一位数据分成了16小段,在6个中间时刻对其进行采样,图中的①②③④⑤⑥即为六个采样时刻。根据这种采样方式可知,实际采样频率应该是16倍的波特率。其中,要特别注意起始位的判断,因为有时候干扰信号也会使得下降沿出现。在数据线上有下降沿出现时,假设它就是起始位,接着在六个中间时刻对它进行采样,若是6次采样结果中,低电平出现的次数比较多,那么它就是真正的起始位,否则,它就不是起始位,应当继续等待真正的起始位。

3 UART系统仿真测试及分析

编写测试脚本后,在Modelsim中分别对发送模块和接收模块进行仿真测试,测试结果如图4、图5所示。

从图4中可以看出,在复位信号置高及发送使能信号有效时,开始发送数据,此时,uart由空闲状态转换为发送状态,在一帧数据发送完毕后,uart又重新回到空闲状态,同时输出一个时钟周期高电平的发送结束信号。根据异步串行通信原理可知,待发送的八位并行数据为10111010时,数据线上的传输数据应当依次为0(起始位)、0、1、0、1、1、1、0、1、1(停止位)。与上图进行对比后发现,每隔一个波特率时钟便输出一位数据,输出的数据为0010111011[6]。并且此时波特率选择端口值为11,说明波特率设置为115200HZ,发送一帧数据应该为86806ns,用光标进行测量,测量数据正确。这说明发送模块设计正确,能够满足要求。

从图5可以看出,复位电平置高且串行输入有下降沿出现时,开始接收数据,在一帧数据接收完毕后,同时输出接收结束信号。根据异步串行通信原理可知,在串行数据为0010101011时,它的数据位是01010101,则接收模块收到的8位并行数据应该是10101010。与上图进行对比后发现,接收模块输出的并行数据正是10101010。这说明接收模块设计正确,能够满足要求。

4 结语

本系统采用Verilog_HDL硬件描述语言来实现通用异步收发器。根据功能需求,分别对UART的三个主模块进行了设计。最终的仿真测试结果显示,该设计完全满足要求,能够很好的进行数据的发送和接收。该设计简单便捷,实用性高。

参考文献

[1] 吳厚航.深入浅出玩转 FPGA[M].北京:北京航空航天大学出版社,2010.

[2] 杨宗国,李艳萍.基于FPGA的UART模块的设计[J].现代电子技术,2009(2):19-22.

[3] 贾亮,冀源.基于FPGA的串口通信控制器设计[J].微型机与应用,2016,35(22):33-35.

[4] 夏宇闻.Verilog 数字系统设计教程(第三版)[M].北京:北京航空航天大学出版社,2013.

[5] 袁玉卓,曾凯锋,梅雪松.FPGA自学笔记-设计与验证[M].北京:北京航空航天大学出版社,2017.

[6] 谢谢.基于FPGA的UART设计[J].电子设计工程,2016,20(16):51-53.

Design and Implementation of UART Based on FPGA

LUO Chun-Mei,XIAO Shun-Wen,WANG Yong

(School of Electronic and Information Engineering,China West Normal University,Nanchong Sichuan 637009)

Abstract:This design uses Verilog_HDL language to achieve UART system. The system consists of three modules: the baud rate clock generation module, data sending module and data receiving module. Modelsim simulation shows that the design of each module complies with the requirements, with high data transmission rate and accurate data transmission.

Key words:FPGA;UART;Asynchronous serial communication;Modelsim simulation