基于码密度的高精度时间数字转换器设计*

2019-04-30张青松徐光辉

张青松,徐光辉,李 娜

(陆军工程大学 研究生院,江苏 南京 210007)

0 引 言

对时间精度测量的要求广泛存在于通信工程、激光测距、医学成像、科学计量等实际应用中[1-3]。目前,时间数字转换器(Time-to-digital Converter,TDC)是时间精准测量的一种基本方法,它通过将表示时间间隔的模拟信号转换为数字信号这一途径,实现对时间间隔的精确测量[4]。

由于时间测量技术自身高度依赖于所在系统的参考时钟的特点,也就必然导致其测量分辨率由系统时钟所限制。随着分辨率的提高,无可避免的会提高系统的时钟频率,时间测量的分辨率如果提高到50 ps,那么相应的时钟频率就要达到20 GHz的标准,这无疑会给硬件设计带来巨大挑战。此外,在高分辨率的工程应用下,系统自身所带有的非线性也会愈发的明显,在测量设备的设计和使用中必须考虑到这一点。

目前,现下流行的时间数字转换器系统的实现方式有两种:利用CMOS实现的全定制ASIC-TDC和可编程逻辑门阵列实现的FPGA-TDC。其中,可编程逻辑门阵列实现的FPGA-TDC凭借其开发周期短、研发成本低、灵活性高的优点,逐渐成为当下此类系统的首选方案。因此,本文采用主流Xilinx工具平台(Vivado)在7系列FPGA(Field-Programmable Gate Array)芯片上构建抽头延迟线结构,从而实现高精度的TDC系统。

尽管通过延迟单元来构建进位链结构有其自身的优势,但与此同时也不可避免的带来一些其他方面的问题。首先要面对的就是编译工具本身[5]的特定属性,使得底层硬件难以实现稳定的进位链结构。其次,可编程逻辑器件中最小延时单元的时间是不可控的,并且会根据温度、电源电压等实际外部因素[6]进行变化,这一问题可以通过对TDC系统进行偏差校准来加以解决。

1 基于进位链的TDC测量原理

本文将该系统分为粗测量部分和精测量部分,粗测量部分用来满足系统对测量量程的要求,精细测量部分来保证对分辨率要求的设计。实际应用中,针对粗测量部分的要求,普遍采用时钟脉冲计数法,这是最简单的测量方法。而精密测量部分则利用底层硬件搭建的延迟链,通过测量起始和结束信号的边缘与基准时钟边缘之间的间隔来实现。

本文采用现下已经很成熟的时间内插技术,通过7系列芯片中Slice单元中专用进位链CARRY4进行级联来构造抽头延迟链结构,每个CARRY4器件内部分布着18个端口(10个输入和8个输出端口)。其中,CYINIT成为开始信号的输入端口,上一个器件的CIN口用来与下一级的CARRY4器件的CI输入端口进行级联,通过这种方法,就可以在在底层硬件中固化成为足够使用的延迟链结构。CARRY4模块内部的具体构造,如图1所示。CARRY4的内部由4个MUXCY和1个MUX组成,最多能引出4个由MUXCY作为基本延迟单元的抽头端口。

图1 CARRY4结构

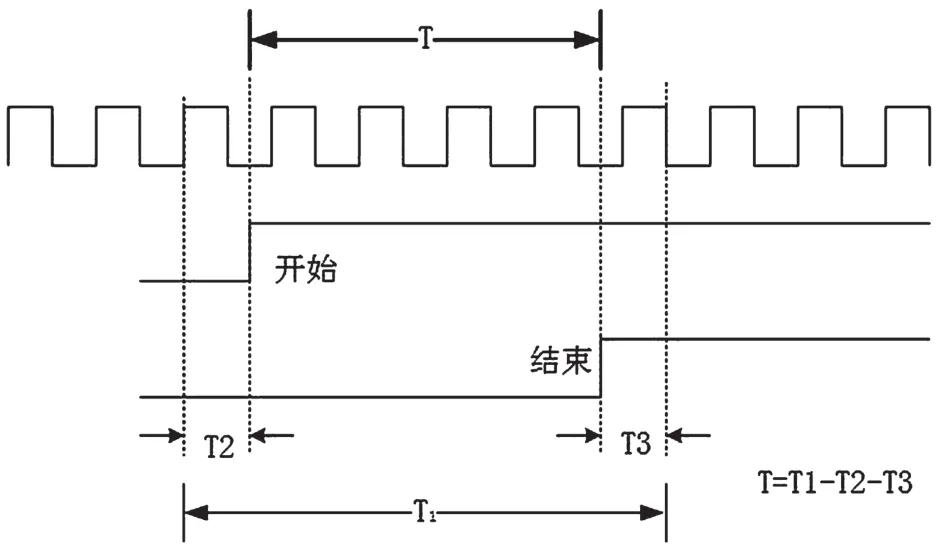

当start信号和stop信号的上升沿到来时,所发出的开始信号就能在构造的延迟链中传播,系统通过设立的多级触发器来准确的捕捉信号的传播位置,一旦某一级的触发器输出变为0,则说明输入信号已传播到此处。其中每级进位链的具体延时可由器件本身工艺来确定,于是就可求得开始信号与结束信号的时间间隔。TDC测量时序图如图2所示。

图2 TDC测量时序

2 TDC系统的设计与实现

在系统的设计与实现的过程中,针对时间测量,有两个非常重要的关键指标:数据精度的最小时间间隔和系统量程的最大时间间隔。通常为了达到设计需要,我们要求测量精度要达到皮秒级别的水平。另外,可以通过扩展Gray码的位数来进行扩展量程。但是,实现细计数精度的提高则是一个相对复杂的过程,也是实际应用中需要重点关注的地方。

根据实际要求,细测模块的量程要达到5 ns(现有条件下的最高的时钟参考频率达到200 MHz),整个系统的时间分辨率应小于100 ps。为测量信号留下10 ps的抖动空间。本文分析并结合现有实际,采用Xilinx工具在7系列FPGA芯片中实现TDC系统,以满足系统的实际要求。

本文设计的TDC系统如图3所示,主要由延迟链模块、两级触发器锁存模块、校准系统和编码模块等构成。使用系统时钟为200 MHz的底层硬件,通过配置255个延迟单元以满足系统的实际需要。由于底层硬件的物理原因,导致各级器件的参考时钟可能并不同步,一旦数据的0-1跳变发生在时钟上升沿周围,那么抽头数据信号便无法满足触发器的建立和保持时间,就会出现亚稳态现象。一旦出现亚稳态,就会造成系统测量错误甚至导致系统在短时内无法正常工作,所以要尽可能避免此类情况发生的概率。

图3 四通道TDC结构

为了保证系统正常稳定工作,文章通过将两个触发器级联在一起的方式,充分利用了两级触发器特有的锁存功能,可以有效的降低系统出现不稳定状态的概率。因为只要系统在第二级触发器建立的时间前达到稳定状态,即使前一级触发器出现亚稳态,第二级触发器锁存的数据就依然是稳定的。同时,采用触发器锁存技术,还能够灵活控制与之相关的温度计编码模块的保持时间,使之不受系统时钟频率的制约,从而降低编码电路的处理速度。

与此同时,为了进一步的提高了系统的测量精度,本文分别配有4条延迟链同时对待测信号进行测量,最后通过求平均值的方式来获得最终的测量结果。

3 基于码密度的校准电路设计

虽然编译软件的后仿可以大概模拟进位链的延迟数据,但这只是一个估计值。实际研究表明,受底层硬件的物理特性的影响,各级延迟单元的延迟时间并不相同。随着电压和温度等外部环境的变化,延迟单元也会随之发生改变[7-8]。因此,实现数字系统转换器的首要问题是怎样实现和固化器件内部的基本单元,并保持系统各个操作的一致性。另外,受频率漂移和底层硬件布局布线的影响,会给测量数据带来一定的误差,必须加以校正,以提高系统的测量精度。

3.1 进位链的校准方式

进位链的校准方式平均延迟校准和码密度校准两种。其中,前者是以各个延迟单元延迟时间相同为前提。然而,该方法是高度假设的,并且不对每个延迟单元执行更精确的校准。当延迟单元的大小发生很大变化时,会导致较大的测量误差,并大大降低系统的灵敏度。当进位链中的信号经过LAB边界或者半边界时会导致该级延迟增大,从而影响最终的测量精度。因此,文章选择第2种方式进行在线校准。

码密度法是一种逐位校准的方法,用于测量每一个延迟单元的真实延迟时间。首先,使用大量均匀分布在一个时钟周期内的随机脉冲作为TDC系统中要测量的输入信号。由于输入信号是随机的,所以信号在落在一个周期内任何一点上的概率是相等的。然后,记录落在各级延迟单元上的次数,并且当随机事件的数量足够大时,延迟时间会与事件的数量成正比,从而可以得出每个延迟单元的具体大小,计算公式如下:

第m个延迟单元采样得到的实际次数为M,N为随机事件的数量,Tm为第m个延迟单元的延迟时间。

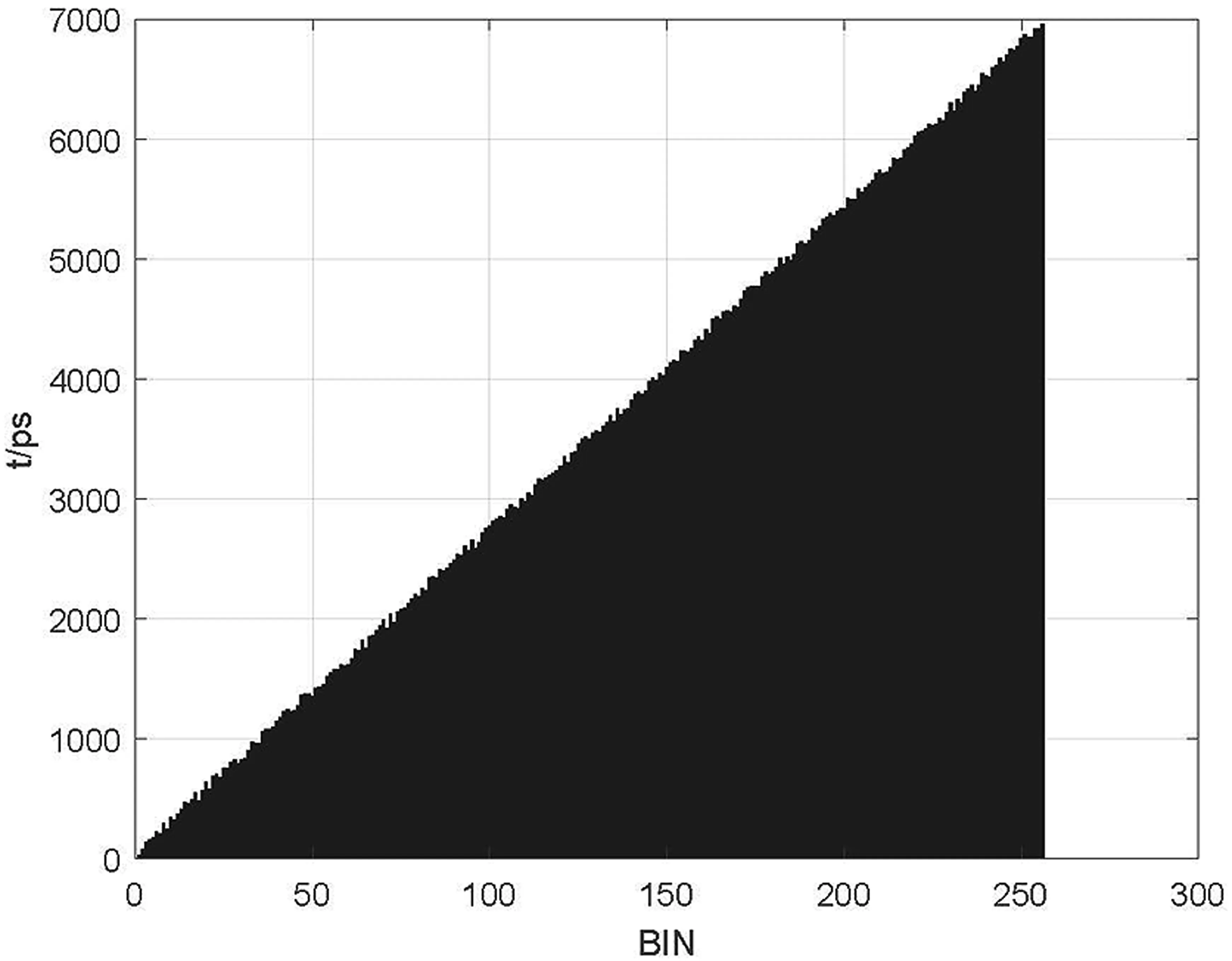

3.2 校准样本数的确定

利用码密度法对系统进行校准的一个关键问题,就是确定随机事件的具体数量N。虽然从数学的角度看,样本数量当然是越多越好,但是数量太多会导致较长的校准时间。对于有限的随机数N,实际计数值nq服从二项分布,其平均值为:

标准偏差为:

假设样本都是随机的,得出:

最后,根据测量精度和进位链级数就可以估算出最小样本数量。在本文中,要求误差小于10 ps,则可以计算出:

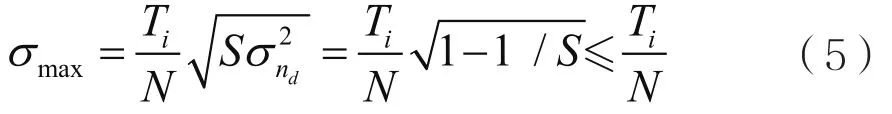

3.3 校准电路设计

通过以上分析,本文设计的校准电路结构框图如图4所示。校准电路主要由随机信号产生电路、保持电路以及查找表存储电路等几个部分组成。随机信号产生电路是利用环形振荡器产生随机信号,而校准电路则是通过对实际存储的校准结果建立累加查找表的方式进行工作。

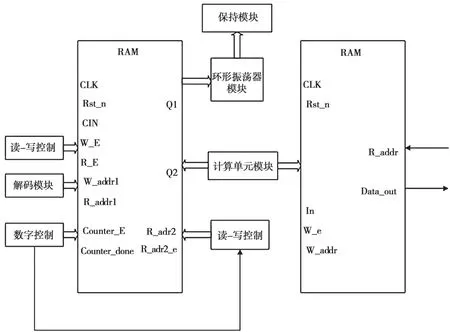

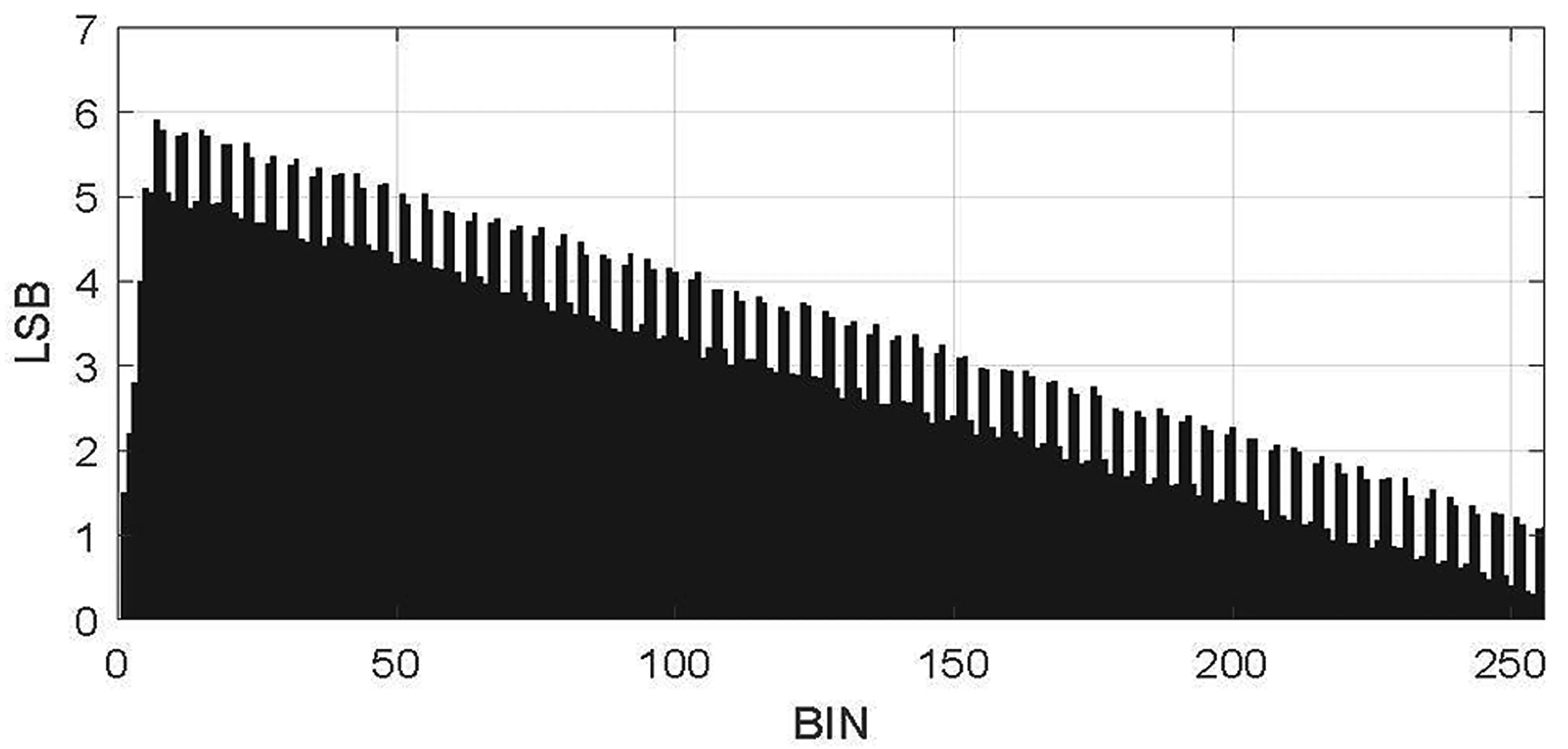

通过统计结果分析,可以得到每个延时单元的具体延时,如图5所示。

图4 校准电路结构

图5 延迟单元测量

4 实测结果分析

分辨率一般用最低有效位(Least Significant Bit,LSB)来表示,代表系统能识别的最小时间间隔。分辨率越高,也就是bit数值越大,信号范围被分割成的区间数目越多,因此,能探测到的信号变量就越小,测量也就越精确。在本文中,由于延迟单元的不一致性,实际上使用的是平均LSB,表示为:

式中,Q为实际内插的延迟单元个数。根据统计结果分析得到平均LSB为30 ps左右。

通过之前的分析可知,由于各个延迟单元的不一致性,导致了系统的非线性。非线性(Non-Linearity,NL)通常用:微分非线性(Differential Non-Linearity,DNL)和积分非线性(Integral Non-Linearity,INL)这两个参数来衡量。

差分非线性(DNL)可以理解为刻度间的差值,即对每个模拟数据按点量化,由于量化产生的误差。文章中用来表示码宽与最低有效位(LSB)之间的偏移值,微分非线性实际上是反映了时间码宽之间的不均匀程度,严重的微分非线性会导致失码。可表示为:

式中,LSB´为各个延迟单元的实际延时;LSB则为各个延迟单元的平均延时。

积分非线性(INL)可以理解为单值数据误差,对应模拟数据由于元器件及结构不能精确测量而产生的误差。相当于微分非线性(DNL)的累加运算,可以表示为:

根据结果统计,微分非线性和积分非线性的仿真结果如图6、图7所示。可以看出延迟链微分非线性(DNL)为(-1,2)LSB,积分非线性(INL)为(-1,6.5)LSB,说明使用该方法有较好的稳定性和线性度。

图6 INL

图7 DNL

5 结 语

本文采用近年来应用广泛的Xilinx 7系列FPGA芯片,借助主流软件设计了一种高精度时间数字转换器系统,由延迟链、两级触发器、校准模块和编码模块等构成。通过码密度法可以得到每个延迟单元的具体延迟时间,并且可以分析其中的不一致性。在抽头延迟线的数据锁存过程中,采用了两级触发器级联的方式,有效的降低了系统的亚稳态性。该方法适用于目前Xilinx公司的主流芯片,填补了该公司在主流器件上利用时间内插技术实现时间数字转换器系统的技术空白,有利于该方法在各个电子应用领域的推广使用。