基于EIM总线传输的数据通信接口设计实现

2019-04-28乔霖李永红岳凤英

乔霖 李永红 岳凤英

摘 要:以Freescale公司LMX6系列的ARM处理器及Xilinx公司的Kintex_7系列FPGA为核心的硬件平台,介绍了一种通过EIM总线接口传输的ARM与FPGA之间的数据通信设计实现方法。文中简单概述了EIM总线数据通信的功能特点及异步通信的基本原理,基于Linux嵌入式操作设计完成EIM总线接口驱动代码开发,通过VHDL硬件语言配置数据通信逻辑,结合测试代码通过EIM接口对FPGA的相关寄存器进行读写测试,通过ChipScope设置信号触发,完成通信数据采集与验证。通过该通信接口的研究设计,实现ARM系统与FPGA之间的高速数据互联通信,实时性强,传输速率高。该技术已成功运用于某型多功能总线数据采集板卡设计。

关键词:通信接口;EIM总线;异步通信;通信逻辑;读写测试;通信验证

中图分类号:TN913-34;TP274

文献标识码:A

文章编号:1004-373X( 2019) 24-0092-04

0 引言

随着高速数字信号处理技术的发展,ARM嵌入式设备外设控制要求不断增加,单一的ARM嵌入式处理设备应用开发越来越难以满足日趋复杂产品的应用需求,而伴随着可编程逻辑器件FPAG的广泛拓展应用,为ARM嵌入式设备功能扩展研发提供了一种有效的解决办法。作为嵌入式技术发展的重要方向,两者之间数据交互通信,为复杂的高速数字信号处理业务提供了完善的硬件解决方案[1-3]。作为该平台设计方案的核心,如何实现两者之间的高速通信配置是该方案设计的技术难点。

I.MX6系列多媒体应用处理器是Freescale公司面向解决多媒体和显示应用的最灵活设计开发平台,具有多核可扩展和低功耗、性能和完备的集成度等优势。基于ARM9rM,ARM Cortex-A9等内核处理器技术,为快速增长的消费电子、汽车和工业市场应用提供较好的需求解决方案[4]。EIM总线是Freescale公司I.MX6系列芯片的重要并行数据总线接口,主要用于同外设芯片或外部存储器进行数据传输,实现异步访问带SRAM接口的外设器件或者同步访问带NOR FLASH或PSRAM等接口的外设器件[5]。本文采用Freescale公司的I.MX6Q处理器及Xilinx公司的Kintex_7系列FPGA为核心的硬件设计平台,连接EIM总线接口设计实现ARM Cortex-A9处理器与FPGA之间的高速数据通信。该技术方法实现从Linux操作系统应用到FPGA的底层数据链路通信,可作为相关高速数字信号采集与处理的平台设计研发关键性技术参考,有效地降低了相关项目开发难度,缩短了研发周期。

1 EIM总线概述

EIM总线是I.MX6Q处理器与外部片外和存储器设备之间数据通信的重要并行总线接口,可为其提供片选、时钟和读、写逻辑控制等功能。作为I.MX6Q与外设芯片之间重要的并行通信总线接口,EIM总线接口通信具有数据传输实时性强、误码率低、外设可扩展等优点,它具有以下几方面技术特点:

1)可同时支持多达4个片选信号,灵活的地址空间配置,每个片选分区空间可通过VIA端口自由分配;

2)支持自由选择和定义分区寻址空间,最高可同时满足6个寻址空间独立定义和配置;默认每个独立片区支持128 MB寻址空间;

3)每个独立片选具备可选的写保护引脚,支持16 bit/32 bit复用地址/数据模式;

4)支持X8,X16和X32的数据位大小配置,每个片选空间读/写通道具有独立的等待状态控制信号;

5)异步访问模式支持可编程的控制信号保持和建立时序,可编程的自由或固定的读、写潜伏期时序配置,支持异步页面访问模式;

6)支持同步内存突发读/写模式访问NOR-FLASH和PSRAM等存儲设备;

7)支持大/小端点访问操作模式,RDY-INT信号设置外部中断功能和定义外部启动信号等;

8)通过AXI总线协议进行数据通信,支持直接存储访问( Direct Memory Access,DMA)数据传输技术。

EIM总线通过配置控制寄存器MUM,SRD,SWR等模式控制位,支持异步访问模式、异步页面模式、多路复用地址数据模式、突发时钟模式、低功耗模式及启动模式等工作模式[6]。这些工作模式下,根据DSZ位可改变支持8 bit,16 bit或32 bit数据位大小。

2 系统设计

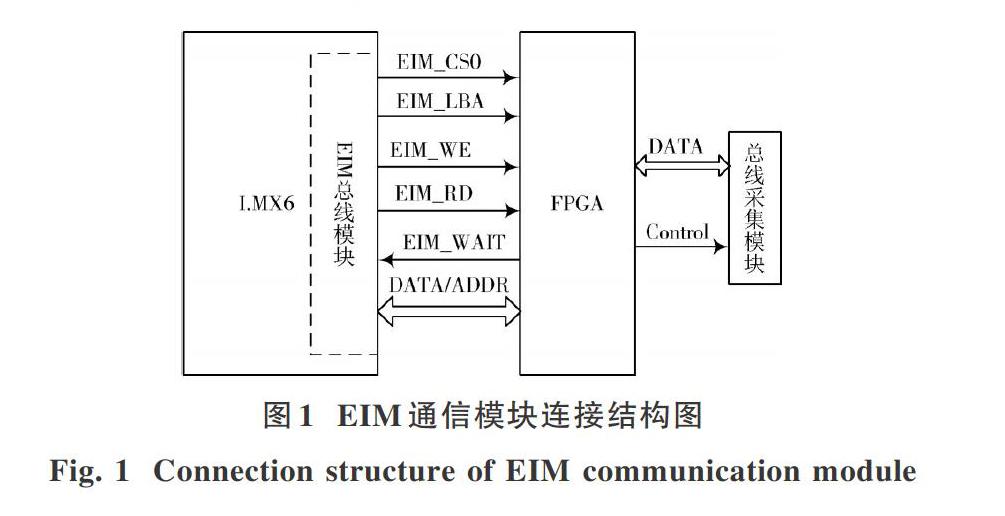

数据通信接口模块设计通过EIM接口实现ARM与FPGA之间的数据链路通信,通信模块连接结构如图1所示。Freescale公司I.MX6Q系列处理器芯片支持扩展4个ARM Cortex_A9内核,运行频率最高可达1.2 GHz,支持USB 2.0,IEEE 1588以太网,SD/MMC,SPI,MIPl-HIS等丰富的外设扩展端口[7-8]。处理器内部特殊的哈佛指令和数据分离结构,即实现系统运行性能最优化,又充分地利用了系统存储资源空间。Kintex_7系列FPGA是Xilinx公司性价比最高的新型现场可编程门阵列器件,该系列FPGA芯片串行带宽达800 Gb/s、478 KB逻辑处理单元、34 Mbit分布块RAM,高性能选择1/0技术支持最高1 866 Mb/s的DDR3接口,内置DSP模块25x18乘法器、48位累加器和高性能滤波预加器,峰值性能可达2 845 GMAC/s,高速串行收发器最高可支持到12.5 Gb/s的数据传输速率[9]。

3 EIM驱动开发

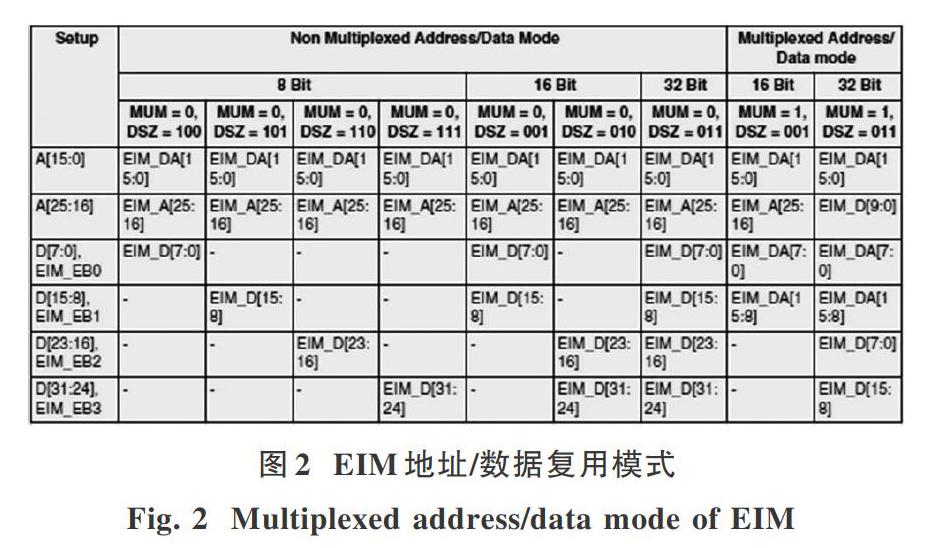

EIM总线驱动开发是完成从FPGA数据采集与ARM应用层数据通信的关键,为底层硬件与应用APP之间通信提供标准的Linux驱动接口[10-11]。EIM总线接口设计配置EIM_CSnGCR1控制寄存器支持如图2所示的几种地址/数据复用配置模式,本设计采用MUM=1和DSZ=O01复用16 bit地址/数据模式,地址线和数据线复用EIM_DA[15:0]引脚,节约引脚数量,减少对其他外设模块影响,地址空间范围为Ox08000000- Ox0800FFFF。由于EIM总线存在端口功能复用,根据配置要求修改端口MUX模式,修改Linux内核board - mx6q_sabreauto.h文件。

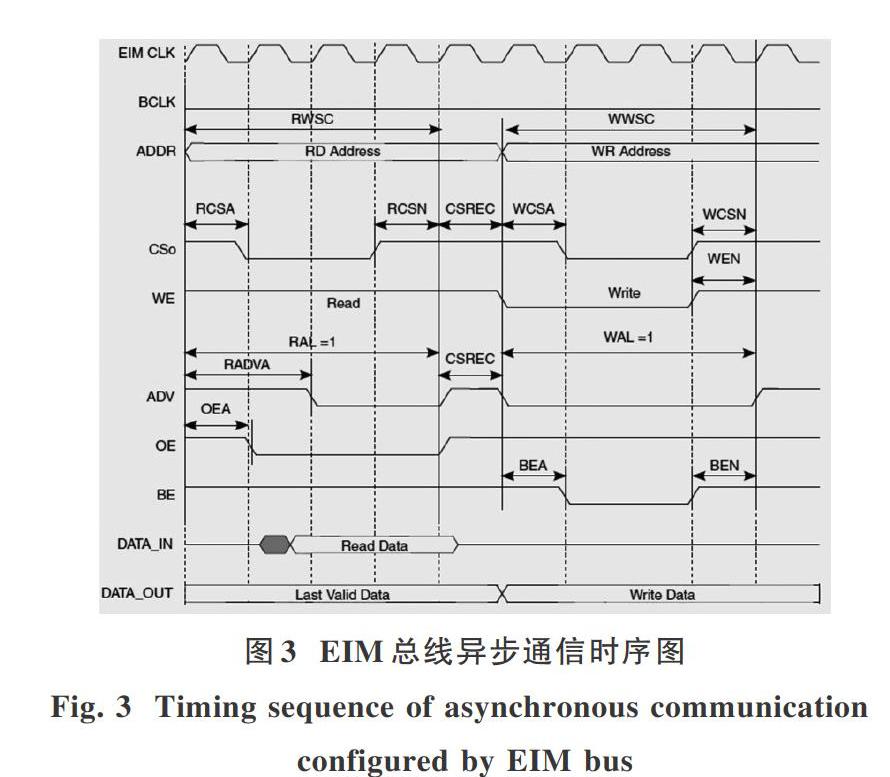

EIM总线配置寄存器用于控制通信时序信息、数据/地址接口数据宽度、片选分区寻址空间设置等,通用寄存器配置完成EIM总线接口初始化,定义接口数据传输的控制性参数,EIM总线配置通信时序如图3所示。根据硬件平台设计要求CSnGCR1通用控制寄存器配置操作模式,MUM=1开启地址/数字总线复用模式,SRD=SWR=1,配置数据读、写传输为异步模式,设置突发长度BL为4个数据字节,设置数据为DS2[2:0]=001,DATA[15:0]对应16 bit数据位,设置EIM读和写配置寄存器CSORCRi和CSOWCRI定义BE,CS,WE,OD及ADV等控制信号建立和保持时钟时序等信息。

void mx6q_setup_weimcs ( void )

{

unsigned int reg;

void _ iomem *eim_reg = oremap (WEIM_BASE_ADDR,Ox20) ;

void _ iomem *ccm_reg = ioremap (CCM_BASE_ADDR,Ox80) ;

if( !eim_reg) {printk ( "error iomem eim_reg\n" ) ; }

if( !ccm_reg) {printk( "error iomem ccm_reg\n" ) ; }

/* For CCM Serial Clock Multiplexer Register *l

/*CCM_CSCMRI : Divicer for aclk_eim_slow *l

reg = readl(ccm_reg + OxIC) ;

reg&=-(Ox60000000);

reg b Ox00380000;

writel(reg, ccm_reg+ OxlC);

/*For CCM Clock Gating Register 6*/

/*CLKCTL_CCGR6: Set emi_slow_clock to be on in allmodes*/

reg= readl( ccm_reg+ Ox80);

reg I= OxOOOOOCOO;

writel(reg, ccm_reg+ Ox80);

/*For EIM General Configuration registers.*/

writel( Ox07f13089, eim_reg);

writel( Ox00000001, eim_reg+ Ox00000004);

/* For EIM Read Configuration registers. CSORCRI,CSORCR2;e/

writel( Ox18022072, eim_reg+ Ox00000008);

writel( OxOOOOb068, eim_reg+ OxOOOOOOOC);

/* For EIM Write Configuration registers. CSOWCRl,CSOWCR2 */,

writel( Oxd863ffe6, eim_reg+ Ox00000010);

writel( Ox00000000, eim_reg+ Ox00000014):

printk(”WEIM init end. CSOGCRl_is%x\n”, readl( eim_reg));

iounmap( eim_reg);

iounmap( ccm_reg);

)

在系統内核文件board-mx6q_sabreauto.c中,为完成EIM接口与FPGA之间通信,添加数据通信各类操作函数,如:imx6_baseboard_init/exit函数提供EIM总线初始化配置和资源卸载;eim_request_irq配置FPGA数据中断请求;eim_write/read_datl6提供基于CSO寻址空间的读、写数据,地址接口映射等。通过修改imx6q-sabreau-to_gpmi-weim.dts文件中参数,注册使能weim-nor驱动程序,完成接口驱动加载配置[12]。

4 逻辑实现

为保证EIM总线通信数据传输的正确性,逻辑读写时序参数需与I.MX6Q驱动寄存器配置保持一致,逻辑设计采用VHDL硬件语言编写,采用模块化编码思想,充分考虑代码功能复用。逻辑程序按照功能可划分为FIFO存储单元、数据采集单元和读/写控制逻辑单元。读操作周期中,数据采集单元将数据缓存至FIFO存储器空间,等待EIM接口数据传输读操作控制。将待读寄存器地址写入EIM地址总线Addr[15:0],通过EIM—LBA信号提示FPGA锁存地址,对应逻辑预设FIFO存储器地址,拉低片选CSO信号后,使能FPGA读设备;拉低OE输出使能,同时释放地址线,将对应FIFO存储器数据写人EIM数据总线Data[15:0];经过Tr时间拉高OE使能信号,读取总线数据,完成EIM总线读操作周期。除OE,BE读/写控制信号外,读写操作逻辑程序基本类似,读/写逻辑数据控制流程如图4所示。5测试

FPGA根据驱动时序编写测试程序,初始化内部寄存器值为Ox0000。通过ARM应用驱动读写函数,对EIM总线数据接口模块进行寄存器读写通信测试。写入FPGA内部定义地址寄存器OxOAOO-OxOAOF依次写入数据位OxOOO01-OxOOOF,然后再通过EIM接口,读对应位写人数据,结合FPGA软件集成环境ChipScope设置信号LBA下降沿触发,捕捉数据波形,验证通信数据采集正确性。采集测试读写操作时序如图5、图6所示,根据测试数据分析表明,通过EIM总线数据通信接口设计实现基本数据传输功能,满足处理器之间数据通信功能要求。

6 结论

本文根据多功能数据总线采集与处理应用项目需求,基于Freescale公司I.MX6Q处理器及Xilinx公司Kin-tex_7系列FPGA为核心的硬件平台,研究实现了一种通过EIM总线接口传输的ARM与FPGA之间的数据通信方法。通过系统地分析EIM接口通信特点,重点介绍了EIM接口设计软件驱动程序开发和逻辑控制的具体实现,通过系统互联通信测试,验证了接口数据通信的正确性,该设计满足接口数据通信需求。结果表明,该技术方法适用于其他类似相关处理器平台通信设备应用场合,具有一定的设计参考价值。

参考文献

[1]张高健,杨刚,杨霖,等.基于ARM+FPGA的多路广播音频处理系统[J].电声技术,2015( 12):68-70.

ZHANG Gaojian, YANG Gang, YANG Lin, et al.Multiplexbroadcasting audio processing system based on ARM and FP-GA [J]. Audio engineering, 2015( 12): 68-70.

[2]朱晓鹏,肖铁军,赵蕙.ARM+FPGA的实时数据采集系统设计[J].计算机T程与设计,2009,30( 13):3088-3090.

ZHU Xiaopeng, XIAO Tiejun. ZHAO Hui. System design ofreal-time data acquisition based on ARM and FPGA [J]. Com-puter engineering and design, 2009, 30( 13): 3088-3090.

[3]常秀清.基于Linux系统的EIM接口数据传输方法[J].无线电工程, 2016.46(6):18-22.

CHANG Xiuqing.A data transmission method for EIM inter-face based on Linux operation system[J].Radio engineering,2016, 46(6):18-22.

[4] NXP Semiconductor. Embedded solutions based on ARM tech-nology guide [M]. Austin: Freescale. 2014.

[5]陈崇森,基于i.MX6Q+FPGA平台Android下EIM总线接口设计[J].现代计算机,2016( 13):60-65.

CHEN Chongsen. Design of EIM bus interface based on i.MX6Q+FPGA platform under Android [J]. Modern computer,2016(13):60-65.

[6] NXP Semiconductor. i.MX6Dual/6Quad applications processorreference manual [M]. Austin: Freescale, 2017.

[7] NXP Semiconductor.i. MX6 series of applications processors[M]. Austin: Freescale, 2017.

[8]杜培军,闫帅,刘锦高.基于i.MX6车载音视频系统的设计和实现[J].电子设计工程,2015,23( 20):185-188.

DU Peijun, YAN Shuai, LIU Jingao. Design and implementa-tion of vehicle audio and video system hased on i.MX6 [J].Electronic design engineering, 2015. 23(20): 185-188.

[9] Xilinx.7 Series FPGAs data sheet: overview[M]. San Jose:Xilinx. 2017.

[10]宋宝华.Linux设备驱动开发详解[M].北京:人民邮电出版社.2010.

SONG Baohua. Embedded Linux device driver development[M]. Beijing: Ports&Telecom Press, 2010.

[11]韩少云,嵌入式Linux驱动程序实战开发[M].北京:北京航空航天大学出版社 , 2012.

HAN Shaoyun. Implementation of embedded Linux devicedriver development [M]. Beijing: Beijing University of Aero-nautics and Astronautics Press. 2012.

[12] NXP Semiconductor. i.MX reference manual [M]. Austin : Fre-escale. 2018.

作者简介:乔霖(1993-),男,山西临汾人,硕士,研究方向为动态测试与智能仪器。

李永红(1967-),男,山西临汾人,硕士生导师,教授,研究方向为卫星/微惯性组合导航技术、飞行器弹载数据记录仪、

常規弹药制导与控制。

岳凤英(1977-),女,山西忻州人,硕士生导师,副教授,研究方向为导航、制导与控制,检测技术与自动化装置。