适用于3D NAND的高稳定度的 Capacitor-free LDO

2019-04-28万金梅刘飞曾子玉霍宗亮

万金梅 刘飞 曾子玉 霍宗亮

摘要:文中设计一种应用于3D NAND的无片外补偿电容的LDO,该电路在传统嵌套米勒补偿的基础上,增加“gⅢ减小电路”和“轻重载控制电路”,实现在空载(电流负载为零)且有大负载电容条件下的稳定。此设计应用YMTC 0.18 μm工艺实现,仿真结果显示,在2.5-3.6 V电源供电下,整个电路消耗的静态电流为50μA,总补偿电容为7 pF,电路稳定的时间小于6μs,输出线性调整率小于2.2 mV/V,负载调整率小于0.9 mV/mA。

关键词:LDO;米勒补偿;3D NAND;电路设计;仿真实验;稳定性分析

中图分类号:TN911-34; TP301.6

文献标识码:A

文章编号:1004-373X( 2019)24-0042-04

0 引言

近年来,越来越多的适用于SoC的LDO调制器结构相继被提出[1-4],其中,文献[3-7]都采用了嵌套米勒補偿,但普通的嵌套米勒补偿只能实现小负载电容条件下的稳定。对于应用于3D NAND中的LDO而言,由于它给整个NAND中的所有charge pump供电,并且相邻平面间的寄生电容比原来的2D NAND增大了4倍左右[8],因此对LDO负载提出了特殊要求,需要能支持nF级负载输出电容。因而对空载(电流负载为零)条件下的LDO环路稳定性提出了挑战。为了确保线性调制达到要求,电路的环路增益必须足够大,文献[3]利用基于FVF的DSMFC结构,可以实现负载电容为10 pF-10 nF范围内的稳定,但是重载条件下的环路增益只有50 dB,达不到精度要求。文献[4]通过增加增益级去提高环路增益和负载调制、线性调制等,同时利用米勒补偿实现稳定,但只能实现最大负载电容为50 pF的稳定。因此在大负载电容条件下,如何同时实现高增益和稳定性是一个难题。本文利用嵌套米勒补偿,并增加“gm减小电路”和“轻重载判断控制电路”,只需7 pF的补偿电容便可轻松实现负载电容为1 nF,负载电流为空载条件下的快速稳定,并且环路增益总体达96 dB以上,具有更好的线性调整率。

1 LDO结构及稳定性分析

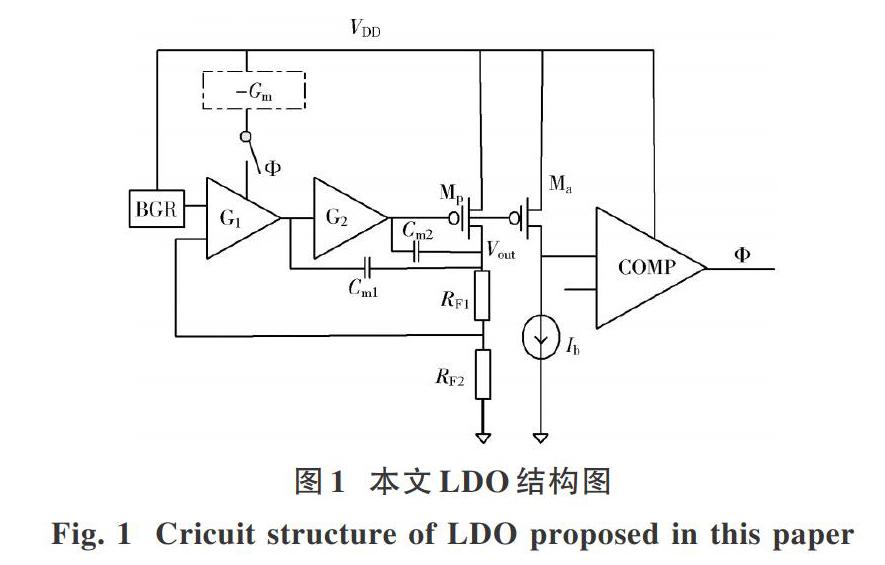

本文提出的LDO结构如图1所示,包括“gm减小电路”(虚线所框区域“一Gm”)、两个增益级(G1,G2)、功率管和“负载判断控制电路”等。其中由负载感应电路和迟滞比较器构成“负载判断控制电路”,用于控制轻、重载两种不同工作模式下的“gm减小电路”的开启和关闭。

由式(4)和式(6)可知,各极点位置g。,与无关,只有环路增益式(5)与gm1有关。利用本文的方法,在轻载时,控制开关中关闭,此时“gm减小电路”加入,第一级放大器的跨导Gm=gm1-gm;重载时,控制开关中打开,“gm减小电路”与LDO断开,为正常米勒补偿结构,此时第一级放大器的跨导Gm=gm1。

在轻载条件下,电路本身增益足够大,在不改变原来各个极点位置的情况下,利用“gm减小电路”使得增益曲线向下移动,从而保证空载条件下的稳定性。而在重载条件下,电路本身增益较小,这时释放“gm减小电路”,从而弥补了因重载而负载电阻小,从而导致增益小的缺陷。图3为本文LD0和嵌套米勒补偿的LDO幅频响应对比图,由图可以看出在空载时,不改变各个极点的位置,仅仅将增益曲线向下移动,能更好地满足相位裕度和增益裕度要求,实现电路的稳定。2电路设计

本文提出的LDO电路如图4所示,第一增益级里的“gm减小电路”(如图4中虚线区域所示),作用是在轻载条件下减小第一级的gm。通过Ma管复制功率管Mp的电流,Mb充当一个恒流源,当处于轻载时,流过MP的电流较小,Ma和Mp栅电压较高,从而迟滞比较器的输入电压低于参考电压Vref2,则比较器输出为高,则控制开关中使得“gm减小电路”开启;反过来,重载时,控制开关中使得“gm减小电路”关闭,此时整个LDO为嵌套米勒补偿的正常结构。

3 仿真结果

本文在YMTC 0.18 μm工艺下用cadence的Spectre仿真,电源电压为2.6-3.6 V。负载电容CL范围为0 pF-1 nF,负载电流范围IL为0-5 mA。图6a)和图6b)分别为负载电容为1 nF和1 pF时对应于不同的负载电流IL下的开环增益和频率响应图。

可以看出仿真结果和表1的推导结果一致。在全负载电流范围内,电路环路增益都在95 dB以上,并且相位裕度都在86。以上。在负载电容为1 nF、空载时,电路因为共轭极点导致“尖峰”出现,利用本文的方法,很好地将尖峰移至0 dB以下,从而保证了电路的稳定。

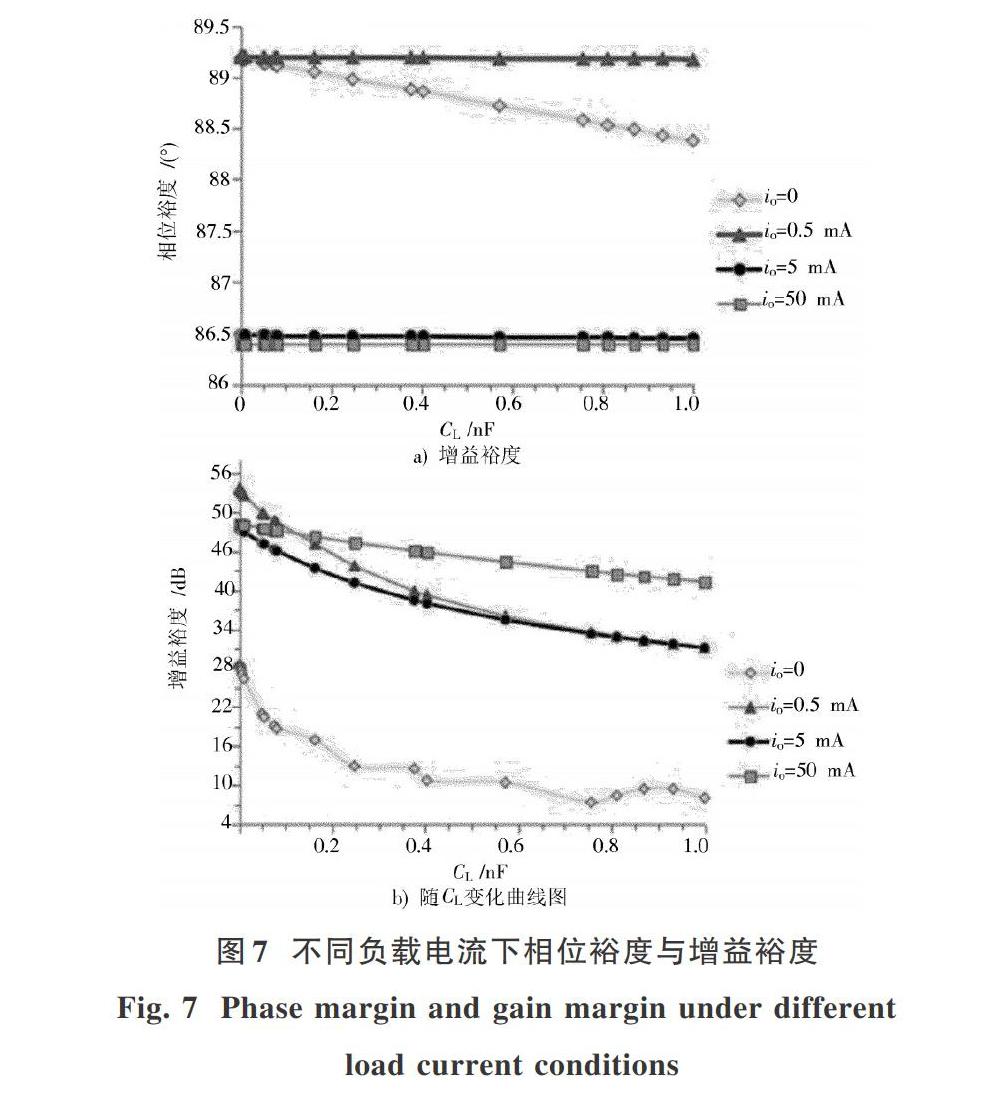

图7a)和图7b)分别为不同负载电流下电路相位裕度和增益裕度随CL变化曲线图。

由图可以看出,随着CL的增大,相位裕度和增益裕度都呈下降趋势,在轻载尤其是空载时,电路由于加入了“gm减小电路”,增益曲线向下移动,因而相位裕度和增益裕度都比重载条件下大。但在相同负载电流情况下,随着CL增大,次极点也越来越靠近主极点,因而裕度也会相应的减小。整体来看,电路相位裕度都在860以上,增益裕度最差也在7 dB,因此具有高稳定度。

4 结论

本文利用新颖的方法设计了一款适用于3D NAND的LDO。仿真结果表明,在相同负载电容情况下,本文的LDO所需补偿电容最小,具有更高的环路增益和更好的线性调制。

参考文献

[1] HUANG W. LIU S. Capacitor-free low dropout regulators usingnested Miller compensation with active resistor and l -bit pro-grammahle capacitor array [J].IET circuits, devices & sys-tems, 2008, 2(3) : 306-316.

[2] ZHAN C, KI W H. An output-capacitor-free adaptively biasedlow - dropout regulator with sub - threshold undershoot - reductionfor SoC [C]// IEEE International Symposium on Circuits & Sys-tems. Rio de Janeiro : IEEE , 2011 : 45-48.

[3] TAN X L, KOAY K C. CHONG S S, et al. A FVF LDO regula-tor with dual- summed miller frequency compensation for wideIoad capacitance range applications [Jl IEEE transactions on cir-cuits & systems I: regular papers, 2014, 61(5) : 1304-1312.

[4] GUO J, LEUNG K N. A 6-W Chip-area-efficient output-capaci-torless LDO in 90-nm CMOS technology [J]. IEEE Journal ofcircuit, 2010, 45(9) : 1905.

[5] KAMAL Z, HASSAN Q, MOUHCINE Z. Full on-chip CMOSlow dropout voltage regulator using MOS capacitor compensa- tion [C]// 2012 International Conference on Multimedia Comput-ing and Systems. Tangier: IEEE, 2012: 1109-1114.

[6] MAITY A, PATRA A. Trade-offs aware design procedure foran adaptively hiased, capacitor-less low drop-out regulator us-ing nested miller compensation [J]. IEEE transactions on powerelectronics, 2015 , 31( 1) : l.

[7] GARIMELLA A, RASHID M W, FURTH P M. Nested millercompensation using current buffers for multi- stage amplifiers[C]V/ 2011 IEEE 54th International Midwest Symposium on Cir-cuits and Systems. Seoul : IEEE , 2011 : 1-4.

[8] FU Liyin, WANG Yu, WANG Qi, et al. A high efficiency all- PMOS charge pump for 3D NAND flash memory [J]. Jonurnalof semiconductors . 2016. 37( 7 ) : 98-103.

[9] CHONG S S. CHAN P K. A 0.9-/spl mu/A Quiescent currentoutput-capacitorless LDO regulator with adaptive power transis-tors in 65-nm CMOS [Jl IEEE transactions on circuits and sys-tems I: regular papers, 2013, 60(4) : 1072-1081.

[10] PENG S Y. LIU L H, CHANG P K. et al. A power efficient re-configurable output-capacitor-less low-drop-out regulator for low-power analog sensing front-end [J]. IEEE transactions on cir-cuits and systems I: regular papers, 2017, 64(6) : 1318-1327.

作者簡介:万金梅(1993-),女,硕士研究生,主要研究方向为模拟集成电路设计。

刘飞(1974-),男,博士,研究员,主要研究方向为数模混合设计。

曾子玉(1985-),男,硕士研究生,主要研究方向为模拟集成电路设计。

霍宗亮,男,博士,研究员,主要研究方向为三维存储器件及设计。