数字化仪控平台中基于AT96总线的数据交互设计

2019-04-09伍巧凤孙诗炎王明星

伍巧凤,贺 理,李 昱,孙诗炎,王明星

(核反应堆系统设计技术重点实验室,成都 610213)

0 引言

数字化仪控平台[1,2]中控制器单元通过背板AT96总线与各功能单元进行数据交互,以实现了不同功能需求[3]。AT96总线是由德国西门子公司发起制定的工控机总线标准,其作为ISA总线的兼容协议,采用PC的Wintel架构,具有抗冲击力强、机械结构合理、适合工业现场使用,易于维护等特点。AT96总线内存使用机制与PC计算机完全一致。控制器单元的内存只能有640K~1M内存区间,并且这里面的大多数内存已经被显卡等设备占用,因而可以使用的空间很小,基本上只能提供一个几十KB的页面给功能单元使用,但若功能单元数量众多,显然无法满足系统设计要求,所以需要通过一种机制来扩展内存。因此,采用内存分段和页面扩充技术,将一个内存空间扩充为多个页面,来实现控制器单元与多个功能单元的信息交互,并且在系统中通过180°跟随机制来防止控制器对功能单元的访问冲突。

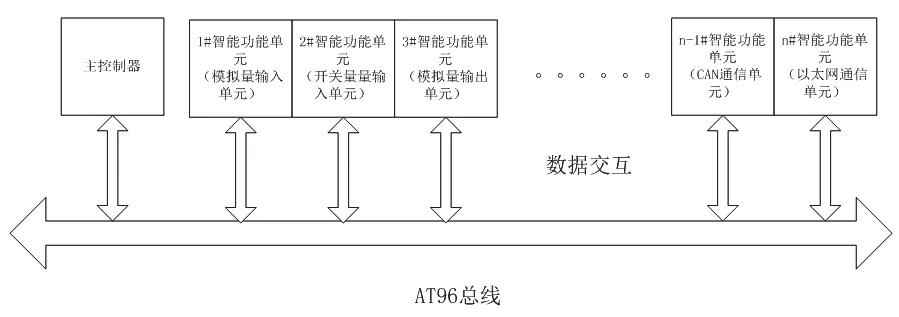

图1 数字化仪控平台构架Fig.1 Digital instrument control platform architecture

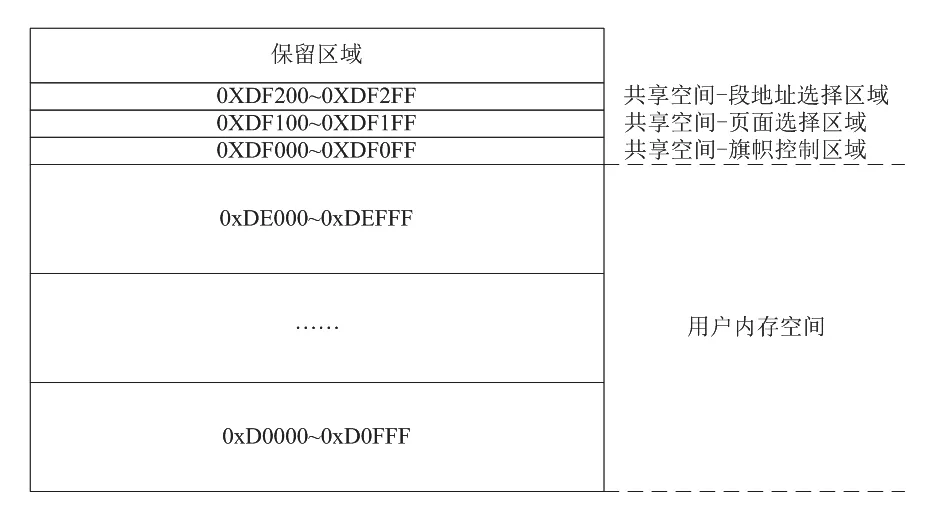

图2 内存地址分配图Fig.2 Memory address assignment diagram

1 数字化仪控平台构架

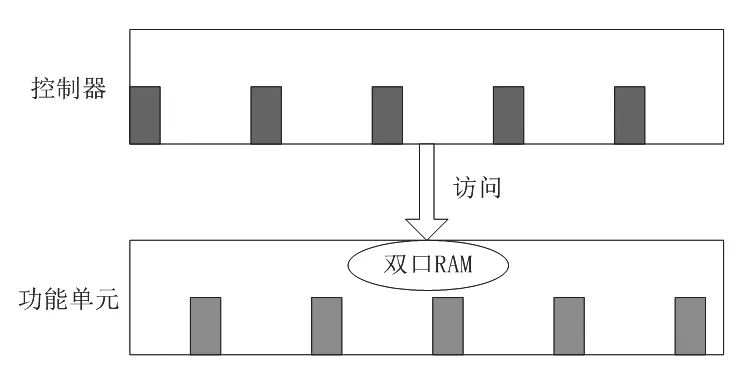

数字化仪控平台由主控制器、AT96总线、智能IO功能单元(模拟量输入单元、模拟量输出单元、开关量输入单元、开关量输出单元、以太网通信单元、CAN通信单元等)组成,其构架见图1。

IO功能单元为智能设计,各功能单元自带微处理器,独立进行数据采集和处理,数据存放于各功能单元的双口RAM。控制器通过AT96总线与功能单元双口RAM进行数据交换。

2 数据交互设计

2.1 内存分配

一般控制器的内存只能在640K~1M内存区间,并且这里面的大多数内存已经被显卡等设备占用。因此,可以使用的空间很小,平台中的控制器基本上只能提供一个64KB的页面给IO功能单元使用,但平台中板卡数量众多,显然无法满足系统设计要求,需要通过一种机制来扩展内存。

图2是内存地址分配图。在图2中,将内存分为16个内存段,每个内存段4KB,标识为0~F。例如,第1段内存为0xD0000~0xD0FFF,第2段内存为0xD1000~0xD1FFF……以此类推。标识为0~E的60KB为用户内存空间,一旦切换以后,为该功能单元独占使用。标识为F的4KB为共享区间,为所有功能单元共用。在共享区间中,其低端的256Bytes区间为抢旗帜区间,其地址为0XDF000~0XDF0FF;其次为页面选择区间,占用256Bytes区间,其地址为0XDF100~0XDF1FF;依次往上的256Bytes区间为段地址选择区间,其地址为0XDF200~0XDF2FF,剩余的区间为保留区间,暂不使用。

2.2 页面扩展

基于2.1节内存分配技术进行页面扩展,本系统将64KB页面扩充成64个页面,每个页面64KB,以4KB为段单位,包含16个内存段,前15个内存段(编号0~E)为用户内存空间,用以存储交互数据,每个功能单元可以根据实际需求占用1~15个内存段,第16个内存段(编号F)作为共享区间,用于命令发送等控制使用。

本系统各个页面分配如下:

页面0:为I/O类型功能单元使用区间,每个板卡占用一个4KB内存段,最大同时支持15个板卡,板卡的内存段通过4bit拨码开关选择。

页面1~8:为隔离CAN通信单元使用区间,每个CAN通信单元占用2个内存段,内存段通过6bit拨码开关选择,其中3bit为页面选择,3bit为内存段地址选择。

页面9~16:为隔离RS485通信单元使用区间,每个RS485通信单元占用2个内存段,内存段通过6bit拨码开关选择,其中3bit为页面选择,3bit为内存段地址选择。

页面17~24:为隔离以太网通信单元使用区间,每个以太网通信单元占用2个内存段,内存段通过6bit拨码开关选择,其中3bit为页面选择,3bit为内存段地址选择。

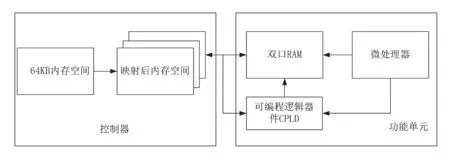

图3 内存页面扩展Fig.3 Memory page extensions

图4 180°跟随机制示意图Fig.4 Diagram of 180°following mechanism

页面25~63:系统保留,可扩展。

系统内存扩展由一个CPLD和双口RAM来实现,CPLD负责进行地址译码和命令解析,同时输出控制信号,以及对冲突进行检测。

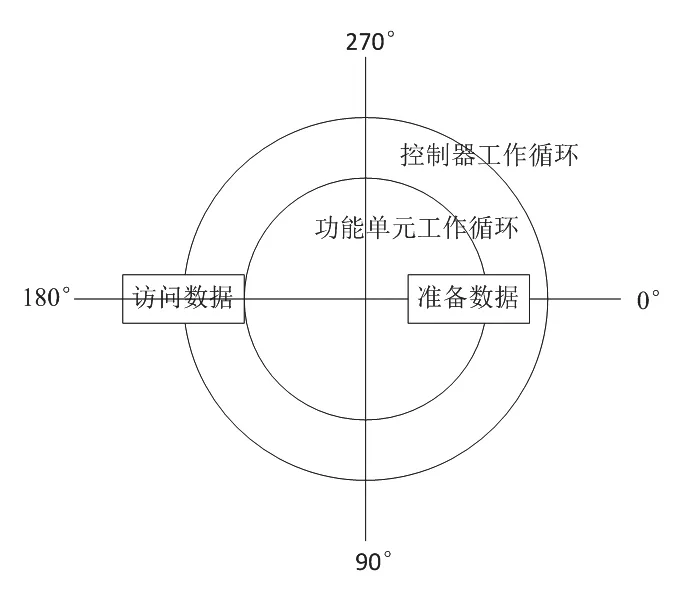

2.3 180°跟随机制

因功能单元为智能设计,各功能单元自带微处理器,所以可在智能单元工作循环中准备数据的时刻,与控制器访问数据的时刻错开180°。即根据控制器的访问周期,功能单元自行测算出控制器每两次访问周期的中间时刻,在这个中间时刻智能单元准备数据。这样,即使控制器出现突发情况,造成访问功能单元的时间点提前或者延后,但由于这个中间时刻的存在,可以尽最大可能避免控制器访问功能单元时出现冲突或者无效。

图5 时间片同步示意图Fig.5 Time slice synchronization diagram

图6 时间片同步调整示意图Fig.6 Time slice synchronous adjustment diagram

在实际工作中,功能单元微处理器在空闲时刻时,一直监视硬件双口RAM标志的访问变化,并根据该变化确定控制器的访问时刻,每经过一段时间,微处理器都会评估自己和控制器之间时刻的同步性,然后根据评估结果,调整自己对双口RAM的访问时刻,以实现与控制器的同步跟随功能。在这种跟随机制下,功能单元会随时测量控制器的访问周期,随时保持与控制器访问周期错开180°的间隔。

图5为正常情况下控制器对功能单元的访问示意图,功能单元准备好数据,控制器稍后就可以访问,二者和谐共处,不会因此发生冲突。

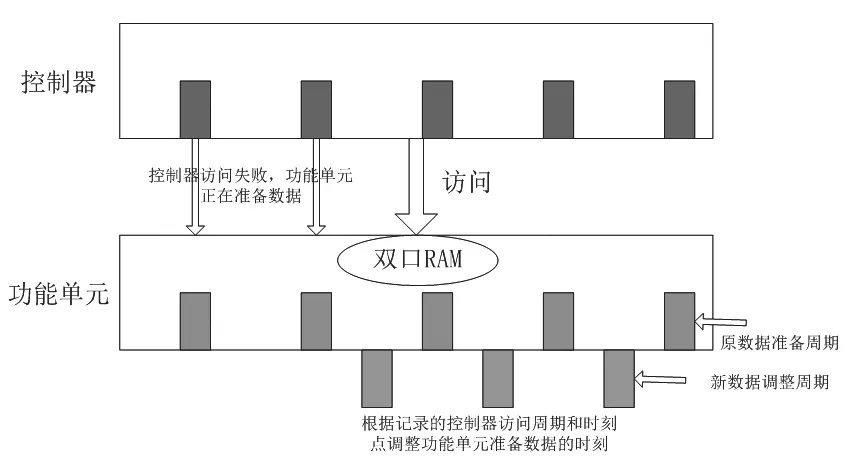

当运行一段时间后,可能出现图6所示情况。

在图6中,控制器和功能单元循环周期没有改变,改变是控制器对功能单元的访问时刻,导致控制器每次访问功能单元时,均与功能单元数据准备相冲突,从而只能放弃当前时间片。功能单元微处理器记录每次控制器的访问时间点,当其探测这种冲突情况后,功能单元会自动避开控制器的访问时间点,前移自己的数据准备周期,从而有效处理冲突的情况。功能单元在前移时,可以计算好时间,使得数据准备时间正好与控制器访问时间错开180°。这样联动处理后,一是解决了控制器对功能单元数据访问的及时性,二是提高了带宽的利用率。

3 结论

数字化仪控平台通过AT96总线实现控制器与智能IO功能单元的数据交互,在控制器内存不足的情况下,通过内存分段和页面扩展技术实现控制器内存扩展,从而实现控制器与众多智能IO功能单元的数据交互。因IO单元的智能化设计,在IO功能单元微处理器中设置180°跟随机制,实现功能单元准备数据和控制器访问数据的180°延时,在有效处理冲突的同时,提高了带宽的利用率。