基于FPGA的视频图像低通滤波处理

2019-03-30张晓晶

张晓晶

摘要:利用Altera公司CycloneⅢ系列的FPGA作为主控芯片,通过VHDL语言编程,设计实现了一个实时的视频低通滤波处理系统。通过低通滤波改变输入视频信号的带宽,从而在监视器上观测到不同带宽视频信号的显示质量变化。

关键词:图像滤波;低通滤波;FPGA

中图分类号:TN713.4 文献标识码:A 文章编号:1007-9416(2019)12-0119-02

0 引言

实时视频处理是图像处理领域的研究热点之一,广泛应用于可视电话、视频会议,监控、通信等领域中。现场可编程门阵列(FPGA)的优点在于其灵活的可编程性和强大的并行处理能力,可以把很多图像处理功能集成在一个FPGA芯片上。为了观测不同带宽视频信号的显示质量变化,本文基于FPGA设计实现了一个视频图像低通滤波处理系统。降低视频信号的带宽,只会改变视频图像的水平分辨力,而视频图像的垂直分辨力是由电视系统的扫描参数决定的,基本不受信号带宽变化的影响[1],所以本文只需要设计水平滤波器,不需要设计二維滤波器。

1 系统整体设计

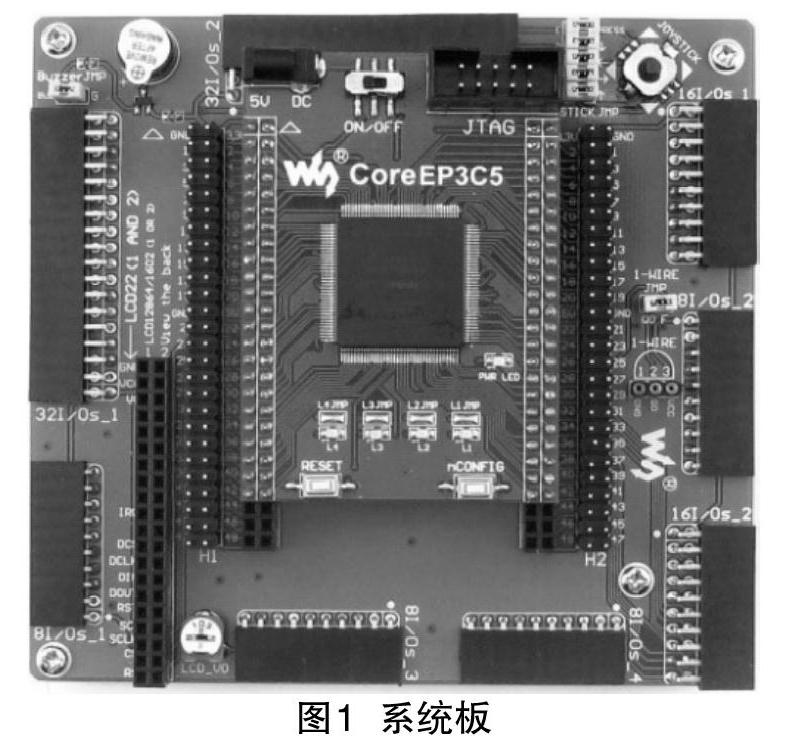

本系统的硬件平台如:FPGA型号为EP3C55F484用于对视频进行实时低通滤波处理。A/D芯片为TVP5150将输入的模拟视频信号转换为数字信号输入FPGA,D/A芯片为ADV7171将处理后的数字视频信号转换回模拟视频最终在监视器上显示,另外FPGA连接了两块16bit数据线的SRAM用于对视频数据进行存储。系统板如图1所示。

1.1 信号采集

在系统前端,先利用摄像头取得光学图像。摄像头的输出为一路PAL制复合视频信号,完成光信号到模拟电信号的转变。之后通过TVP5150视频解码芯片将模拟信号转变为数字信号。利用FPGA对TVP5150进行I2C配置,选择输出格式为ITU-RBT.656,即时钟频率为27MHz的4:2:2取样格式的YCrCb信号。

1.2 场解码

一帧完整的PAL制式ITU-RBT656数据分为奇偶两场,23-311行为偶数场有效数据,366-624行为奇数场有效数据,其余为行场控制信号或无效数据。每行前288byte为行控制信号,其中最前面的4byte为EAV(有效视频结束)信号,最后面的4byte是SAV(有效视频起始)信号。

EAV信号和SAV信号均有3byte的前导:FF,00,00。最后1byte为XY。F为奇偶标志位,V为垂直消隐标志位,H为水平消隐标志位,P3,P2,P1,P0为保护比特位。首先通过连续判断FF,00,00和XY来进行F、V、H的提取与检测。若H为0,即为SAV,再去判断F,若F为0,即为奇数场,若F为1,即为偶数场。每当F从1跳变到0,则为一帧的帧头。之后去判断V,若V为0,则为场正程。由于我们只处理有效数据,所以在检测到帧头的情况下,若H=0且V=0,则此行为有效数据。

1.3 帧缓存

本文利用两块SRAM进行乒乓存储实现处理与显示之间的转换。以一帧数据为单位进行存储。当向SRAM1中写当前帧时,读的是SRAM2中存储的前一帧,当SRAM1中存好一帧后,才会进行乒乓切换,读取SRAM1中的数据。

一帧中的有效数据为720×576个像素,开始时写地址指针位于(0,78),当检测到帧头且H=0、V=0后,第一行有效数据的SAV中的FF、00会写入(0,78),随后的00、xy会写入(0,79),随后的第一个有效像素会被写入(0,80)。存储时,若发现SAV中的F从0跳变到1时,意味着奇数场结束,进来的将是偶数场的数据,写地址指针将跳到(1,78),进行偶数场的存储。当F从1跳变到0,即为新的一帧帧头,写地址指针会重新位于(0,78),如此循环往复。

2 视频低通滤波在FPGA上实现

2.1 低通滤波器的设计

人眼对色度变化的敏感性很低,故本文只对亮度信号Y分量进行低通滤波处理[2-3]。因为输入信号的时钟频率是27MHz,输入数据是YCbYCr格式,即一个亮度信号一个色度信号的排列,可知像素时钟为13.5MHz,即Y信号的采样频率为13.5MHz。在标清信号中输入视频信号的带宽一般不大于6MHz,我们这里选择将输入视频信号的带宽限制在3MHz以内,即对应的数字低通滤波器的截止频率为:

wc=fc/fs*2pi=3/13.5*2pi=0.44pi

从而可进行低通滤波器的设计。

2.2 低通滤波器在FPGA上实现

本文选择12阶FIR滤波器实现,得到13个系数,FIR滤波器实现的公式为:

(1)

其中h(n)为滤波器系数,x(n)为每行像素的亮度Y值,y(n)为滤波后的像素的亮度信号Y。

使用该公式滤波会造成输出图像相对于输入视频图像产生向右的平移。为了避免滤波后图像的移位问题,本文先对输入的像素进行缓存然后使用非因果滤波器进行滤波,由于所设计的滤波器是线性相位的滤波器,即系数是对称的,可采用线性相位结构以提高计算效率,这样滤波一次只需要7次乘法。由于得到的FIR滤波器的系数都是小数,本文先对滤波器的系数进行左移8bit进行放大,在完成滤波的相乘累加处理后再把所得结果右移8bit恢复到原来的大小,从而实现亮度信号Y分量的低通滤波处理。

3 实验结果

通过以上步骤,完成了各个系统模块的设计,实现了摄像头采集视频的降低带宽处理,滤波前输入图像是多波群信号,包含了0.5M,1M,2M,4M,4.8M和5.8MHz的信号。经过截止频率为3MHz的低通滤波后,高于3MHz的信号被滤除,即4MHz、4.8MHz和5.8MHz的信号被滤除,只保留了0.5MHz、1MHz和2MHz的信号。

4 结语

本文基于FPGA设计实现了对视频图像信号的低通滤波处理,滤波器的截止频率可以不同,比如选择1MHz、2MHz、3MHz、4MHz等,不同截止频率的滤波器可以通过修改FIR系数改变,所以可以很方便的观测不同带宽的视频信号的显示质量的变化。整个系统分为场解码模块、帧缓存(乒乓存储)模块和低通滤波模块。实验结果表明了本方法的可行性。

参考文献

[1] 张虎军.基于FPGA的视频采集输出系统的实现[D].大连海事大学,2011.

[2] 俞彬杰.基于FPGA的全彩色LED同步显示屏控制系统的设计[D].上海交通大学,2008.

[3] 吴镇杨.数字信号处理[M].高等教育出版社,2016.

FPGA-based Video Image Low-pass Filtering

ZHANG Xiao-jing

(Beijing Polytechnic, Beijing 100176)

Abstract:A real-time video low-pass filter processing system is designed and implemented by using FPGA of cyclone Ⅲ series of Altera company as the main control chip and programming with VHDL language. By changing the bandwidth of the input video signal through low-pass filtering, the display quality of the video signal with different bandwidth can be observed on the monitor.

Key words:image filtering; low pass filtering; FPGA