设备级的高精度时间同步

2019-03-27黄华明

黄华明

【摘要】 本文介绍了在精确时间同步系统中,为实现设备与设备间高精度的时间同步而提出的一种新的接口设计方案。该方法不但大幅度提高同步精度,而且简化了硬件接口设计。此外,对于将来更高精度的升级扩展,长距离传送和强干扰环境等特定场景的时间同步应用也具备巨大的优势。

【关键词】 PTP 1PPS ToD RS422 1000BASE-X

一、引言

在PTP(Precise Time Protocol)分布式系统中,我们需要在本地设备之间同步ToD(Time of Day)并测量PTP系统的准确性。ITU-T G.703和CCSA都定义了1PPS/ToD接口,接口提供串行ToD时间信息传送和秒脉冲1PPS(One Pulse Per Second)信号作为相位指示。物理连接器采用RJ-45连接器,其电气特性符合RS422标准。

本篇文章主要阐述当前采用的RS422接口技术所具备的局限性,以及采用新型1000BASE-X接口传输1PPS/ToD原理和新设计在各项性能上的大幅提升。

二、当前的接口实现方案

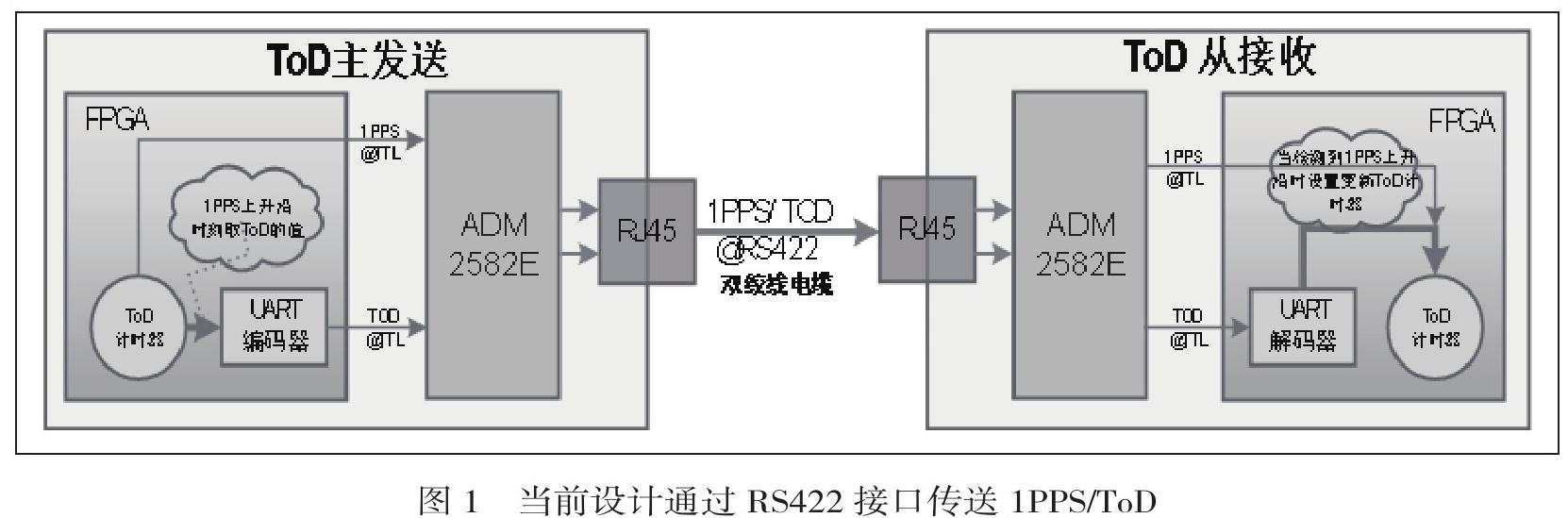

当前的1PPS/ToD接口設计符合G.703和G.8271中规定的基于ITU-T V.11的相位和时间分配接口以及相关的CCSA/CMCC标准。

外部接口采用RS422接口进行1PPS和ToD信息传输,采用RJ-45物理连接器,其电气特性符合RS422标准的要求。

FPGA引脚输出1PPS/ToD使用单端LVTTL电平。 在FPGA输出到面板接口时,电平转换芯片ADM2582E将单端LVTTL电平转换为差分422电平输出到面板。 同时,芯片将面板输入1PPS/ToD的差分422电平转换为单端LVTTL电平,并将其发送到FPGA。 具体实现框图如图1:

由于采用RS422标准1PPS/ToD接口,插入电平转换芯片ADM2582E,该电平转换芯片使得1PPS产生较大的上升时间(最大可达15纳秒),这将会引入很大的1PPS采样误差,达到数纳秒级别的误差。同时,采用不同批次的电平转换芯片ADM2582E,当转换电平时,1PPS信号延迟的差异会造成最终1PPS采样时间点的差异,严重影响采样1PPS的一致性,甚至可达到10纳秒以上的差异。

此外,即使同一电平转换芯片ADM2582E,随着温度等环境因素的变化,经过ADM2582E芯片的1PPS信号延迟也会发生变化,这也会导致最终1PPS采样时间点的差异,严重影响采样精度,误差可达数纳秒。

综上所述,采用RS422标准传输1PPS/ToD,由于物理特性和接口标准的局限性,在时间同步系统中会产生数十纳秒的同步误差,虽然可以满足早期同步系统的要求,其允许微秒或数百纳秒精度的同步误差要求。但对于目前纳秒级的高精度同步系统,这是不可接受的。

除了同步精度较差以外,使用该接口传输1PPS/ToD还不利于恶劣环境和长距离传输以及强电磁干扰等场合。同时,也很难升级扩展到更高精度的同步系统应用中。

三、改进型设计方案

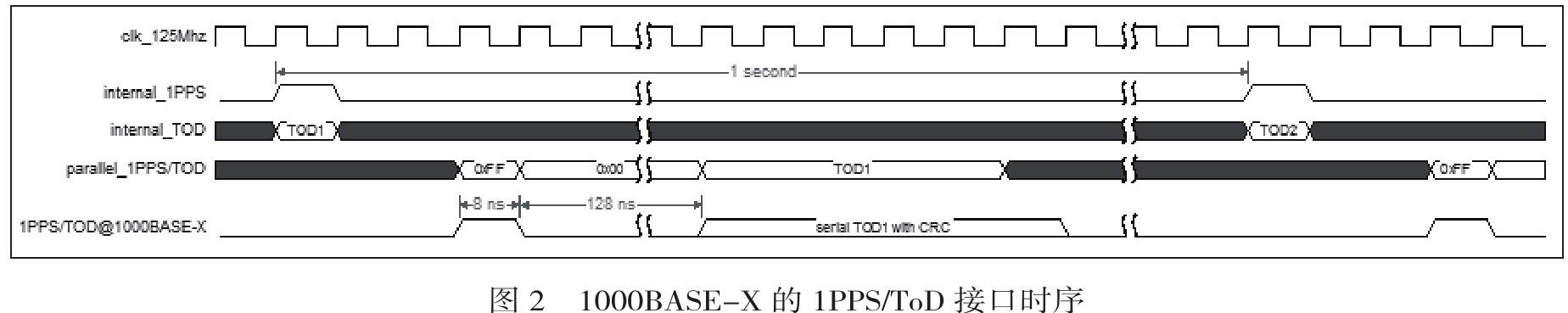

在改进型设计中,采用1000BASE-X接口,1PPS和ToD信号被组合编码为以下时序:

从图2的时序图可以看出,在空闲状态下,信号线全部为0。当PTP系统产生125Mhz的1PPS定时信号时,FPGA内部锁存当前系统的ToD时间值。ToD主发送测内部8ns宽度的125Mhz 时钟下的1PPS脉冲,在SERDES串行数据线上表现为连续输出的8个纳秒高电平。 在连续8纳秒高电平之后,插入128纳秒低电平作为间隔。在该间隔之后,80位系统时间ToD信息和8位CRC校验值按照顺序被串行编码到SERDES数据线上。

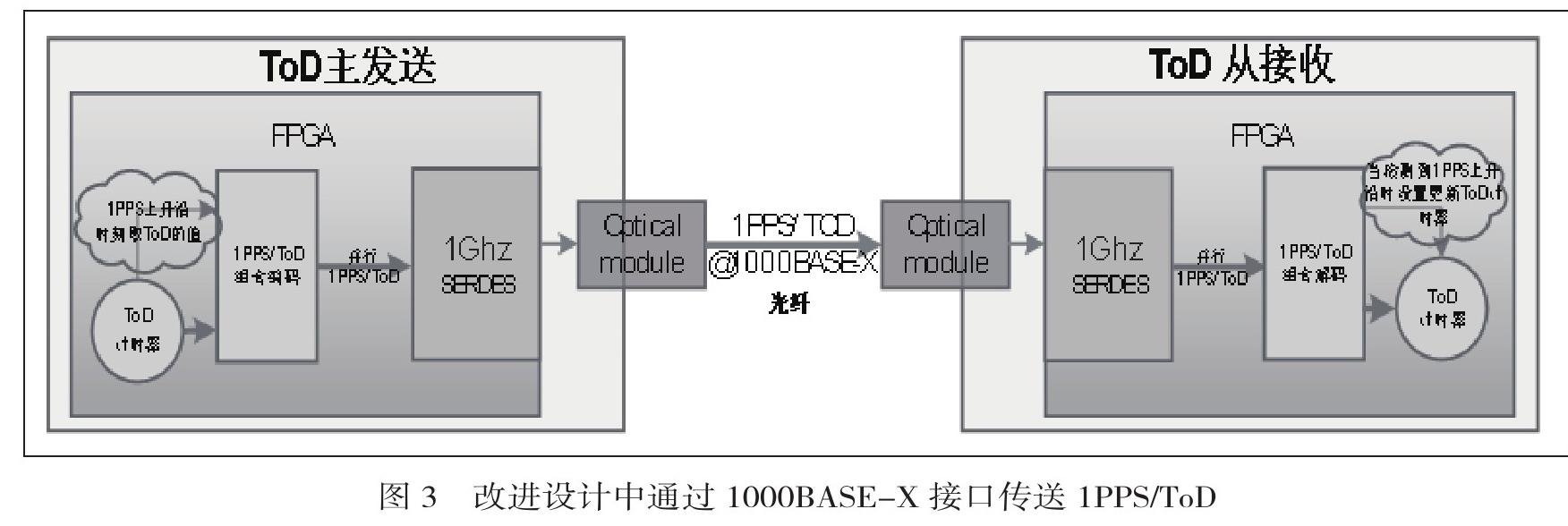

改进型设计框图如下图3:

改进设计中使用1000BASE-X作为实现的示例。在ToD的主发送侧,FPGA中的1PPS/ToD组合编码将1PPS和80位的ToD信息组合成单个串行数据线,通过FPGA内嵌SERDES硬核将数据串行化为1Ghz信号,并使用差分LVDS电平输出到光模块接口。

在ToD的从接收侧,1Ghz串行数据流被解串并行化,但未被FPGA中内嵌的SERDES硬核进行原始数据的比特流对齐。通过从前一级输入的并行1PPS/ToD,在1PPS/ToD组合解码中,通过将代表1PPS的连续8个‘1的0xFF比特对齐,来恢复后续ToD信息,并获得1PPS和接收系统采样时钟之间的相位差值phase_diff。

使用恢复的1PPS和ToD信息校准从接收侧的本地ToD计时器。更新校准时,补偿先前获得的相位差phase_diff,这样可以使同步校准精度达到1纳秒。

为了满足更高精度的时间同步要求标准,可以使用更高频率的SERDES接口。例如10G或100G,代替1Ghz接口。只要通过改变接口速率而不改变内部功能实现,就能提高同步精度至一个甚至几个数量级。因此,通过提高1PPS信号的SERDES检测精度,可以很容易地升级到更高的时间同步精度。

使用上述改进型接口设计方案,可使本地设备之间的ToD系统同步精度和PTP系统的测量精度提高一个数量级以上,并且可以提供具有更高精度的可扩展升级设计。为5G新标准要求中的超高精度时间同步提供了强有力的保证。

四、结果及分析

使用1000BASE-X千兆光纤接口代替RS422接口作为1PPS/ToD信号传输接口。千兆光模块直接连接到FPGA的SERDES引脚,将1PPS/ToD信息串行编码为单条数据线,并使用LVDS差分电平直接通过千兆光纤接口传输。

与原有RSS422接口技术相比,主要优点如下表:

五、结束语

本文所描述的通过新型传送接口实现的设计方案,将1PPS和ToD信号合二为一,降低硬件实施成本;同时采用具有可扩展工作频率的硬件接口有助于扩展到更高精度的时间同步;设计使用光信号接口代替电信号接口传送1PPS/ToD信号,可应用于更多实际场景,如长距离和强电磁干扰环境等。

参 考 文 献

[1] 中国移动高精度时间同步1PPS+ToD时间接口规范,中国移动通信有限公司发布,2010年

[2] ITU-T G.703. Physical/electrical characteristics of hierarchical digital interfaces, Apr,2016.

[3] ITU-T G.8271/Y.1366. Time and phase synchronization aspects of packet networks, Jul,2016.

黄华明,1976年9月,男,FPGA研发工程师,高级职称。长期从事固网传输芯片开发。