UCOSII在微机保护通用平台的应用

2019-01-30洪广焦

文/洪广焦

1 引言

随着智能电网标准的提出,继电保护装置向着综合化、标准化、网络化方向发展。过去,设计继电保护装置只从可靠性、速动性、选择性、灵敏性的角度设计产品。现在,因为应用场景的多样化、安装操作的标准化、数据传输的网络化,所以对微机保护装置的设计提出了新的要求。

1.1 多样化是指发电、输电、配电都出现了多种新技术,形成新的保护应用场景

如:潮汐发电,超高压直流输电,环网配电等。因此微机保护装置功能设计必须综合化,可配置。不仅要求软件可以按需配置和定制,内部硬件可以按需替换,而且要求软件二次开发周期短,硬件抗干扰强,才能适应多样化。

1.2 标准化是指安装标准化、接口标准化,操作标准化

如:不同厂家的产品安装的开孔尺寸统一、接入协议兼容、操作界面统一。因为标准化的目的是为了提高运维效率,减少投资成本。目前,以国家电网为主导的标准化产品首先在网内12kV开关柜上推开。

1.3 网络化是指微机保护的数据来源于网络,给予网络

如:实时采样数据可以来源于合并单元,保护事件和实时数据可以被多个高级应用召唤。所以网络化要求实现数据交互可靠性和低时延性。

综上可得,具备兼容性,可迭代性、可配置性、数据交互低时延性、抗干扰性已经成为微机保护设计的新指标。为了满足这些新指标设计了非应用功能分层化,应用功能模块化的微机保护通用平台。并通过引入操作系统作为应用和硬件的中间层,不仅实现了软硬件隔,而且也为应用程序模块化奠定基础。通过引入FPGA(Field-Programmable Gate Array)实现硬件模块化,从而实现多种场景无缝替换。

2 系统总体方案设计

本系统主要由应用层、系统层、驱动层、硬件层构成。应用层又可分为保护逻辑模块、人机界面模块、电力通信协议模块、数据处理模块、历史记录查询模块、装置信息模块、出厂设置模块、用户设置模块。驱动层主要分为采样驱动模块、网络通信驱动模块、开关量输入输出驱动模块、液晶显示驱动模块、编码校时驱动模块、串口打印驱动模块、串口调试驱动模块、数据存储模块。因为驱动层采用了于硬件模块映射的方式驱动自适应绑定(主要是利用外设芯片的厂家信息,自动化加载对应驱动),所以驱动模块和硬件模块的划分基本一致。因此硬件层对应划分为模拟采样电路、以太网电路、开关量电路、液晶显示电路、编码校时间电路、串口电路、存储时钟电路、电源电路(外购整体部件)。本系统以ARM+FPGA作为核心硬件平台,通过移植实时操作系统和轻量型协议栈为基础,实现分层化、模块化微机保护通用平台。

3 硬件设计

嵌入式应用平台的设计,主要包含硬件和软件量大部分,而硬件电路主要由数字电路和模拟电路组成,模拟电路主要为电源技术,采用集成模块。数字电路的核心是处理芯片。为了实现低成本且自适应多样化场景应用,故选用意法的STM32F系列微控制器。因为其有丰富的系列化,以及封装的通用性,所以电路主板设计成可根据应用场景自由选用不同档次芯片的核心模块,和自由组合的通用模块。以下以STM32F207ZET6(以下统称MCU)作为实例阐述硬件设计。系统硬件主要分5部分,即MCU最小工作系统、两片MAX11046芯片和Alteration公司的CycloneII系列的EP16C芯片组成的采样模块、用74LS138译码器实现的开入开出电路,MCU的I2C和FM31L276芯片组成的存储时钟电路模块。MCU内部集成的MAC和外部WJLXT971ALE芯片组成的网口通信模块。因采用了大量集成芯片和功能模块封住,增强了装置平台的抗干扰。本文重点阐述网口通信模块电路和采集电路。

3.1 采集电路

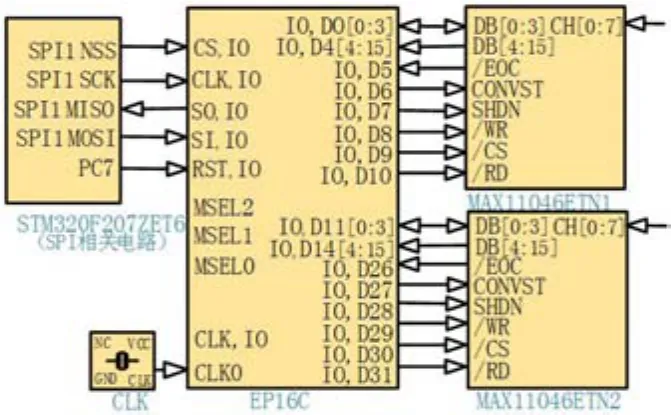

采样电路采用两片AMAX11046芯片和一片FPGA,共同组成16个独立的16位高速模拟并行采样通道。每通道均具有片内T/H电路,能实现3µs的快速转换时间,每个通道最高达250ksps吞吐率,支持多种工作模式,内部集成线性相位数字滤波器,数据输出接口支持SPI或可选帧同步,便与FPGA互联。其中,FPGA内置EPROM存储器,上电时,把EPROM中的电路逻辑规则复制到片内RAM中,随后FPGA进入工作状态。FPGA通过修改内置EPROM存储器上的逻辑,能够反复使用。FPGA的编程通过QuartusII编程器,对通用的EPROM、PROM编程。当需要修改FPGA功能时,通过不同的编程实现电路功能。因此,FPGA的使用非常灵活。采样电路原理图如图1所示。

3.2 通信电路

以太网通信电路主要有三部分组成,介质访问控制器(MAC)、外接物理层(PHY)和集成变压器。因(MCU)自带MAC,同时支持媒体独立接口(MII)和媒体简化独立接口(RMII),本文采用了MII接口和美光科技公司的LXT971ALE芯片连接以便实现多PHY的控制。所以外部电路只需提供PHY和变压器(13F-66YGD4NL自带RJ45接口)。原理图如图2所示。

MCU的MAC和PHY连接主要有三部分组成。

(1)通过MCU和PHY的DMIO和DMC连接主要用来配置PHY和实时监视PHY运行状态;

(2)MAC的 RX[0:3]和 TX[0:3]分 别于对用的PHY链接作为数据收发通道。RX _CLK和TX_CLK组成的收发数据的时钟,时钟来自PHY25MH晶振分频得到;

(3)MAC和PHY传递的数据包通过直接内存访问器(DMA)实现数据先进先出交互处理。同时一个MAC可以通过不同的PHY地址(ADDR[0:4]),实现多个PHY连接。

4 软件设计

uC/OS-II是一款小巧但功能强大的嵌入式实时操作系统内核,它的主要特点就是源代码开放、硬件资源要求低、程序执行时间确定,应用于继电保护装置中可以充分隔离驱动和应用代码实现非应用程序分层设计,应用程序模块化封装。它采用任务调度,CPU使用更为合理。传统的前后台程序设计,不仅对芯片的硬中断依赖性强,而且难已对程序实现模块化封装,更不能实现分层化开发,代码重用率低。而实时系统的引入,解决了以上难题,同时uC/OS-II广泛应用于工业控制领域,通过了非常严格的测试标准,并得到了美国军方的认证。可见其内核是非常稳定的,而其开源方便企业对核心技术的把控,同时也方便对内核的优化和改进。

4.1 UCOS-II系统移植和任务改进

因V2.89版本的UCOS-II操作系统只支持64个可剥夺中断优先级任务配置,为了实现同一优先优先级任务的轮询机制,也为了减少任务切换造成不必要的资源开销。采用了相同任务优先级里放调用两个应用程序,通过标志实现两个应用程序的轮训调用。通过修改 OS_CPU.C、OS_CPU.H和 OS_CPUA.AS源代码文件实现10MS任务调度。移植系统主要分四步,第一步实现操作系统时间节拍与芯片的中断地址关联,系统挂起中断地址和芯片挂起中断函数关联。第二步通过系统节拍中断服务函数OSTickISR()配置任务调度时间。第三步初始化系统函数OS_Init(),通过OS_CPU_SysTickInit()初始化系统时钟,并通过OSTaskCreate()函数创建不同应用模块的任务,通过参数设置给不同的应用模块分配合适的堆栈大小,优先级等。第四步任务间通过互拆量实现任务同步和资源管理。最后通过OSStart()函数启动系统调度运行系统和应用函数。

4.2 LWIP移植

平台采用了V1.3.2 的Light-Weight-IP(LwIP)协议栈。它是一种小型开源TCP/IP协议栈,一般它只需要几十K的,40KB左右的ROM和十几KB的RAM就可以正常运行,这使得LwIP协议栈在中低端的嵌入式系统中有着广泛的运用。修改lxt971ale_Init ()函数完成PHY初始化,并配置和MCU的对接,实现链路数据的读取,因片MCU自带MAC,所以采用了专用DMA的方式读写PHY内的数据包。配置LwIP_Init()函数实现协议栈的内存分配和mac地址,IP地址的初始化;用HelloWorld_init()初始化TCP协议。通过操作系统开设LwIP_Periodic_Handle()任务进程,5mS更新一次lwip的一些状态,并用ETH_CheckFrameReceived()查询是否有新的数据包要收发,通过消息方式通知LWIP处理程序LwIP_Pkt_Handle(),唤醒处理程序马上处理数据包,并输出给对应的应用程序接口缓存。

图1:采样电路原理图

图2:通信原理图

5 结论

通过充分利用ARM和FPGA的各自优势,设计一种基于分化,模块化的架构的微机保护通用平台,解决了传统设计的硬件复杂度和软件代码重用性低的缺陷。从而实现ARM的微机保护平台的多场景应用。而可变成的FPGA并行处理能力给MCU的资源减轻了数据读取,GPIO不足的等难题,为未来扩展提供了基础。实验结果证明这是一种高效可行的平台设计。