高场应力下晶格匹配 In0.17Al0.83N/GaN HEMT退化研究

2019-01-12

(淮阴师范学院计算机科学与技术学院,江苏淮安 223300)

相较于传统窄禁带半导体器件,由宽禁带半导体GaN制备的AlGaN/GaN高电子迁移率晶体管(HEMT)适合在高温、高压与高频等极端环境下工作[1-3]。随着材料生长和微加工技术的发展,AlGaN/GaN高电子迁移率晶体管的性能不断获得突破。但是,由于AlGaN与GaN材料之间存在较大的晶格失配,AlGaN/GaN异质结中存在逆压电效应,当压电应力达到一定程度时晶格会产生应力形变,从而产生新的缺陷,造成器件损坏[4-5]。为了消除逆压电效应,在GaN衬底上直接生长与其晶格匹配的In0.17Al0.83N外延层的方法被提出[6]。该方法另一大优势是InAlN势垒层较强的自发极化效应,能够提供更高的二维电子气浓度,使得晶格匹配In0.17Al0.83N/GaN异质结在微波和高频应用方面具有很大的发展潜力,也成为近年来研究的热点[7-8]。尽管InAlN和GaN势垒层不存在逆压电效应,但是InAlN材料生长质量还不高,器件可靠性仍然面临一定的威胁。在本文中,一种由InAlN势垒层高缺陷密度引起的晶格匹配In0.17Al0.83N/GaN HEMT退化被发现,该退化主要引起器件的饱和漏电流(IDsat)和跨导峰值(gm)降低,并使阈值电压发生正向漂移。经过分析认为,该退化是由沟道热电子的俘获和去俘获过程导致的。

1 器件制备与测试

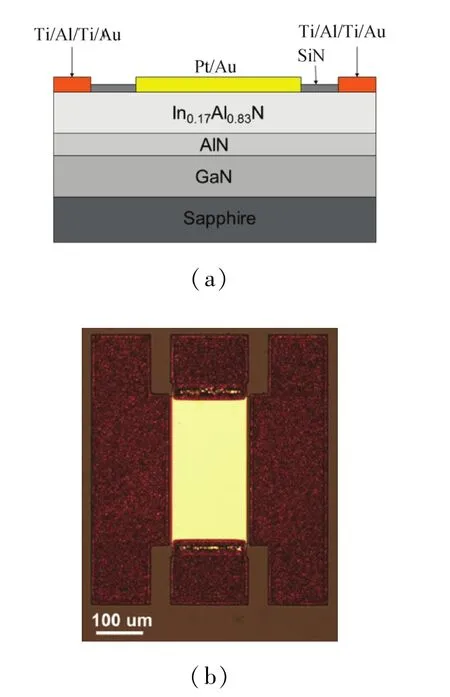

图1(a)和图1(b)所示分别为晶格匹配In0.17Al0.83N/GaN HEMT的结构示意图和器件平面照片。其中,GaN外延片(约3 μm)是通过金属有机化合物气相沉积法(MOCVD)在蓝宝石衬底上生长的。In0.17Al0.83N/GaN异质外延结构主要包括3 μm非掺杂GaN层、18 nm非掺杂In0.17Al0.83N势垒层、1 nm AlN隔离层和150 nm SiN钝化层。器件的欧姆接触采用电子束蒸发Ti/Al/Ti/Au后在800℃氮气中快速热退火60 s获得,栅肖特基接触采用电子束蒸发Pt/Au(50/300 nm)形成。器件栅长为100 μm,栅宽为200 μm,栅极处于源漏电极中央,栅源和栅漏间距均为5 μm。

图1 晶格匹配In0.17Al0.83N/GaN HEMT:(a)结构示意图和(b)器件平面照片Fig.1 Lattice matched In0.17Al0.83N/GaN HEMT:(a)structural schematic diagram and(b)optical micrograph

2 实验结果与分析

首先,对器件基本电学参数进行了测试,其中,击穿电压约为42 V,阈值电压(VTH)约为4.5 V,跨导峰值(gm)约为0.05 S,饱和漏电流(IDsat)约为0.23 A。

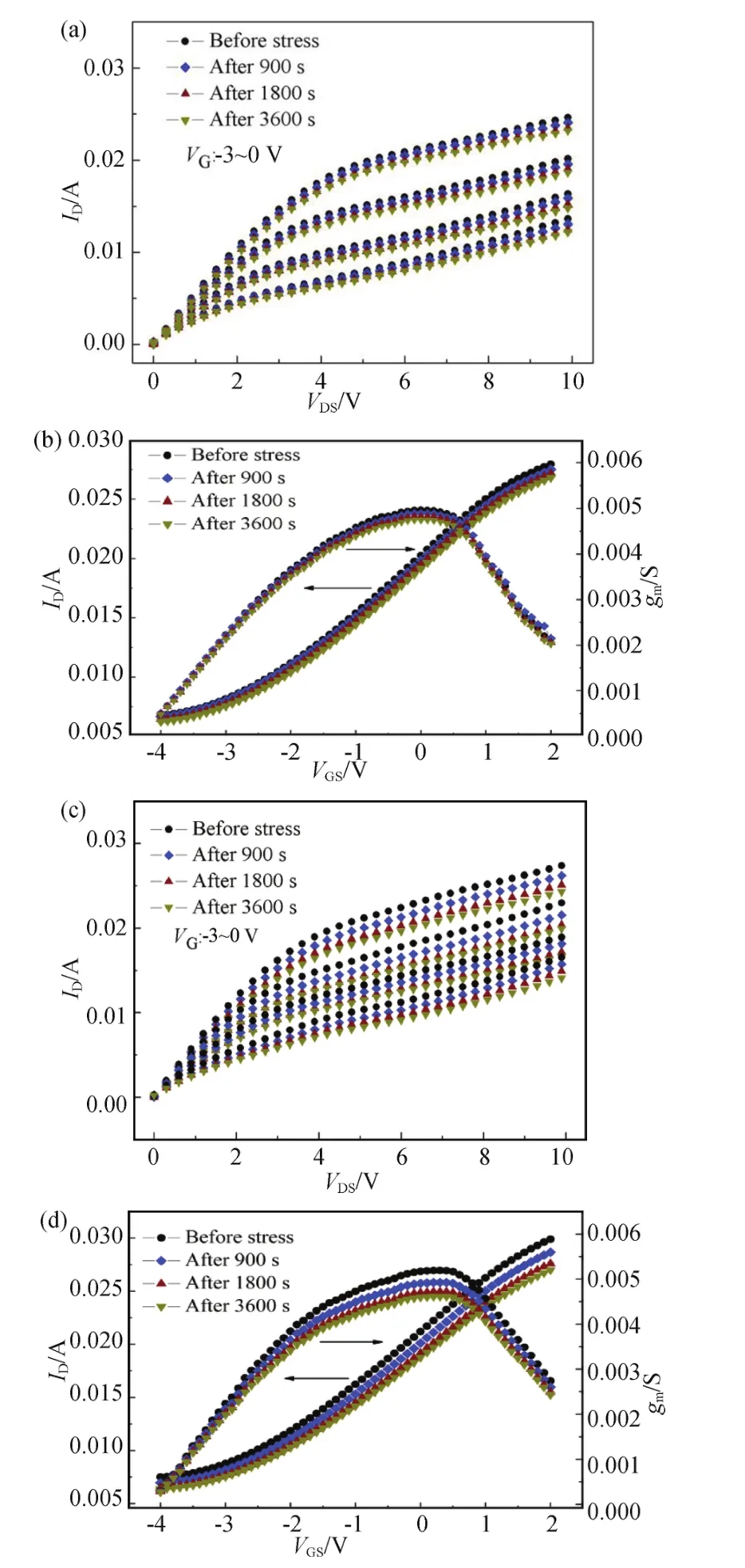

图2所示为晶格匹配In0.17Al0.83N/GaN HEMT器件在不同源漏应力 (VDS)前后输出特性曲线,其中图2(a)和图2(b)为VDS=10 V(VG=0 V)前后的输出和转移特性曲线,图2(c)和图2(d)为VDS=20 V(VG=0 V)前后的输出和转移特性曲线,应力持续时间分别为900,1800和3600 s,输出特性栅压由-3 V至0 V(反向),测试间隔1 V,转移特性测试电压为VDS=6 V。可以看出,持续VDS应力使HEMT器件的输出和转移特性产生退化,主要表现为IDsat和gm峰值降低,阈值电压发生正向漂移。通过比较VDS=10 V和VDS=20 V应力下的退化程度,可以发现应力越高,退化程度越明显。根据图2(a)和2(b),计算经过3600 s的10 V源漏应力后,IDsat下降了约5.8%,gm下降了约4.4%。根据图2(c)和2(d),20 V源漏应力后,IDsat下降了约11.3%,gm峰值下降了约11%。当应力时间超过3600 s后,基本不再退化。综上可知,-10 V源漏应力对器件输出和转移特性影响相对较小,但-20 V源漏应力对器件性能产生了明显的影响。为了提高晶格匹配In0.17Al0.83N/GaN HEMT工作的可靠性,分析源漏应力后器件性能退化的具体机理很有必要。

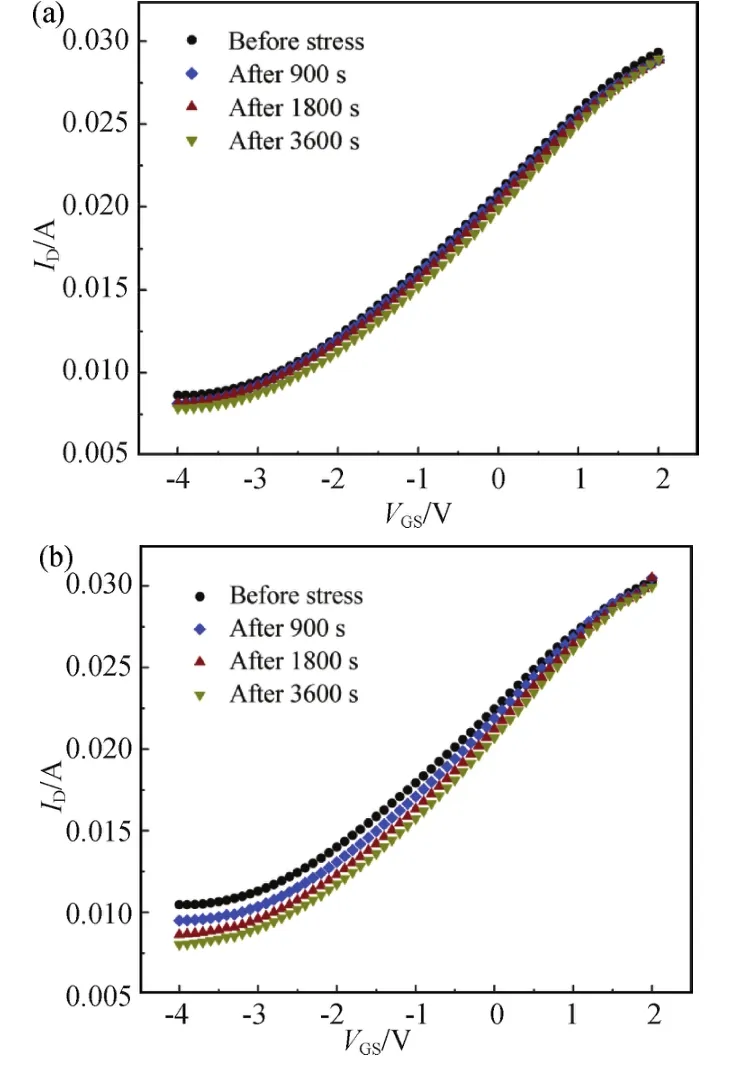

在GaN基HEMT中,器件退化主要与大信号工作状态的强电场有关,通常情况下,失效机理主要有沟道热电子注入、逆压电效应和栅极电子注入等[9]。由于晶格匹配In0.17Al0.83N/GaN HEMT异质界面实现晶格匹配,避免了压电应力,因此基本可以忽略逆压电效应产生的影响。为了判断沟道热电子注入和栅极热电子注入对器件退化的影响,分别在源端悬空和栅端悬空的情况下对器件施加应力(悬空指该端不接探针)。源端悬空时,应力条件为VD=20 V,VG=0 V;栅端悬空时,应力条件为VD=20 V,VS=0 V。在相同时间高场应力后,对器件转移特性进行测试。图3所示分别为(a)源端悬空和(b)栅端悬空下,应力前后测得的HEMT转移特性,应力持续时间分别为900,1800和3600 s。可以看出,源端悬空后,器件转移特性退化相对较小,而栅端悬空后,器件转移特性仍然发生明显退化。经过计算,当源端悬空3600 s时,IDsat下降了约4.8%,VTH漂移约5.7%;然而当栅端悬空时,IDsat下降了约23.3%,VTH漂移约20.8%。比较这两种不同应力下的退化,不难确定退化过程中,电子主要是来源于沟道碰撞电离产生的热电子。

图2 不同源漏应力下的输出特性和转移特性退化:(a)10 V前后的输出特性;(b)10 V前后的转移特性;(c)20 V前后的输出特性;(d)20 V前后的转移特性Fig.2 Degradation of output characteristics and transfer characteristics under different source-drain stresses:(a)output characteristics after 10 V;(b)transfer characteristics after 10 V;(c)output characteristics after 20 V;(d)transfer characteristics after 20 V

图3 转移特性退化:(a)源端悬空;(b)栅端悬空Fig.3 Degradation of transfer characteristics:(a)source floating;(b)gate floating

沟道热电子注入过程中,退化通常和材料中存在的缺陷有关,下面将分析究竟哪种缺陷在退化过程中起主要作用。高场应力后,在晶格匹配In0.17Al0.83N/GaN HEMT中可能影响器件退化的因素主要有以下几个:InAlN势垒层陷阱;表面态;异质结界面态[10]。其中,只有InAlN势垒层的陷阱才能明显影响VTH,而由异质结界面态缺陷引起的退化,通常是不可恢复退化。

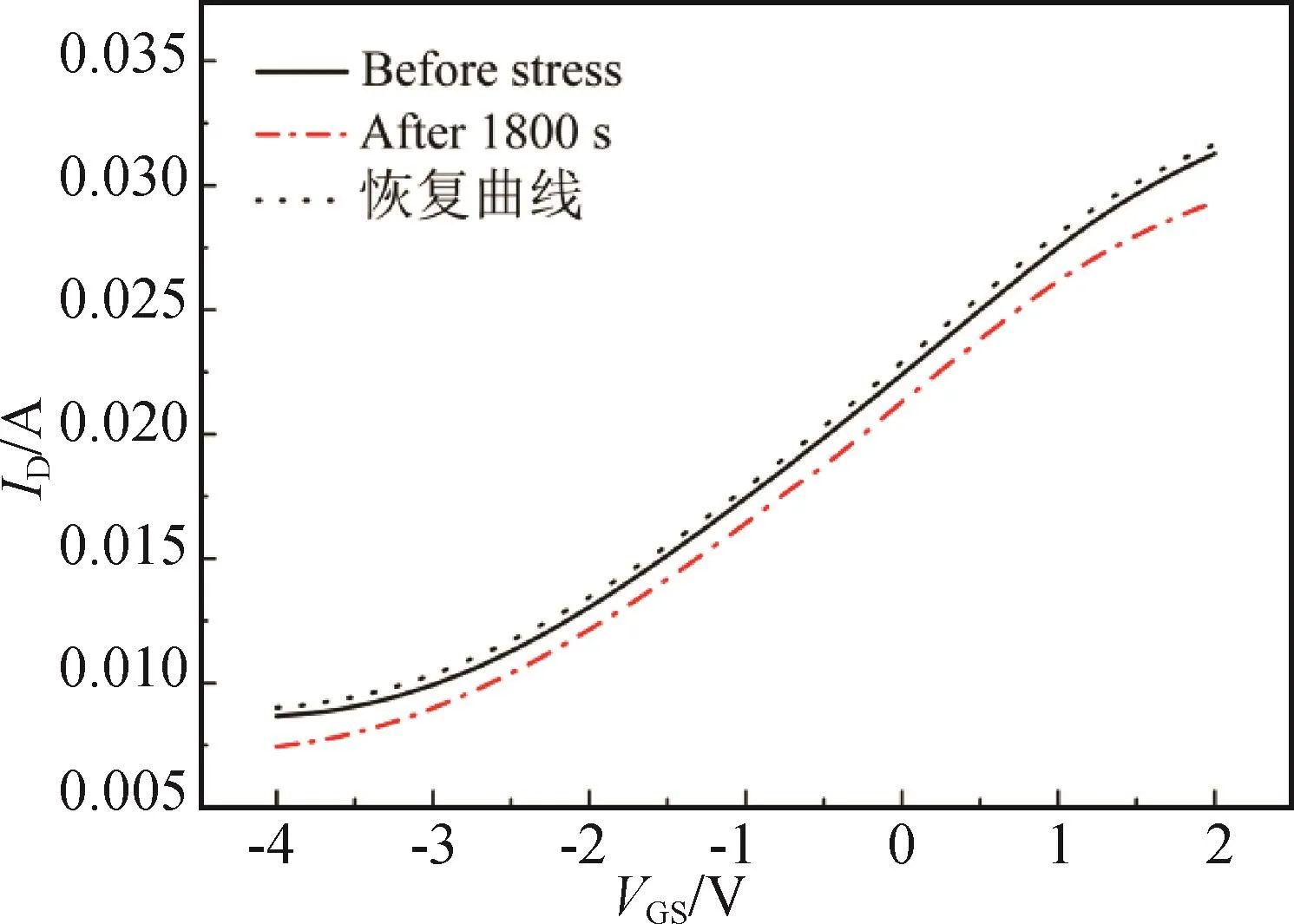

为了分析参与退化的主要缺陷,对器件施加源漏20 V应力(VG=0 V),持续时间1800 s,然后撤掉源漏应力并将已退化样品放置一段时间后,测得的转移特性和恢复特性曲线如图4所示。其中,黑色实线为应力前器件转移特性,红色虚线为应力后转移特性,黑色虚线为恢复转移特性。可以发现,器件转移特性完全恢复了,表明该退化是可恢复的。由于异质结界面态引起的退化往往是永久退化,所以可以排除界面态的影响。另外,由于只有InAlN势垒层的陷阱才能明显影响VTH,而表面态对其几乎没有影响,考虑到退化过程中VTH也会退化,因此栅下InAlN势垒层的陷阱是退化主要原因。另有研究表明,填充表面态的电子大多来自栅电子[11],而本退化中,退化主要与沟道热电子相关,因此表面态参与退化的可能性较小。

图4 晶格匹配In0.17Al0.83N/GaN HEMT的转移特性和恢复特性曲线Fig.4 Transfer characteristics and recovery characteristics of lattice matched In0.17Al0.83N/GaN HEMT

根据上述实验结果,本文提出由沟道热电子填充InAlN势垒层缺陷的退化物理机制可用以解释晶格匹配In0.17Al0.83N/GaN HEMT的退化。当给器件施加一个较大的源漏应力,由于横向电场加速,沟道中大量热电子形成源漏电流。由于InAlN势垒层中存在高密度缺陷,应力持续过程中,沟道热电子逐渐被InAlN势垒层缺陷俘获,导致IDsat和gm降低。当材料中大部分固有缺陷均俘获电子,器件逐渐不再退化。当器件源漏应力被撤去以后,经过一段时间,被缺陷俘获的电子被释放,器件性能逐渐恢复。因此该退化过程,可认为是一个沟道热电子被缺陷俘获和去俘获过程。该退化现象,对晶格匹配In0.17Al0.83N/GaN HEMT工作的可靠性和稳定性都有影响,为了抑制该退化产生的影响,提高InAlN势垒层质量,降低InAlN势垒层缺陷密度将是抑制该退化的重要途径。

3 结论

本文首先制备了晶格匹配In0.17Al0.83N/GaN HEMT,然后基于源漏应力测试发现当VDS较高时,器件IDsat和gm出现明显降低,VTH正向漂移。根据源、栅悬空退化比较和退化恢复特性,提出一个由InAlN势垒层缺陷俘获沟道热电子导致退化的机制,该机制有助于提高器件工作可靠性和商业化应用。