基于FPGA的CPCI-CAN通信卡电路设计

2019-01-12戴宏睿李文魁阮嘉伟

戴宏睿李文魁阮嘉伟

(1.海军工程大学电气工程学院,武汉,430033;2.东部战区海军保障部,宁波,315100)

20世纪90年代发展起来的PCI总线作为计算机的行业标准,具有支持多种处理器、优异的并行操作能力、即插即用等特点[1],但在工业控制、军工等可靠性实时性要求较高的场所,暴露出连接不可靠、抗干扰能力差、抗震性差等问题。紧凑型PCI总线(Compact PCI)是PCI总线的电气和软件标准与欧式板卡机械结构的结合。电气接口上增加了一部分故障检测、系统管理、热插拔等总线信号;机械结构上摒弃了原有的金手指连接方式,采用高密度、气密性针孔连接器,连接可靠。

控制器局域网(Controller Area Network,CAN)是20世纪90年代发展起来的现场串行总线。相比于RS485等传统总线,CAN总线采用不分主从的多主方式,通信实时性高;传输距离更远、传输速率更快;采用非破坏性总线仲裁技术,抗电磁干扰性好[2];使用短帧数据结构,容错性高。本文设计旨在开发基于CPCI总线的CAN通信卡,满足工业、军事应用环境下的自动化测控系统应用需要。

1 总体设计

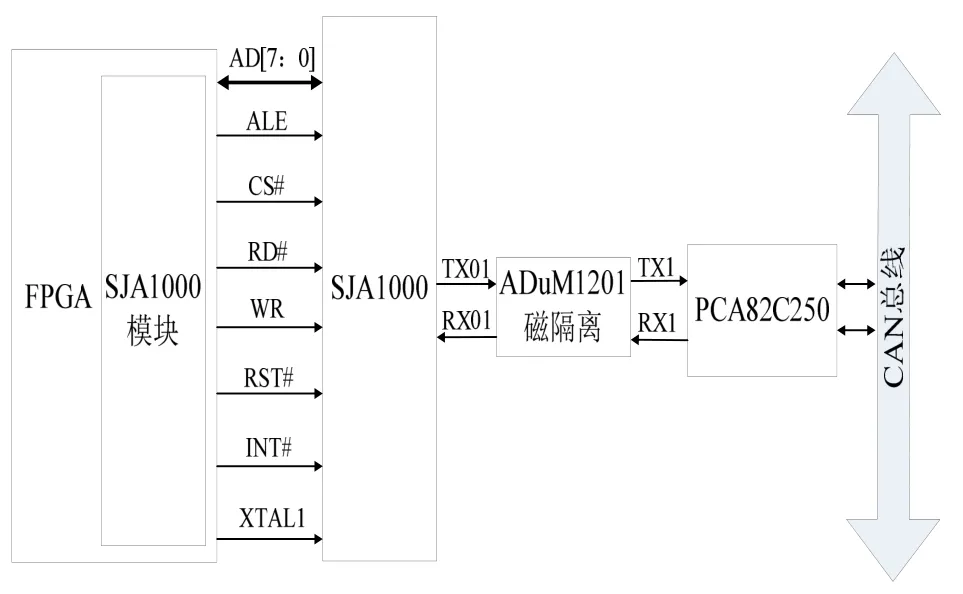

拟设计的CPCI-CAN通信卡电路组成如图1所示,主要参数为:3U规格(100 mm×160 mm),2通道隔离CAN接口,DB9接口,支持CAN 2.0B规范,最高波特率1 Mbps,电气隔离DC 2 500 V。电路主要包括CPCI接口电路、主控电路、CAN通信电路。CPCI接口电路负责接收上位机的指令,CAN收发电路用于执行指令,完成数据和地址的收发,主控电路负责控制数据传输速率。

图1 CPCI-CAN通信卡电路组成框图

CPCI接口实现一般有两类方案[3],一是采用FPGA等可编程逻辑器件实现接口逻辑,但 CPCI总线协议及时序控制复杂,开发难度较大;二是采用专用接口芯片,此时不用考虑逻辑的时序匹配等。本文采用第二种方案,选用PLX Technology公司的PCI9030接口芯片实现,它具有可编程通用I/O,兼容PCI r2.2规范,并将CPCI总线信号转化为本地总线信号。

主控制器件的选择有多种方案:或是采用单片机、ARM、DSP等微处理器;或是采用可编程逻辑器件,如 CPLD和 FPGA等。现场可编程门阵列FPGA是在PAL、CPLD基础上发展起来的,相比单片机、ARM 等微控制器,在不更换硬件条件下可灵活方便地升级,开发时间短。本设计采用FPGA实现主控电路功能,具体选用 Xilinx公司的XC2S200。它具有低功耗高级CMOS NOR闪存工艺和适用于标准FPGA配置的JTAG初始化命令。

CAN总线控制器实现有多种方案:一是选用集成CAN控制器的微控制器,如单片机、DSP、ARM等;二是选用独立的CAN控制器;三是通过FPGA等实现CAN控制器功能[4]。本设计选用独立CAN控制器SJA1000,可靠性高,开发效率高。

2 电路设计

2.1 CPCI接口电路

2.1.1 组成及功能

CPCI接口电路实现CPCI总线与本地总线的时序转换、协议转换和数据传输。如图2所示,CPCI总线接口信号包括上位机控制信号、数据地址等,这些信号经 PCI9030转换为本地总线信号,进入FPGA的 PCI9030接口模块。其中,MODE引脚置低规定PCI9030为非复用模式。

图2 PCI9030接口电路图

2.1.2 CPCI本地总线信号

CPCI本地总线信号及含义为:ADS#(地址起始)、BLAST#(传输结束),分别控制总线数据传输开始和结束。本地地址信号LA[27:2],通过LBE[3:0]使能。非分时复用数据总线 LD[31:0]用来传递 32位PCI数据。PCI9030作为主设备时,通过LW/R#控制本地总线数据的写/读。RD#和 WR#实现PCI9030的读输出和写输出。本地中断输入 LINTi用于触发中断。基地址片选信号 CS0#、CS1#使能本地总线上相应设备,并设定总线地址范围。LRESETo#用于在复位输入 RST#有效时输出本地复位信号。

2.1.3 PCI9030配置电路

PCI9030的初始化通过EEPROM配置实现,包括工作模式、数据地址空间及设备ID等。EEPROM选用93LC66B,3.3 V供电。将93LC66B的CS(片选)、SLK(时钟)、DO(数据输出)及 DI(数据输入)与PCI9030对应引脚相连。ORG置1选择16位数据传输模式。DO需要外接上拉电阻,配合 PCI9030的复位下拉信号 RST#,上电时可在 PC端对EEPROM进行在线烧写。

2.2 FPGA主控电路

如图3所示,主控电路由XC2S200 FPGA及其辅助电路组成,包括24 MHz晶振、电平转换(5 V-3.3 V、5 V-2.5 V及FPGA配置电路等。其主要功能为:通过CPCI总线接收上位机传来的信息,处理后产生各种控制信号,实现 CAN总线和上位机之间按规定的时序逻辑进行数据传输;通过访问 CAN控制器实现对 CAN总线的控制,并对两端总线传输过来的数据进行缓冲和锁存。

图3 主控电路

XC2S200 FPGA是基于RAM的,掉电后程序丢失,配套的需选用专用系统可编程PROMS平台闪存存储FPGA内部网表信息,工作时再将其加载到FPGA上。根据Xilinx的FPGA配置芯片匹配表,选择XCF02S作为配置芯片,它具有标准FPGA配置的JTAG初始化命令。配置电路见图4。

图4 XCF02S配置电路

FPGA配置可采用主串行模式或从串行模式。本设计使用FPGA主串行模式。该模式下时,FPGA产生时钟由CCLK输出驱动PROM,将CF#置高,并使能CE#、OE,数据将在时钟上升沿传输。

FPGA TDO将其内部网表信息传输至XCF02S。在配置时,控制信号和同步信号通过TDO发给配置芯片 XCF02S,其收到指令后,通过数据输出引脚D0输出网表信息至FPGA的DIN。来自PC端的程序通过JTAG TDO直接对FPGA进行烧写。

2.3 CAN通信电路

在FPGA控制下,CAN通信电路实现CAN消息帧的接收和发送,其中CAN控制器SJA1000和CAN收发器PCA82C250分别实现CAN协议的数据链路层功能和物理层功能。

如图5所示,SJA1000与FPGA的连接信号主要包括:AD[7:0](数据地址复用);读写控制信号 RD(读)、WR (写)、ALE(锁存)、INT#(收发中断使能);来自FPGA的时钟输入XTAL1。

图5 CAN通信接口电路图

采用双通道数字磁隔离器 ADuM1201实现CAN控制器与收发器之间的电气隔离。隔离电路如图6所示。

图6 CAN通信磁隔离电路

3 逻辑设计

FPGA开发可采用Verilog HDL、VHDL等多种硬件描述语言。Verilog HDL简洁易懂,应用广泛。本文在Xilinx ISE10.1集成开发环境下采用Verilog HDL语言进行板卡的FPGA逻辑设计。

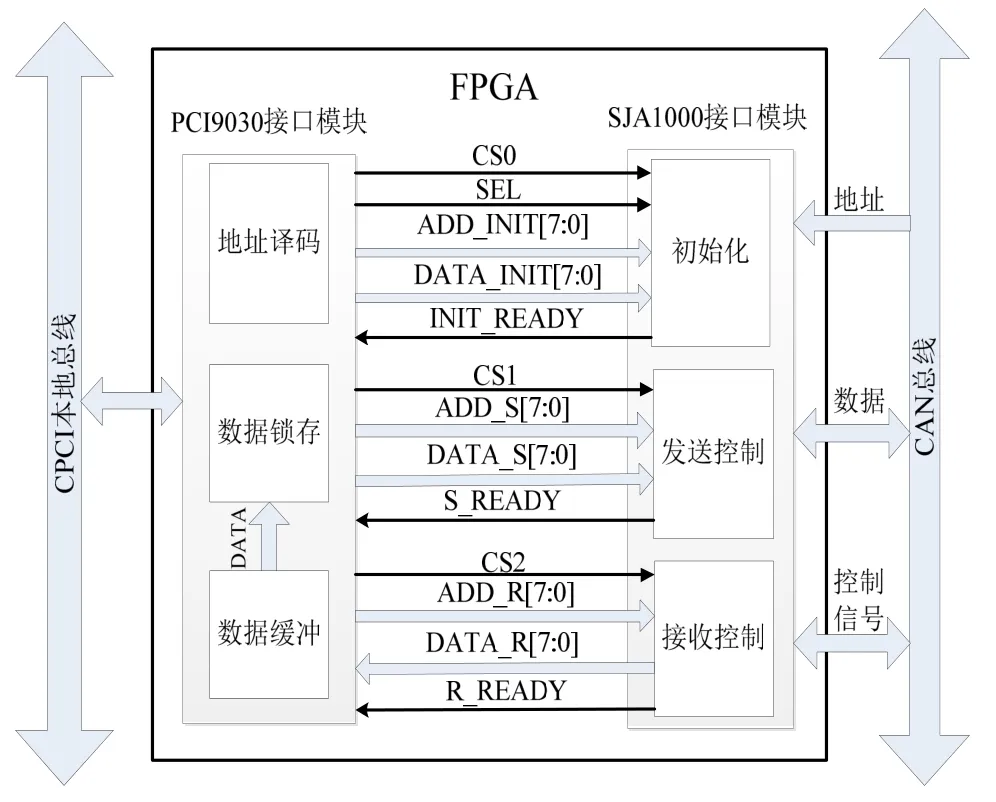

3.1 逻辑模块组成

FPGA内部逻辑可分为PCI9030接口模块和SJA1000接口模块两个功能模块。前者包括地址译码、数据锁存和数据缓冲子模块,实现与CPCI总线的数据交互;后者包括初始化、发送控制和接收控制等子模块,实现CAN总线数据通信。FPGA内部逻辑如图7所示。

图7 FPGA内部逻辑

上电后,应首先完成SJA1000和PCI9030的初始化。接收数据时,SJA1000接口模块接收来自CAN总线数据,通过接收控制单元进入数据缓冲区,发送给PCI9030接口模块,经由PCI9030传递到CPCI总线到达上位机。发送数据时,上位机发送指令,经PCI9030接口模块地址译码后,将数据地址锁存。进入SJA1000接口模块数据缓冲区,待先前数据发完后,通过发送逻辑将数据送至SJA1000往外发送。

PCI9030接口模块负责将传来的上位机发送或接收命令信号进行译码,使能(CS[2:0])SJA1000的各子模块和CAN通道选择(SEL)等。锁存来自上位机或 CAN总线的数据地址,并提供接收数据时的缓冲空间。

3.2 SJA1000接口模块设计

FPGA要实现对SJA1000的控制,主要是对其寄存器进行操作,包括初始化、发送控制及接收控制。FPGA的控制命令是通过写使能 WR、读使能RD、锁存ALE及片选CS等操作实现对寄存器的读写。

SJA1000接口模块的主要工作流程为:接收到发送或接收指令后,向SJA1000发送初始化指令,待发送/接收的数据进入 SJA1000接口模块中的发送接收控制子模块。同时各子模块准备好后将READY信号返回上位机。

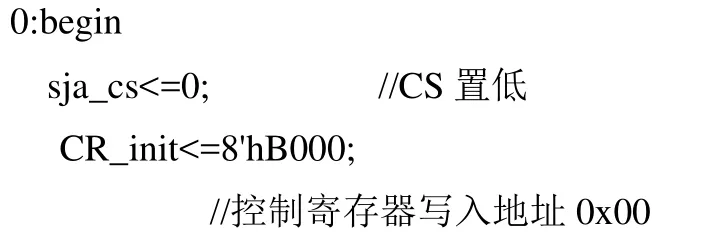

3.2.1 初始化逻辑

仿真开始时,设置各信号初值为0。分别对控制寄存器赋值0x01和0x06,完成置位复位请求和发送中断使能。下面给出部分代码及含义。

SJA1000初始化操作时序如图8所示。通过对总线定时寄存器(BTR0和 BTR1)赋值来设置总线波特率。16 MHz晶振,波特率125 kbps,则BTR0和BTR1分别赋值0x03和0x1c。置位命令寄存器(CDR)设置CAN模式。

图8 CAN控制器初始化仿真

3.2.2 发送控制逻辑

发送前,检测是否有数据等待发送,即读取SJA1000状态寄存器值是否为“0D”,若是,表明发送缓冲区空闲。若不满足,赋值“0E”给控制寄存器,清空发送缓冲区,再读取状态寄存器值,循环超过3次即发送请求失败。发送控制流程如图9所示。

图9 发送控制流程图

部分发送代码如下:

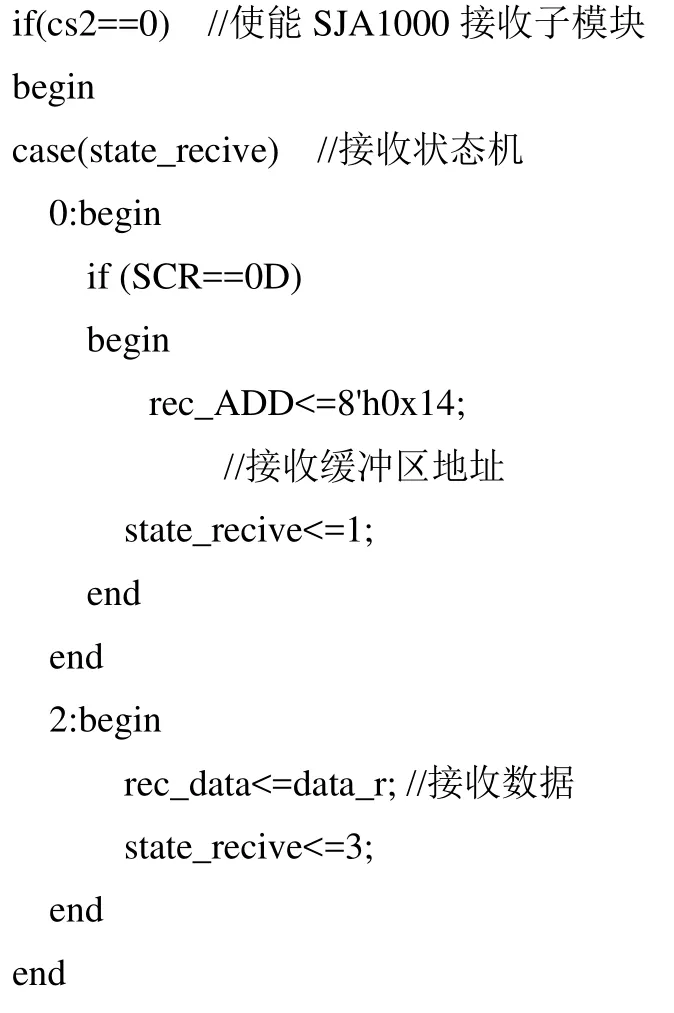

3.2.3 接收控制逻辑

板卡收到上位机“接收”指令后,SJA1000接收模块接收PCI9030接口模块的发送使能信号,然后读SJA1000状态寄存器,判断是否满足接收条件。若满足,置位命令寄存器将SJA1000接收缓冲区的数据发送至PCI9030接口模块的数据缓冲子模块。接收控制逻辑对应的主要代码如下:

4 测试与结论

如图10所示,将CPCI-CAN通信卡插入神州飞航CPCI 6U工控机BST71004,通过USB-CAN转接器与 PC连接。PC端运行 CAN测试软件CANTest。总线波特率分别设置为125 kbps、500 kbps和1 000 kbps,CAN数据帧采用扩展帧,对板卡进行 CAN数据收发的通信速度测试和正确性测试。结果表明,该CPCI-CAN通信卡能在CPCI总线计算机上以最高1 Mbps的波特率实现CAN总线数据的正确传输,通信可靠,工作稳定。

图10 板卡通信测试连接图

本文设计的CPCI-CAN通信电路以FPGA为核心进行开发,消除了传统 CAN通信电路可能存在的信道堵塞等问题,具有可靠性高、抗干扰能力强、便于后续升级的优点。该CPCI-CAN通信卡在工业及军事领域具有广泛的应用前景。