基于FPGA的Intel-8080总线实现研究

2019-01-06夏云超

夏云超

摘 要:高速信号处理系统基本围绕DSP与FPGA设计实现解决方案,FPGA具有并行速度高、处理能力强、扩展性强、可用于ASIC设计的优势,然而FPGA硬件解决方案在实现低速外设、用户界面、用户交互方面相较于嵌入式软件解决方案开发周期长、开发人员少、公共开发资源少。因此,基于FPGA与MCU的联合解决方案能有效集合上述优点,具有良好的应用前景,但是需要一种FPGA与MCU的稳定、通用的通信接口设计。文章提出的MCS-8051系列单片机是广泛使用的MCU平台,内部集成有Intel-8080总线控制器,故FPGA可以设计一种兼容Intel-8080总线协议的通信接口以实现MCU与FPGA的通信。

关键词:高速信号;单片机;现场可编程逻辑门阵列

1 Intel-8080总线的实现

MSC-8051系列处理器采用Intel-8080外部总线与外部扩展内存通信,现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)与单片机接口可按照Intel-8080总线规范设计,模拟为总线上的外部扩展内存,使单片机可使用扩展内存访问指令向FPGA传输数据(MOVX @DPTR,A)或从FPGA获取数据(MOVX A,@DPTR)。

如图1所示,ALE为地址锁存信号,高电平有效;WR为数据写入信号,低电平有效;RD为数据读取信号;P0为总线地址bit7~bit0与总线数据bit7~bit0复合信号;CLK为FPGA全局时钟,RST为FPGA全局复位;其余信号输入输出线为映射到总线上的寄存器。

作为总线从设备,FPGA应实现当单片机发出读取请求时把对应地址的寄存器值输出到总线上,当单片机请求写入时把对应地址寄存器按总线内容赋值。

由于此设计中使用的总线地址不大于256个,因此可使用8位地址线,高8位地址线可不接,以节省板面空间。

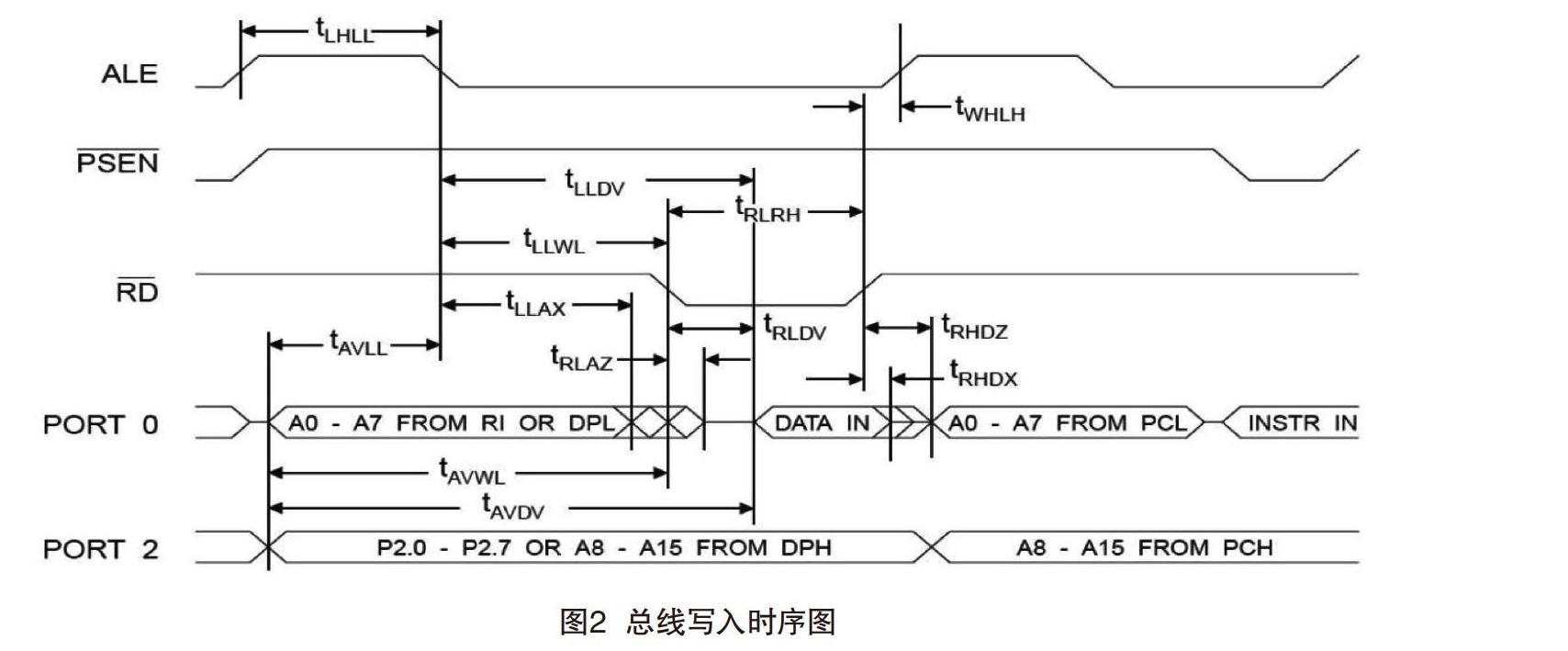

2 读取时序实现

参考Intel-8080总线读取时序图,设计读取控制电路,满足时序要求。如图2所示,ALE由总线主机提供(单片机),读取数据时主机首先拉高ALE,同时主机于P0与P2输出16位地址。ALE高电平持续tLHLL时间后,主机拉低ALE信号,此时从机收到ALE低电平,锁存地址总线信号。经过tLLWL时间后,主机拉低RD信号,并高阻P0接口。当总线从机(FPGA)收到RD低电平信号时,从机根据锁存的地址寻址映射表,将对应寄存器数据读出,于總线P0上输出。经过tRLRH时间后,主机拉高RD信号,从机收到RD高电平时,高阻P0。经过这一时序,单片机可使用一条MOVX A,@DPTR指令从FPGA读取1个字节指定数据。

FPGA的实现方法为:

(1)使用ALE为时钟线控制8位D触发器,锁存地址信号。

(2)使用锁存后的地址信号控制数据选择器(MUX)选通寄存器数据(从寄存器到总线接口方向)。

(3)使用内部时钟同步化RD信号。

(4)使用同步的RD作为OE线控制P0的三态门,控制选通后的寄存器数据。

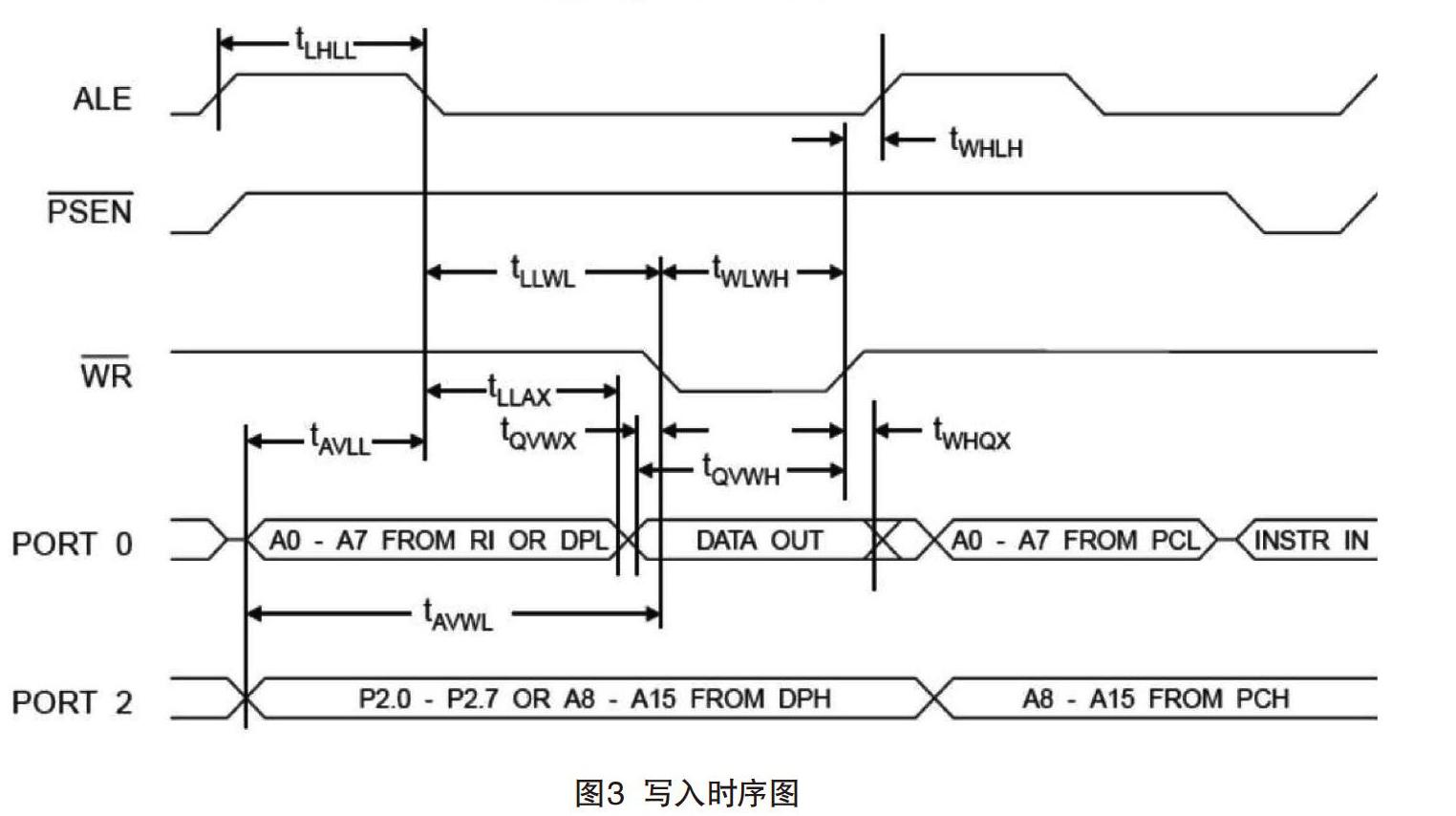

3 写入时序实现

参考Intel-8080总线写入时序图,设计写入控制电路,满足时序要求。如图3所示,ALE由总线主机提供(单片机),读取数据时主机首先拉高ALE,同时主机于P0与P2输出16位地址。ALE高电平持续tLHLL时间后,主机拉低ALE信号,此时从机收到ALE低电平,锁存地址总线信号。经过tLLWL时间后,主机拉低WR信号,于P0上输出写入的数据。经过tWLWH时间后,主机拉高WR信号,从机收到WR上升沿时,从机根据锁存的地址寻址映射表,将P0上的数据写入对应寄存器。经过这一时序,单片机可使用一条MOVX @DPTR,A指令向FPGA写入1个字节指定数据。

FPGA的实现方法为:

(1)使用ALE为时钟线控制8位D触发器,锁存地址信号。

(2)使用锁存后的地址信号控制数据译码器(从总线接口向寄存器方向)。

(3)使用内部时钟同步化WR信号,并判断同步后的WR上升沿。

(4)使用同步的WR的上升沿标志与地址译码结果逻辑与作为寄存器数据锁存CE信号,控制总线信号向寄存器数据写入。

4 结语

依据上述设计的基于FPGA的Intel-8080总线在与STC8A8K进行总线通信时,通信稳定,具有良好的实际应用价值。

Study on implementation of Intel-8080 bus based on FPGA

Xia Yunchao

(Guilin University of Electronic Technology, Guilin 541004, China)

Abstract:The high-speed signal processing system basically revolves around the design and implementation of DSP and FPGA. FPGA has the advantages of high parallel speed, strong processing ability, strong expansibility and can be used in ASIC design. However, FPGA hardware solution has the advantages of long development cycle, fewer developers and fewer public development resources than embedded software solution in realizing low speed peripherals, user interface and user interaction. Therefore, the joint solution based on FPGA and MCU can effectively combine the above advantages and has a good application prospect, but it needs a stable and general communication interface design between FPGA and MCU. The MCS-8051 series single-chip microcomputer is a widely used MCU platform, and the inside is integrated with the Intel-8080 bus controller, so the FPGA can design a communication interface compatible with the Intel-8080 bus protocol to realize the communication between the MCU and the FPGA.

Key words:high speed signal; single chip microcomputer; field programmable gate array