基于FPGA的智能变电站辅助操作分析仪的研制

2018-12-18南方电网玉溪通海供电局曾祥辉

南方电网玉溪通海供电局 曾祥辉

0 引言

近年来,随着智能变电站信息化和网络化水平的不断提高,变电站内智能设备之间的信息交互日益复杂,给整个智能变电站的管理带来了困难。由于无法充分、有效地获取站内海量数据,对整个二次系统的状态监控和故障定位非常复杂。他们不仅需要现场的专家和技术人员完成协调,而且需要大量的时间。此外,当局部地区存在问题时,很难快速识别出整个车站的受影响区域。

然而,如果能得到所有智能变电站的网络数据[1],我们就能够知道更多关于设备状态和系统状态的信息。同时,基于这些数据,能够对整个二次系统的完整性进行研究。利用图形可视化显示和专家数据库技术,可以演示各种过程与其所在区域的二次系统运行状况之间的关系。

此外,还可以对二次系统的运行状态等性能进行定量评价。与传统方式相比,对二级系统的状态管理进行全面识别和分析。然而,传统的数据采集方式效率不高,极大地限制了变电站设备运行状态的分析,也限制了变电站人员整个二次系统的运行和管理。如何以较高的速度和效率充分获取智能化变电站的信息,成为亟待解决的一个技术瓶颈。

目前,现场网络数据包分析仪等设备往往通过软件获取消息。然而由于其分析速度较慢,难以满足全站仪规模的分析需求。二次系统网络中存在大量的信息流,此外系统本身还涉及到全站仪处理层和控制层的网络数据包,需要研究基于硬件模式的信息采集和分析方法,但是传统的ISA、EISA、PCI、AGP总线传输速率已不能满足智能变电站全信息实时采集的要求(如数字数据采集、MMS通信、GOOSE通信、同步通信等)。

参考文献[2]、[3]采用传统的USB2.0总线和CPI总线进行数据传输,总线传输速率有限,不能满足高速的要求。而PCI Express总线的出现极大地改善了这一问题。在[4]、[5]中使用了高速PCI Express总线的传输方式。而设备本身没有对数据的任何有效处理,从而导致传输效率低下。因此,需要开发一种基于新型总线传输的数字光纤硬件分析仪,该仪器在IEC61850中定义了网络消息规则[6],能够满足项目的要求。硬件平台包括光纤收发器和网络数据链路层的构建,需要根据相应的消息进行定制和上传。

本文采用FPGA并行处理结构实现对网络数据包的分析,它比传统的软件包解析更快、更高效。同时,将PCI-Express总线技术应用于智能变电站运行维护辅助分析仪的硬件平台,能够满足智能变电站海量数据的实时采集、高速存储和高效提取的要求。整个智能变电站实现了网络数据的集成监控,同时系统集成度很高。

1 综合监测网络信息体系结构概述

智能变电站采用三层结构和两层网络结构,其组成如图1所示。采用过程层网络实现信息共享。智能变电站的过程层网络与常规变电站的二次回路电缆等效,将间隔层设备与一次设备连接。通过消息在智能设备之间交换信息,信息环由采样值环、GOOSE开关输入输出电路等组成,GOOSE消息主要传递开关量信息。同时,利用SV消息实现合并单元、层间保护与控制装置之间的模拟传输。因此,智能变电站的稳定运行需要高可靠性的GOOSE和SV。它对GOOSE消息有很高的实时性要求。

本文利用智能变电站运行维护的硬件设备作为图1所示的网络信息集成监控框架,主要用于接收、缓存、解析和上传处理层信息(如GOOSE和SV消息)。

图1 网络信息综合监控的体系结构

1.1 硬件平台设计概述

根据QGDW429-2010《智能变电站网络交换技术规范》,当SV通过网络或与GOOSE共用网络传输时,处理层交换机即使在1000M突发业务量激增0.25ms,进入任何100M网络端口也不会造成分组丢失,该网络端口也适用于任何1000M网络端口中的2000M突发业务。当SMV、GOOSE等信息要求更高的可靠性时,全光配置的开关通常选择8、16、24Mbps的光端口和2、4千兆位的光端口。

在设备的正常运行中,系统实现了对硬件分辨率报文设备的要求,设计的报文设备实现了系统的要求,可以在不少于100个节点上满足变电站的规模。硬件设备的单个光端口的传输速率为1000Mb/s,支持GOOSE和SV分析,满足多种网络条件,如组合网络和VLAN划分。硬件设备的硬盘可以支持全站信息存储超过15天。结合上述技术要求,本文设计了一个基于FPGA和PCIE的分析硬件装置,如图2所示。

该平台采用Intel Corei-2655LE处理器,主频可达2.2GHz,5个PCI(e)扩展槽,2个PCIe槽和3个CFast槽,支持2个10/100/1000M以太网端口,两个以太网端口可以访问站级的MMS。与FPGA双向通信的PCIE通道,完成了GOOSE和SV中数据的高速传输。利用CFast链接RAID(冗余磁盘阵列独立)控制器,系统可以访问磁盘阵列的大量数据。为了实现整个装置的灵活性,提高了系统的集成,利用Altera公司的Cyclone IV Gx ep4c FPGA芯片访问网络数据包。

图2 建筑系统硬件平台

利用FPGA实现SV、获取GOOSE消息是本文的难点之一。该系统采用千兆以太网层8E1111芯片实现与光接口和FPGA总线接口的连接,为了保证数据的准确性,使接口连接一个外部的以太网收发芯片实现14千兆从中心交换机通信接口获取。为了提高数据的传输效率,系统采用传动机构合作的双dddr2双缓冲和链式DMA。FPGA将收集分析信息,缓存DDR2写入或收到信息通过链式DMA到主计算机的内存和PCI-E总线。

1.2 消息解析模块

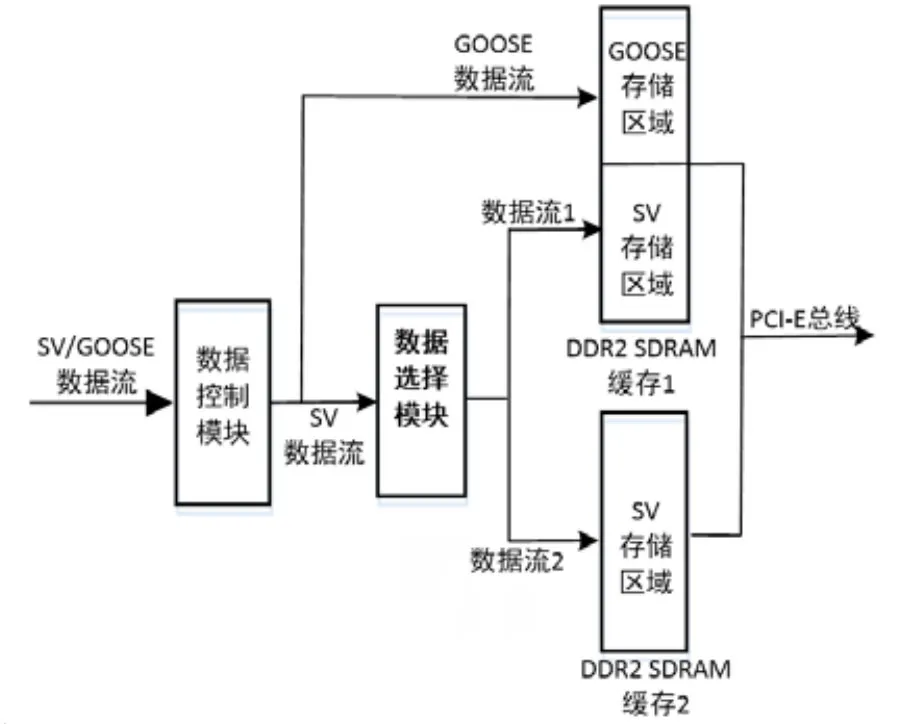

硬件平台主要是从中央交换机获取GOOSE和SV消息。为了满足并发传输时的中央交换机风暴流,系统使用如图3所示的缓存数据接口方法。通过以上处理,减少了操作数据分析造成的延迟,并在实时和优先级传递中将GOOSE消息数据与大量数据分离。还可以减少FPGA上位机触发的MSI中断请求次数,避免高速CPU响应中断的负担。

根据IEC618509-2标准,单个节点的SV消息为每秒4000帧,采样值为每周期80点。如果接入站的间隔设备数为100,每个SV网络包的最大长度为500Bytes,则接入中心交换机四个光端口的SV总数据流量约为4000×100×500Bytes=1.6Gb/s。平台的内部数据处理,通过硬件完成SV消息解析,然后将分析结果打包上传到工控机进行处理。SV数据流量的分析结果约为4000×200×200=0.62Gb/s,经过硬件分析,SV数据流量传输减少了五分之三,即不仅大大降低了PC数据处理的成本,而且提高了数据传输效率。

图3 数据接口处理模块

1.3 数据缓冲和流量控制模块

该装置采用第二代双数据速率同步动态随机存取存储器DDR2作为数据缓存单元。DDR2突发读写到定时的实际操作如图3所示。DDR2控制器的突发长度为16,数据宽度为64。在实际测试中,系统用户的读写时钟频率为62.5M,进行全突发写操作需要16ns×32=512ns,总写入数据为64×16=1024比特。它需要16ns×52=832ns进行全突发写入操作,总写入数据为64×16=1024比特。实际测试结果表明,DDR2突发写入速度为2Gb/s,读取速度为1.2Gb/s,因此写入速度大于硬件分析后的数据流,可以完全避免数据帧。

图4 DDR2突发读写定时

根据系统的需要,必须实时保持GOOSE包传输的硬件平台。SV的传输可以通过缓存上传到系统。当发生故障时,需要在五秒内相应地传输GOOSE分组前后的SV分组数据。因此,系统需要对SV消息进行实时连续访问,以确认当故障发生时,上层软件能够在故障周期之前和之后获得数据。

由于DDR2在读写、控制、数据和地址方面的信号是共享的,因此DDR2不可能同时读写。为了保证同时上传和接收SV,系统采用双缓冲访问机制。我们使用两个缓存,一个作为主缓存、另一个用作备份缓存。为了保证GOOSE的实时性和最小化传输延迟,SV和GOOSE使用子信道和独立的传输机制进行缓存。主缓存分为SV和GOOSE两个存储区,备份缓存尤其适用于SV。

图5 数据缓冲和流量控制模块

1.4 数据传输模块

由于该设备工作正常,整个数据处理能力应大于800MbPs,在极端条件下工作时,整个数据包处理能力应不低于2000MbPs,远远超出传统数据传输总线的能力。因此,需要一种新的总线传输技术突破,而PCI Express(PCIE)总线则是解决这一瓶颈问题的好方法。采用第三代IO总线技术,PCIE采用差分传输方式。这样,每个通道上有两对LVDS差分数据线,它们负责发送和接收数据,每一对差分线路数据的传输速率是2.5Gbps。

将PCIE总线引入智能变电站运行维护辅助分析系统中,可以满足实时采集、高速存储、高效提取智能变电站海量网络数据的需要。为了提高系统的集成度和保持数据传输的灵活性,设备选择FPGA实现PCI Express串行总线的数据传输链路,它的实现框图如图6所示。

图6 组态数据传输链路实现图

如图6所示,PCIE IP模块是一个实现事务层和链路层功能的硬核FPGA芯片实例。采用高速收发器实现PCIE核心物理层的功能,配置模块主要负责从核心配置空间读取信息。DMA阅读器模块和RC从模块完成数据传输,端点设备的存储空间用于主存储器交换数据。

2 驱动程序设计

系统采用WiNeRe+VS2010开发环境完成PC驱动程序的设计。根据所检测到的硬件设备,WindDriver将自动生成与硬件相关的库函数,这允许用户在现有框架基础上定制他们的驱动程序。

PC机与硬件板之间有两种主要的交互方式。第一种方式是PC机通过简单的控制命令自动读取卡片的内容,读取和写入数据空间。无论BAR空间多大,它们只能依次进入空间。如果只用BAR空间进行读写,数据传输速度不超过100MBps,CPU负载非常高。显然,这种高速数据传输方式是不可接受的。

为了提高传输效率,降低CPU的工作压力,系统采用PCIe卡读写PC数据(DMA)。本文采用如图7所示的驱动程序设计。首先,将PC应用于具有连续物理地址的一段内存空间。FPGA将发送MSI中断通知PC读取数据时,它达到一定的数据规模。然后PC机接收并分析中断,并写入BAR0空间寄存器,该寄存器包含上述物理地址的起始地址和空间大小,最后PC机启动DMA。在完成数据传输过程后,FPGA向PC机发送一个中断,当主机接收到中断时,读取BAR0空间状态寄存器确定中断类型,然后做出适当的判断。PC将数据从物理地址空间复制到用户程序可以访问的空间中。

图7 驱动程序设计过程

3 实验分析

智能变电站的运行维护系统主要接收来自过程层中心交换机和上传到上层软件平台打包且由硬件分析后的信息,该系统采用Kaimo公司的SNT3000智能变电站网络测试平台进行了实验验证。通过设置SNT3000,可以把两种典型的压力测试来测试以太网的信息,包括机构的时间压力数据流和数据流的流动机理。由时间机器数据流测试的分组丢失率如表1所示。

表1 时间机制结果表

从理论上讲,Cyclone IV FPGA DMA的写入速度约为622MB/S,PCIe报头造成的效率损失是固定的比例,每帧有效数据为128字节,报头为16字节。PC的中断处理时间为6us,这与Windows正常中断处理时间的大小相同。在完整步骤中,寄存器将有大约第八次写入操作,每个操作大约占用0.5us,而读取操作大约占用2us。主机的适当等待时间约为10us,每个数据传输DAM的大小为4MB,需要23us传输一次数据。然后实际PCI Express DMA写传输速度应该是:(128/(128+16))×(23/(6+0.5×8+23))×622MB/S=385.3MB/S。图8示出了在测试流量中具有不同流的系统的实际吞吐量。

图8 测试系统吞吐曲线

如图8所示,它是流量机构的压力测试下的吞吐曲线。第一条曲线是关于系统的理论速度,第二条曲线是关于系统的吞吐量,而不需要分析消息。当数据流大于312Mb/s时,系统达到最大处理能力,数据开始丢失。第三个曲线是系统解析消息后的吞吐率,并采用链DMA传输系统。通过系统硬件平台分析,有效的数据传输系统仅占整个传输系统的三分之一,因此系统能够承受更高的数据量注入。

图9 消息解析结果显示图

图9示出了软件平台中的消息解析结果。在测试结果中,解析后的GOOSE信息能够准确反映智能变电站运行信息,满足功能要求,并能够准确显示验收过程和区域相关性。当故障发生时,也能准确地显示SV在近时间的故障波形。

4 结论

为了解决智能变电站运行辅助分析系统中数据采集问题,设计了一种基于FPGA的网络消息解析硬件装置。通过时间机构和流量机构的实验和测试,验证了该变速器的可靠性和稳定性。结果表明,该装置能够满足变电站海量网络数据的实时采集、高速存储和高效提取的要求,能够完成处理层网络,并能完成网络数据包接收、缓存、解析和上传等功能,为变电站人员合理有效的管理提供了一种可行的方案。