GPS通信系统的设计

2018-12-06

(1、2、3.安顺学院电子与信息工程学院,贵州 安顺561000)

目前卫星导航定位系统在全球范围内都备受重视,随着欧盟、中国、俄罗斯以及美国等国家对全球卫星导航定位系统相关计划的推出,全球导航定位系统已经进入了蓬勃发展全面竞争的时代。近年来FPGA(Field -Programmable Gate Array)的相关技术已经有明显的进步,应用广泛,本设计通过内嵌综合器以及仿真器的Quartus II软件实现功能。Verilog HDL(Hardware Description Language)具有运行速度快,界面统一,功能集中,易学易用等特点[1]。相较于VHDL(Very High Speed Integrated Circuit Hardware Description Language)有较强的生命力,更加具有直观性。

1 GPS通信系统总体设计

Nios II嵌入式处理器便于模块的集成。Quartes II中的SOPC Builder的组件库提供了SDRAM(Synchroonous Dynamic Random Access Memory)、FLASH(flash memory)和SRAM(Static Random-Access Memory)等控制器,分别通过他们实现对相应模块的控制。本设计分别完成SOPC(System-on-a-Programmable-Chip)系统的搭建,IP核部分的SDRAM_PLL模块和delay_reset_counter模块的设计,并通过适配器将各个模块与主模块连接起来,生成顶层模块,通过仿真验证结果。GPS系统原理图如图1所示。采用Star-III模块,该模块的输出信号根据NMEA(National Marine Electronics Association)0183格式标准输出的,输出信息主要包括位置测定系统定位资料GPGGA,偏差信息和卫星状态GPGSA,导航系统卫星相关资料GPGSV和GNSS信息GPRMC等部分[2]。

1.1 SOPC系统

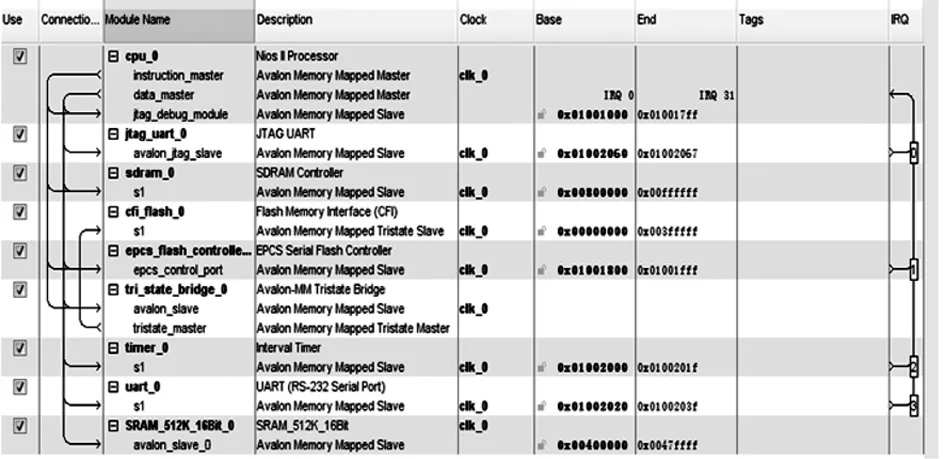

搭建SOPC系统需要SDRAM控制器、Flash控制器、EPCS Serial Flash Controller模块、Avalon 三态桥、Timer 控制器、UART串口和JTAG_UART接口,分别挂在Avalon总线上,由于在SRAM中,只使用了readdata,writedata两个单向信号,而不是双向的data信号进行信息之间的交互,所以SRAM不需要与三态桥有联结,直接挂在了总线上。在SOPC的搭建环境下完成各部分的连通从而实现数据的传输。

SDRAM称为动态随机存储器,通过使用晶体管和电容结构来实现所需功能。Flash控制器兼有掉电时数据不会丢失和在线更改数据的特点。EPCS(Erasable programmable configurable serial)串行存储器,SOPC系统下的Nios II工具所执行代码的存储位置并非EPCS中,而是在RAM中,即使断电也不会影响数据的保存,除非有新的数据将其覆盖。Avalon总线是将Nios CPU与所有的外设相连的工具,通过总线实现数据的交换。Timer定时器驱动JTAG-UART实现串口工作的暂停。而JTAG-UAR串口模块,用于连接计算机,实现信息互换和数据的传输。SRAM(static ram)静态存储器具有静止存取功能,无需自我刷新即可保存它内部存储的数据。

在一个Nios系统中有多个存储器,虽都有存储功能,但是存储的内容多有不同。FLASH多用于存储应用程序;SDRAM作为Nios处理器的RAM和程序运行空间;SDRAM相对于SRAM操作较为复杂SRAM用于高速存取,如显示器缓存。

图1 GPS通信系统原理图

搭建完成后的SOPC系统称为CPU软核,是进行信号处理时所离不开的环境,也是GPS通信系统的核心。采用的Quartus II软件是由嵌入式软件开发设计、可编程逻辑功能设计、集成系统硬件平台设计组合的综合性开发平台[3]。

1.2 自定义IP核

SOPC系统设计中的重要技术之一为IP核(知识产权核),不仅可由厂商提供,也可以通过用户自定义。用户在设计电路时可根据实际需要直接调用IP核或自主生成。本设计使用的IP核看不见程序,只能看见端口信息。仿真验证的过程中与自设构件SRAM大有不同,首先在自主设计的过程中应该先在IP核的库文件中添加相应的库,完成库的建立后对IP核的参数进行设置,从而完成IP核的创建。通过以上GPS通信系统的设计需要添加SRAM-PLL(SDRAM-Phase Locked Loop)模块和复位模块的IP核。

SDRAM-PLL是用于整合时脉讯号的锁相环路又称为锁相环,工作原理为让高频器件能进行正常工作,其必要条件为外部的激励信号与内部的振荡信号同步。SDRAM的时钟输入是由SDRAM-PLL时钟输出。

复位信号是一种能够使电路恢复到初始状态的信号。功能都是使程序的执行回到原点,重新进行操作,类似于计算机的清零作用。计算器清零需要手动进行清零,而复位与其的差别就是复位是在对电路通电后进行操作,还可通过手动进行操作。所需IP核按照上述的方法进行库的建立和仿真。

2 软件仿真

1940年以后,系统仿真是一门新兴的学科,计算机技术的蓬勃发展,对于人们的生活有了很大的改变,各个行业都有了新的突破,在电子器件设计方面也不例外,仿真这门学科也在不断进步。实验在研究过程中所通过建立系统模型并利用所建模型对实际系统进行分析的过程就称为仿真,再对仿真结果的试验和分析。

2.1 SRAM仿真

由于SRAM为自设构件,需要通过Quartus II软件开发环境使用Verilog语言编写代码,编译通过后生成波形文件,在波形文件的空白处双击进行端口的设定,添加端口到波形文件,为输入端口设置激励信号,可通过编写testbench测试文件的方法添加激励信号。

图2 SRAM模块仿真结果

该模块端口定义分为主机端和SRAM 端的,由主机端作为输入端,SRAM作为接收端。在主机端和SRAM端分别定义时钟、片选、写使能、读使能和地址等端口,使得SOPC系统与主机端相连从而获得输入信号。SRAM在运行时首先通过地址总线将要读取的地址传到地址引脚,激活片选信号进而选择SRAM芯片,再激活读使能或写使能信号,使得SRAM能进行读或写的操作。在SOPC系统中所创建的自设构件SRAM对端口定义后,与主机端的相应端口互连,在所生成的波形文件中设置输入端也就是主机端的信号,完成激励信号后进行仿真,其仿真图如图2所示。由图可得SRAM端的输出信号与主机端的输入信号波形一致,验证SRAM模块设计正确。搭建完成的SOPC系统如图3所示。

图3 SOPC系统

2.2 SDRAM-PLL仿真

在仿真软件中添加所需的库,再在仿真的时候调用该库进行仿真。该模块为反馈控制电路,使用外部的参考信号控制环路内部振荡信号的频率和相位,使得能为系统提供稳定的工作状态。应用于通信的接收机中,对接收到的信息进行处理。利用外部的时钟输入作为参考信号来控制输出信号C0、C1、C2的频率和相位。对该IP核进行参数设置,手动设置C0频率为100MHz,C1频率为40MHz,C2频率为10MHz,进行仿真的过程中添加时钟为激励信号,触发模块,使得模块处于工作状态。仿真图如图4所示。

图4 SDRAM-PLL仿真

2.3 复位模块仿真

该模块属于FPGA 所提供的IP核。作用为消除电路运行过程中所产生的抖动,系统上电时提供复位信号,到电路稳定之后撤销复位信号,其中使能信号高电平时启动,而aclr(异步清零)信号是低电平时启动,当二者信号都处于工作信号时,只要时钟上升沿触发,即对q输出信号有作用,从而进行数据更新。复位模块的仿真如图5所示。

图5 复位仿真

3 仿真验证

通过对各模块的设计和仿真验证,证明了各个部分设计正确。再通过Quartus II 软件生成原理图,进行模块连线完成GPS通信系统的顶层设计。编写程序使得GPS的顶层模块实例化,使得端口之间的连接实现信息的交互,通过模块之间的调用实现功能的转换。从而证明该系统的正确性。整个设计由外部的复位模块和锁相环来提供SOPC系统稳定工作的时钟信号,为GPS通信系统能正常运行提供信号。

4 总结

在FPGA的开发环境下,使用Verilog硬件描述语言设计GPS通信系统,大大缩短了设计的周期,提高设计的正确性,在编译或仿真时对系统功能进行验证,若出现错误,可直接修改再进行后续操作直至系统完全正确。这使得本设计较于市场上电子器件的设计有着一定的优势,拥有更好的应用前景。