多约束下寻找关键门的门替换技术缓解电路的NBTI效应

2018-11-13周瑞云易茂祥黄正峰

周瑞云 易茂祥 黄正峰

摘 要: 随着晶体管特征尺寸的不断减小,威胁数字电路可靠性的一个重要因素是负偏置温度不稳定性。为了缓解NBTI效应对电路产生的老化影响,文中提出时延约束、路径约束和考虑非门的可防护性约束的多约束下,通过计算门的影响因数的大小来寻找定位关键门集合,用门替换的方法来防护关键门。通过实验进行证明,文中提出的方法不仅识别出的关键门数量少,且更加精准,老化的时延改善率更高。

关键词: 负偏置温度不稳定性; 电路老化; 关键门; 时延约束; 影响因数; 门替换

中图分类号: TN710.2?34; TP331 文献标识码: A 文章编号: 1004?373X(2018)22?0113?04

Abstract: As the feature size of the transistor decreases constantly, negative bias temperature instability (NBTI) becomes an important factor threatening the reliability of the digital circuit. Under the multiple constraints of time delay constraint, path constraint, and protective constraint considering non?gate, the influence factor of the gate is calculated to search and locate critical gate sets, and the gate replacement method is used to protect critical gates, so as to mitigate the influence of the NBTI effect on circuit aging. The experimental results prove that the method proposed in this paper identifies a small number of critical gates, is more accurate in critical gate search, and has a high time?delay reduction rate during aging.

Keywords: NBTI; circuit aging; critical gate; time?delay constraint; influence factor; gate replacement

随着高新电子技术的迅猛发展,电路的性能和集成度有了较大程度的提高。但晶体管的电压并未随着特征尺寸的降低而减少,此时CMOS的参数逐渐接近物理极限,影响器件的使用寿命,使得器件的可靠性不断下降。CMOS集成电路产生可靠性问题的原因众多,如热载流子注入、电迁移、栅氧经时击穿和负偏置温度不稳定性等。尤其是纳米工艺达到65 nm以下水平, NBTI效应是电路产生失效机制的主要原因[1]。NBTI效应是一种作用于PMOS晶体管的老化机制。根据有关文献表明,电路工作10年后,由NBTI效应引起晶体管的阈值电压增加50 mV,工作速率[2]下降20%。电路有两种工作模式:待机模式(Standby)和活动模式(Active)。在活动模式下,PMOS晶体管的输入信号交替出现高低电平,受到的是动态NBTI效应;在待机模式下,PMOS晶体管的栅极始终处于低电平信号下,受到的是静态NBTI效应。在电路工作的整个生命周期内,静态NBTI效应对电路产生的影响比动态要大[2]。当电路遭受NBTI效应后,会使得PMOS管的阈值电压升高,漏极电流减小,门节点的时延增加。从而导致路径的时延增加,最终发生时序紊乱,芯片的功能彻底失效。因此,研究如何减缓NBTI效应对电路造成的老化影响有着非常重要的现实意义。

国内外的研究学者采用以下方法缓解电路的NBTI效应。通过调整门的尺寸方法来缓解电路NBTI效应,但会引入额外的面积开销[3];采用多阈值电压技术[4];确保电路功能不变的情况下,采用逻辑重构和引脚重排的方法[5];根据不同路径的时序余量不同,采用时序拆借的方法[6];输入向量控制技术[1];插入传输门技术[7]等。

本文是在电路处于待机模式下,采用门替换的方法来缓解NBTI效应对电路产生的老化影响。其能够直接使用标准单元库进行替换,不会引入额外的晶体管的堆叠效应,弥补了IVC技术不能较好地防护电路逻辑深处的门节点的缺点。

传统的关键门识别存在的问题是,找到的关键门过多,增加了防护的开销;或者未寻找到精准的关键门集合,降低了门替换的防护效果。本文是基于传统的静态时序分析框架下,提出多约束下通过计算门的影响因数来识别关键门。着眼于寻找影响电路老化时延严重的关键门集合,再用门替换的方法对所识别的关键门进行防护。

1 NBTI建模与门替换介绍

1.1 NBTI建模

式中:[B]为常量;[Vth0]是PMOS管未老化前的阈值电压;[d(V)]指的是逻辑门的固有时延。一般而言,一個门具有多个PMOS管,文中考虑最坏情况下的最大值作为门的老化时延。

1.2 考虑非门的门替换

文献[4]首次将门替换应用于缓解由NBTI效应引起的电路老化问题。

传统的门替换技术在替换关键门的扇入门时,仅考虑与非门和或非门,忽略了扇入门为非门的情况。本文在第三约束可防护性约束下,还考虑到了非门的替换。非门是一个上拉PMOS晶体管串联一个下拉NMOS晶体管构成的,逻辑上非门可以视为单输入与非门。当关键门的扇入门为非门时,在原来的电路结构上拉网络并联一个PMOS管,下拉网络串联一个NMOS管非门,可以替换为多一个休眠信号的双输入与非门。

2 多约束下关键门的识别方法

2.1 关键门定位的设计流程

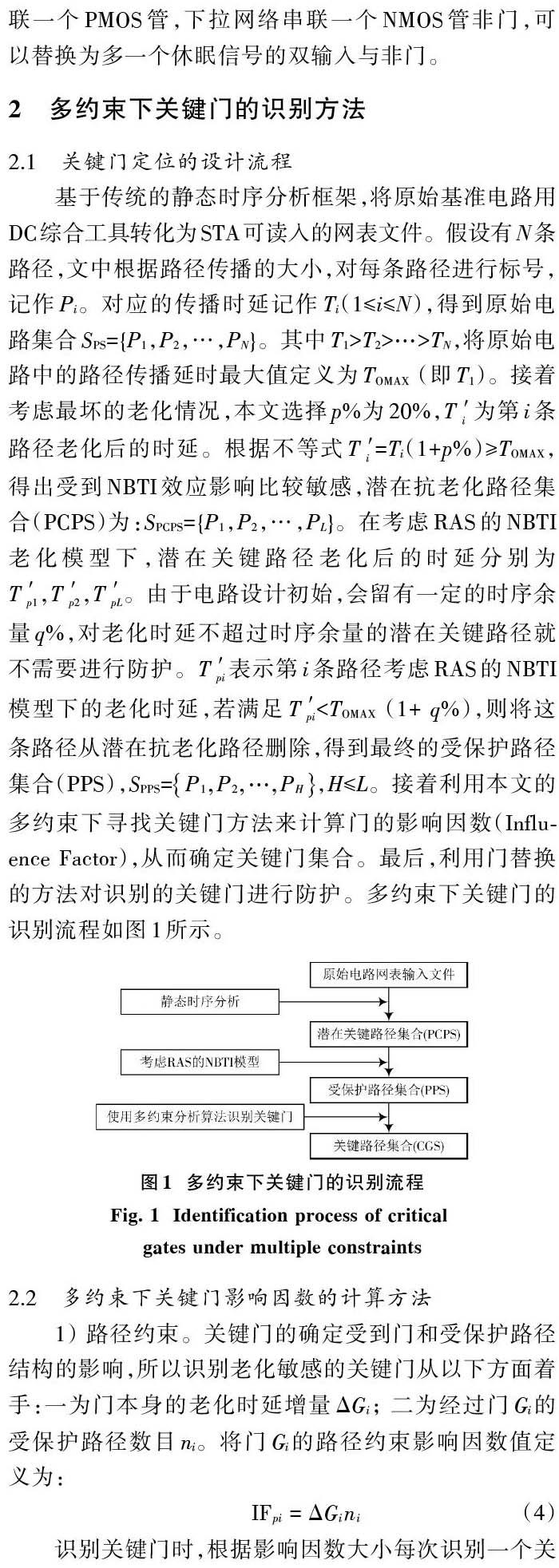

基于传统的静态时序分析框架,将原始基准电路用DC综合工具转化为STA可读入的网表文件。假设有N条路径,文中根据路径传播的大小,对每条路径进行标号,记作Pi。对应的传播时延记作Ti(1≤i≤N),得到原始电路集合SPS={P1,P2,…,PN}。其中T1>T2>…>TN,将原始电路中的路径传播延时最大值定义为TOMAX (即T1)。接着考虑最坏的老化情况,本文选择p%为20%,[T′i]为第i条路径老化后的时延。根据不等式[T′i]=Ti(1+p%)≥TOMAX,得出受到NBTI效应影响比较敏感,潜在抗老化路径集合(PCPS)为:SPCPS={P1,P2,…,PL}。在考虑RAS的NBTI老化模型下,潜在关键路径老化后的时延分别为[T′p1,T′p2,T′pL]。由于电路设计初始,会留有一定的时序余量q%,对老化时延不超过时序余量的潜在关键路径就不需要进行防护。[T′pi]表示第i条路径考虑RAS的NBTI模型下的老化时延,若满足[T′pi] 2.2 多约束下关键门影响因数的计算方法 识别关键门时,根据影响因数大小每次识别一个关键门,防护该关键门,然后重新计算影响因数并识别下一个关键门,如此循环直到保护路径满足时序要求为止。得到路径约束下的关键门集合CGIP set。 得到路径约束下的关键门集合CGIG set。 可防护性约束下计算门的影响因数如图2所示。对于图2a)而言,要想防护G2需要对其前驱门进行判断,发现为与非门,可以直接替换为有[sleep]信号的NAND2。此时,式(6)中Mi=1。对于图2b)而言,计算G2的可防护性影响因数[IFG2],由于G2是NOR2,查找该门的前驱门有两个:G5是与非门,可以直接替换成有[sleep]信号二输入与非门;而G1也是NOR2,需要查找该门的前驱门进行判断是否可防护,发现G3和G4也是NOR2。所以,可以将其替换为有sleep的NOR3,在式(6)中Mi=3。 文中定义的三种约束下寻找到的关键门集合,并不是完全独立的。本文通过三个关键门集合的交集作为最终的关键门,最终得到更加精确的关键门集合CG set。

3 实验结果及分析

3.1 实验环境设置

本文使用C++编程语言编写多约束下关键门的识别以及门替换算法。ISCA85基准电路作为实验验证电路,试验电路的网表是经过Synopsys公司的DC综合工具和45 nm标准单元综合而成的。综合后的实验网表中只包含INV、2?4输入的NAND,以及2?4输入的NOR门。文中采用的参数设置与文献[9?10]中的相同Vdd=0.8 V。对于MOS晶体管的阈值电压为[Vth]=0.18 V,Tox=1.1 nm。在两种不同的工作模式下,活动和待机时间比例即RAS=1∶9,温度均为T=378 K,占空比为0.5;电路的工作时间Tlife为10年,老化最大延迟P=20,时序余量q本文可以选择5%,10%,15%。

3.2 实验结果分析

在不同的时序余量下(q=5%,10%和15%),采用本文方法识别的关键门数目的比重分别为9.09%,4.56%和1.84%。而文献[9]识别的关键门的比重分别为11.56%,5.44%和2.38%。在相同时序余量下,本文所识别的关键门数目比文献[9]小得多。随着时序余量的增大可观察到,识别的关键门数目在不断减小。这主要是因时序余量设置得越大,电路容忍的老化能力則越强,自然需要防护的关键门数量也在减小。

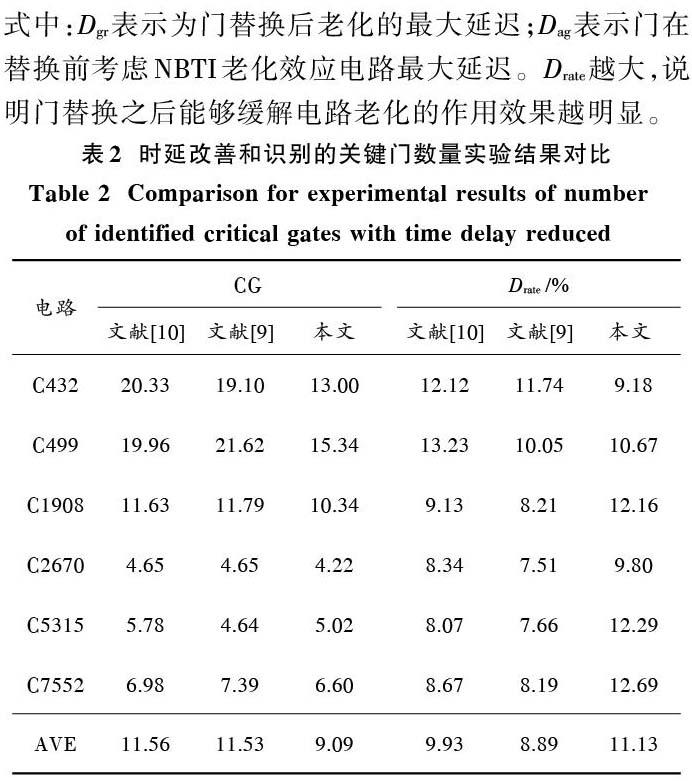

式中:Dgr表示为门替换后老化的最大延迟;Dag表示门在替换前考虑NBTI老化效应电路最大延迟。Drate越大,说明门替换之后能够缓解电路老化的作用效果越明显。

时延改善和识别的关键门数量实验结果对比如表2所示。文献[10]识别关键门的平均数量为11.56%,文献[9]识别关键门的平均数量为11.53%。相比较之下,两者在关键门的识别上相差无几,而本文方法识别出电路的关键门的平均数量仅为9.09%。在时延改善率上,文献[10]比文献[9]平均提高了11.7%,说明在防护近似数量相同的关键门上,文献[9]对关键门的识别更加精准。本文的平均时延改善率为11.13%,对于文献[10]相对平均提高了12.08%,对于文献[10]相对平均提高了25.20%。由此证明,本文的方法在对关键门的定位和识别方面不仅少且更加的精准。防护后的电路对NBTI效应的影响容忍的能力更强。

4 结 论

本文提出了多约束下识别关键门的门替换方法,阐述了路径约束下、时延约束下和可防护性约束下如何计算关键门的影响因数,得到不同约束下的关键门集合。通过三个关键门集合的交集得到最终更加精确的关键门集合CG set。最后将非门作为门替换的逻辑门类型,通过实验本文方法不仅仅在关键门的识别数量上有大幅度的减少,并且时延的贡献率更加显著,同时证明了本文寻找到关键门的准确性更高。

参考文献

[1] VAZQUEZ J C, CHAMPAC V, ZIESEMER A M, et al. Low?sensitivity to process variations aging sensor for automotive safety?critical applications [C]// Proceedings of 28th VLSI Test Symposium. Houston: IEEE, 2010: 238?243.

[2] WANG Wenping, YANG Shengqi, BHARDWAJ S, et al. The impact of NBTI on the performance of combinational and sequential circuits [C]// Proceedings of 44th ACM/IEEE Design Automation Conference. San Diego: IEEE, 2007: 346?369.

[3] KUMAR S V, KIM C H, SAPATNEKAR S S. Adaptive techniques for overcoming performance degradation due to aging in COMS circuits [J]. IEEE transactions on very large scale integration systems, 2011, 19(4): 603?614.

[4] CHAN T B, SARTORI J, GUPTA P, et al. On the efficacy of NBTI mitigation techniques [C]// Proceedings of Design, Automation & Test in Europe Conference & Exhibition. Grenoble: IEEE, 2011: 1?6.

[5] WANG Wenping, YANG Shengqi, CAO Yu. Node criticality computation for circuit timing analysis and optimization under NBTI effect [C]// Proceedings of 9th International Symposium on Quality Electronic Design. San Jose: IEEE: 2008: 763?768.

[6] YUAN L, QU G. Simultaneous input vector selection and dual threshold voltage assign for static leakage minimization [C]// Proceedings of IEEE/ACM International Conference on Computer?Aided Design. San Jose: IEEE, 2007: 548?551.

[7] LIN I C, LIN C H, LI K H. Leakage and aging optimization using transmission gate?based technique [J]. IEEE transactions on computer?aided design of integrated circuits and systems, 2013, 32(1): 87?99.

[8] 范磊,梁华国,易茂祥,等.电路抗老化设计中基于门优先的关键门定位方法[J].微电子学,2017,47(2):258?263.

FAN Lei, LIANG Huaguo, YI Maoxiang, et al. A method to identify critical gates by prioritizing logic gates under circuit anti?aging design [J]. Microelectronics, 2017, 47(2): 258?263.

[9] 梁华国,陶志勇,李扬.一种缓解NBTI效应引起电路老化的门替换方法[J].电子测量与仪器学报,2013,27(11):1011?1017.

LIANG Huaguo, TAO Zhiyong, LI Yang. Efficient method to mitigate NBTI?induced circuit degradation by gate replacement techniques [J]. Journal of electronic measurement and instrumentation, 2013, 27(11): 1011?1017.

[10] BHARDWAI S, WANG Wenping, VATTIKONDA R, et al. Predictive modeling of the NBTI effect for reliable design [C]// Proceedings of IEEE Custom Integrated Circuits Conference. San Jose: IEEE, 2007: 189?192.