电镀镍层作为掩模层的薄膜电路制备方法

2018-10-27刘玉根

刘玉根,孙 林

(中国电子科技集团第五十五研究所,南京 210016)

1 引言

薄膜电路由于具有体积小、重量轻、可靠性高、布线密度高和可集成无源元件的特点,在机载、星载、航天等领域的微波电路上有着广泛的应用。典型的薄膜电路生产工艺主要有两种,第一种工艺流程为:陶瓷基片清洗→金属化→一次光刻→电镀→二次光刻→湿法刻蚀Au/TiW/TaN或Au/TiW;第二种为陶瓷基片清洗→金属化→光刻→电镀→干法刻蚀Au→湿法刻蚀TiW/TaN或TiW。第一种工艺包含二次光刻过程,增加了工艺的复杂程度,生产效率低且成本高;同时还存在人工对位误差的问题,不利于产品精度的提高。第二种工艺虽然避开了二次光刻,提高了生产效率,但干法刻蚀所需设备昂贵,前期设备投入和后期设备运行维护费用较高[1-3]。

针对上述两种传统工艺存在的缺陷,文中提出了一种利用电镀镍层作为刻蚀保护层制备薄膜电路的方法。其目的是利用电镀镍层作为掩模层来代替“二次光刻”,既简化了工艺过程,提高了生产效率,降低了生产成本,也进一步提高了薄膜电路线条精度,具有制备工艺简单、需要的生产设备少、可工业化、低成本大规模生产的特点。

2 实验

2.1 薄膜电路制备流程

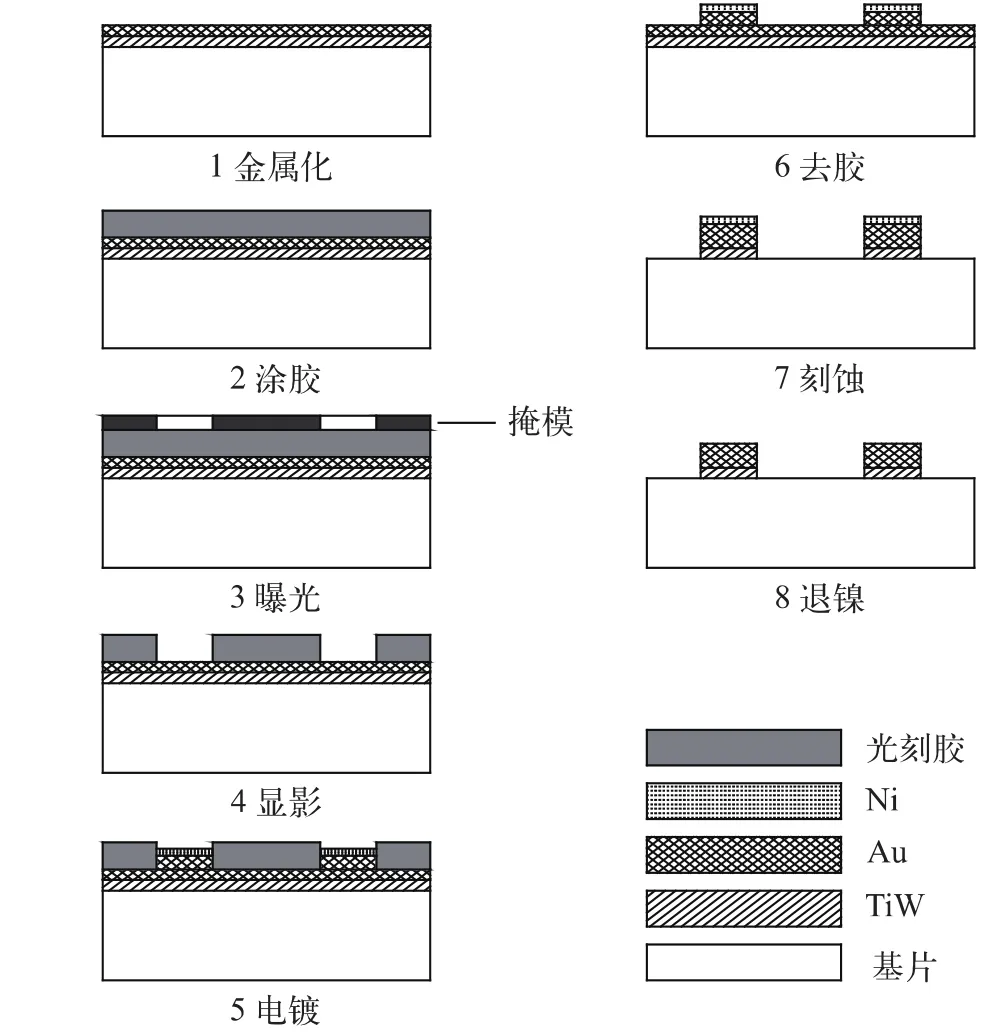

实验以铁氧体材料为例制备薄膜电路,利用镀镍层作为湿法刻蚀过程中的保护层,省去了二次光刻工艺,成功制作出了满足生产要求的铁氧体薄膜电路,大幅提高了薄膜电路的生产效率。其工艺流程为:基片清洗→金属化→光刻→电镀Au/Ni→湿法刻蚀Au/TiW→退镍,如图1所示。

图1 电镀镍层作为掩模层的薄膜电路制备工艺流程图

2.1.1 基片清洗

基片表面的清洁程度是影响薄膜与基片间结合力的主要因素,如果表面不清洁,薄膜和陶瓷基片不能直接接触且会使得膜层产生较大的应力,严重削弱附着力。基片表面的清洗大致分为物理清洗和化学清洗两大类,由于铁氧体材料可与酸发生化学反应,破坏材料表面状态,因此实验中采用甲苯、丙酮、酒精等有机试剂并辅以超声的方式清洗,最后冲洗甩干。

2.1.2 金属化

薄膜电路金属化工艺主要是指物理气相沉积,含蒸发和溅射两类。与蒸发相比,磁控溅射具有膜基结合力强、生产效率高、可重复性好的优点,在微电子制造、光学以及机械加工等领域已被大量应用。本实验采用KDF磁控溅射台依次在铁氧体基片表面沉积TiW/Au,其中TiW为粘附层,厚度为80~90 nm,Au为导体层,厚度为180~200 nm。

2.1.3 光刻

光刻工艺主要分为涂胶、曝光和显影3个部分,其工艺流程为:基片前处理→涂胶→前烘→对准和曝光→显影→坚膜。对于选择性电镀工艺,光刻胶厚度要求大于电镀层厚度,以确保电镀时镀层无侧生长,保证线条精度。光刻过程中,前烘的温度和时间、曝光能量以及坚膜的温度和时间等都十分重要,会直接影响到光刻胶与基片的结合力,以免电镀时出现钻镀现象。

2.1.4 电镀

由于微波信号的传输特性,微带线路都要达到一定的厚度要求,而溅射薄膜的厚度通常都在500 nm以下,因此必须通过电镀对导体进行加厚处理。光刻显影后的基片表面会残留光刻胶底膜,镀前需经等离子打胶处理。本实验在完成正常镀金要求后,又在镀金层上面增加了电镀镍,镀镍层会在刻蚀过程中充当保护层,保护镀金层表面在刻蚀过程中不被腐蚀。

2.1.5 刻蚀

刻蚀工艺是指有选择性地去除表面材料层,包括湿法刻蚀和干法刻蚀。与干法刻蚀相比,湿法刻蚀速率快、成本低,可以满足10 μm以上线宽的薄膜电路加工要求。多层金属刻蚀是湿法刻蚀工艺的一个难题,由于选用了镍作为保护层,因此选择刻蚀液时需要考虑其对镀镍层的影响[4]。采用选择性电镀工艺,需要刻蚀部分的膜层厚度只有几百纳米,腐蚀时间非常短,对微带线的侧向腐蚀很小,几乎可以忽略。

2.1.6 退镍

湿法刻蚀后需要将作为保护层的镀镍层去除,其蚀刻液的选择主要考虑以下几个因素:对基材无影响,对微带线膜层结构中的金属化层无影响,腐蚀速度快。

2.2 测试方法

2.2.1 键合强度

采用直径 25 μm 的金丝和 250 μm×12.7 μm 的金带分别进行试验。试验后要求微带线金层形貌良好,25 μm 金丝的键合拉力应大于 5 gf,250 μm×12.7 μm金带的键合拉力应大于15 gf,且金层无皲裂、脱落现象[5]。

2.2.2 镀层附着力

采用胶带法,选用3M公司生产的剥离强度为4.9 N/cm的胶带作为检验基板镀层附着力的试验胶带。具体方法如下:将基板清洗干净,晾干;用Scotch胶带贴在基板表面,先用手指,然后用橡皮擦抹平以排除空气,放置60 s左右;以接近180°角的方向迅速将胶带拉下;在10倍放大镜下检查基板和胶带,试验后基板应无镀层颗粒或导电图形起皮、气泡、剥落。

2.2.3 剥离强度

将退火后的软实心铜线焊接在微带线端头,并将铜箔弯折成垂直90°,铜箔的另一端固定在拉力试验机上进行拉力试验,并记录微带剥离电路板时的拉力F,抗剥强度=F/W,W为微带线宽度[6]。

3 结果与讨论

3.1 薄膜电路形貌

图2所示为所制备的铁氧体薄膜电路基板,基板尺寸为8.9 mm×9.8 mm×0.4 mm,台阶仪测得镀层厚度为4.7 μm,由于采用了选择性电镀工艺,其微带线条精度达到±2 μm。从产品细节放大照片可以看出线条边缘光滑且轮廓清晰,采用镍作为刻蚀保护层避免了二次光刻中带来的套刻误差,镀金层表面未发现有腐蚀液侵蚀现象。

图2 铁氧体薄膜电路基板照片

3.2 薄膜电路性能

采用该方法加工的铁氧体薄膜电路在经过键合强度、镀层附着力以及剥离强度测试后均无失效现象,测试数据见表1、表2。其中剥离强度试验中失效现象为引线从焊点部位拉开,并未出现微带线与基片分离的现象(见图3),可见实际剥离强度要大于表2中的测试数据。

图3 剥离强度试验后基板照片

表1 键合强度试验数据

表2 剥离强度试验数据

3.3 产品电性能测试

图4为该工艺加工的X波段铁氧体环形隔离组件样品实物照片,采用Agilent 8720ES矢量网络分析仪对样品主要参数指标进行测试,测试结果如表3所示。

图4 样品实物图

表3 主要参数指标测试结果

3.4 工艺难点

金属腐蚀是薄膜工艺中的重要工序之一。同一种金属往往有多种腐蚀方法,具体用哪一种,除了要考虑腐蚀速率、选择比、腐蚀液的稳定性与可控性外,还应根据不同的金属膜系和工艺线路来选择。常用的金刻蚀液大多为I2+KI体系,其在腐蚀金的同时也会对镍进行腐蚀,而在其中加入磷酸或者磷酸盐可以抑制甚至不腐蚀镍,从而达到蚀刻保护的目的。该工艺方法对镀镍层的厚度也有一定要求,如果镀镍层太薄,腐蚀液会从镍表面渗透下去造成金表面的局部腐蚀。通过不同厚度的镀镍层腐蚀效果对比后发现,在镀镍层厚度达到0.5 μm以上时,才可以避免对下层金的腐蚀。

4 结论

利用镀镍层作为掩模层制备得到的薄膜电路外观质量合格,金属图形完整,无脱落、断裂等问题,电路键合强度、镀层附着力及剥离强度满足质量要求。与传统制备方法相比,该方法制备得到的薄膜电路微带线具有更高的线条精度。

该制备方法工艺流程简单,减少了二次光刻,降低了生产成本,生产效率大幅提高;无需使用干法刻蚀类的昂贵设备,避免了干法刻蚀设备采购与后续维护保养带来的高昂费用,降低了生产物资投入,有利于大规模生产。