基于FPGA和PCI接口的EtherCAT从站网卡设计

2018-10-23程天亨张舞杰

程天亨,张舞杰

(华南理工大学 机械与汽车工程学院,广州 510640)

在一些工业自动化流水线生产领域,为了满足生产需求,需要使用工业相机甚至使用多台工业相机进行数据测量。面对成像技术不断发展和进步的新时期,相机分辨率高信息数据量较大,实时性和同步性需求高[1-2],多相机数据传输成为新时期迫切需要解决的问题。同时,随着计算机技术和工业以太网技术的发展与融合,工业以太网由于其速度快、成本低、扩展性好、抗干扰性强等特点取得了广泛的应用。国际上许多著名的工业自动化公司也相继提出工业以太网新标准。德国Beckhoff公司提出的 EtherCAT(Ethernet for control automation technology),具有灵活的网络拓扑结构、系统配置简单、数据传输全双工、高速高效、总线利用率较高等特点[3-5],可以有效地运用在多相机数据传输领域。

然而工业相机的数据接口协议与EtherCAT协议不兼容。为解决工业相机接入EtherCAT网络系统的问题,在此,提出一种将具有实时采集相机图像和图像处理功能的工控机作为从站设备与主站相连的解决方案,并设计了一款基于FPGA和PCI接口的EtherCAT从站网卡,将工控机接收到的图像原始数据或图像处理后的数据传输到EtherCAT网络中,实现与EtherCAT主站数据交互的功能。

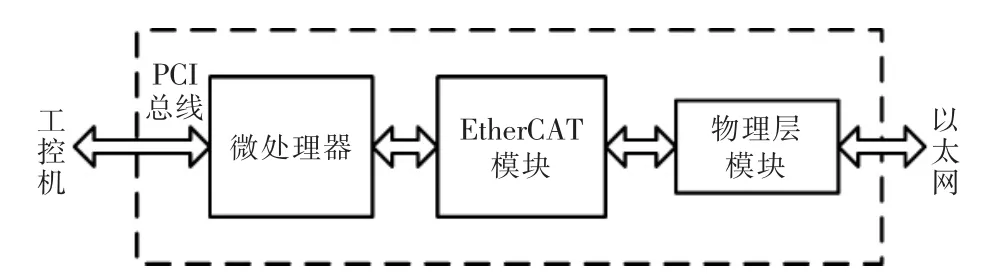

1 EtherCAT从站网卡组成框架

EtherCAT从站网卡由微处理器、EtherCAT模块以及网络物理层模块组成,其结构如图1所示。其中,EtherCAT模块由EtherCAT协议控制器组成,用于实现物理层与数据链路层。文中选用倍福公司ET1100作为EtherCAT协议控制器;微处理器由FPGA芯片实现,选用Altera公司Cyclone IV系列的EP4CE6F17C8;物理层网卡芯片采用KS8721BL。

图1 EtherCAT从站网卡设计框架Fig.1 Design framework of EtherCAT slave network card

2 从站网卡硬件设计

系统硬件包括FPGA与ET1100的PDI接口模块、ET1100与以太网物理层PHY芯片的MII接口模块和FPGA的PCI通信模块。ET1100通过MII接口与以太网物理层芯片连接,再通过16位异步微处理的PDI接口与FPGA连接。从站网卡启动后,接收到来自主站的报文数据,FPGA通过内部运行的状态机与PCI和ET1100进行通信,完成工控机和主站的数据交互。

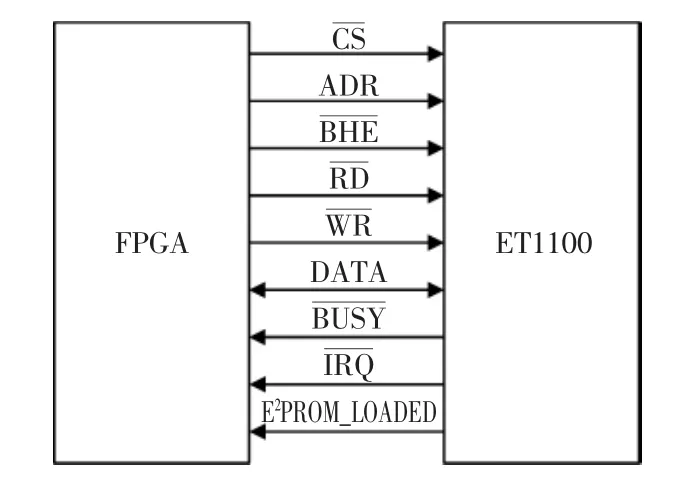

2.1 EtherCAT PDI接口

过程数据接口 PDI(process data interface)是实现从站控制器和应用之间的接口。ET1100支持3类过程数据接口,分别为数字量I/O,SPI从机、8/16位同步/异步微处理接口。PDI接口类型由寄存器0x0140—0x141进行配置[6]。在此使用16位异步微处理器接口与FPGA相连。

该总线接口使用复用的地址和数据总线,其ET1100和FPGA电路连接如图2所示。

图2 ET1100与FPGA硬件接口Fig.2 Hardware interface between ET1100 and FPGA

其工作原理为:当片选信号CS有效时,写或者读访问开始。如果处于写访问,地址ADR和数据DATA随着WR信号的下降沿而被置为有效值;写访问能通过WR信号或CS信号被置为无效。如果当前处于读访问时,地址ADR信号必须在RD信号的下降沿之前被置为有效值。读出的数据会保持有效值直到ADR,RD或CS信号变化。

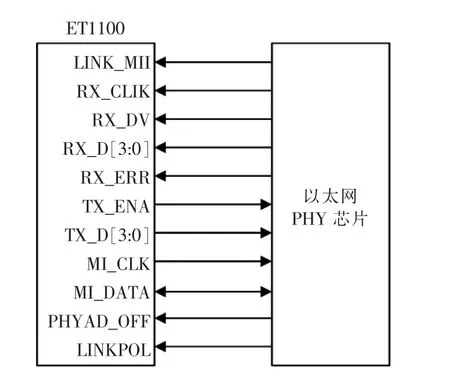

2.2 EtherCAT MII接口

ET1100可提供4个物理通信端口,每个端口都支持MII接口和EBUS接口。MII接口以工业以太网网线作为传输介质,可以与工控机直接相连,传输距离远,可有效传输100 m[7]。文中采用双MII接口,其ET1100和PHY芯片电路连接如图3所示。

图3 ET1100与PHY芯片硬件接口Fig.3 Hardware interface between ET1100 and PHY chip

2.3 PCI接口硬件设计

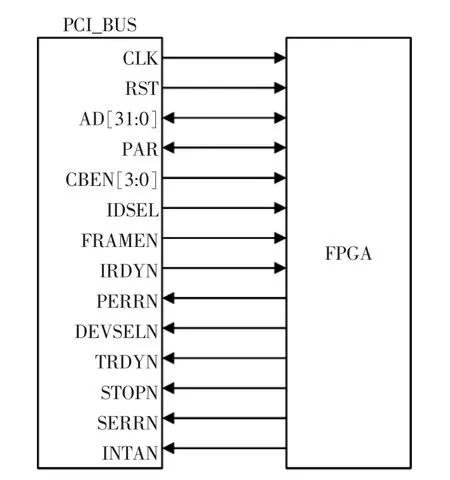

外设组件互连标准PCI(peripheral component interconnection),是由Intel公司1991年推出的用于局部总线的标准。PCI总线具有即插即用、中断共享、高速数据传输等功能[8]。其FPGA和PCI总线的电路连接如图4所示。

图4 FPGA与PCI总线硬件接口Fig.4 Hardware interface between ET1100 and PCI bus

PCI总线接口控制器设计中用到的信号,按照功能,可分为系统信号、地址数据信号、接口控制信号、错误报告信号和中断信号[9]。系统信号包括CLK和RST信号,提供系统时钟和系统复位信号。AD引脚为地址和数据的复用引脚。

3 从站网卡软件设计

根据从站网卡设计框架,需要对微处理器FPGA进行模块化、标准化的编程,其中包括对FPGA顶层模块框架的结构化设计,并根据逻辑操作需求设计合理的状态机,提高设计的通用性[10]。

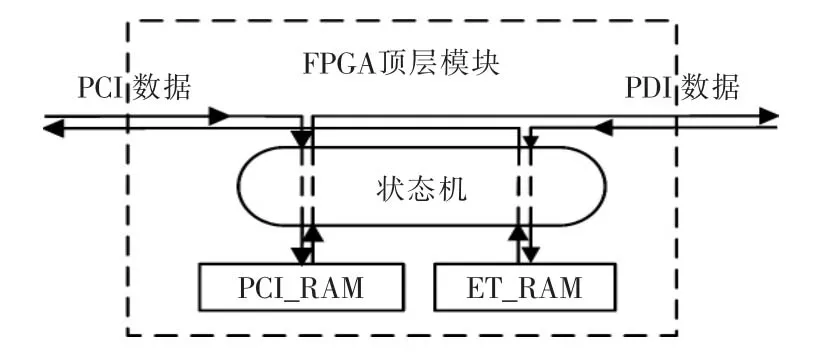

3.1 FPGA顶层模块框架

在FPGA顶层模块的设计中,首先设计接口模块,使用FPGA提供的IP核构造PCI总线,用于实现读写PCI数据的功能。

在FPGA的程序开发中,由于PCI总线、PDI接口以及FPGA顶层状态机处于3个不同的相互独立的时钟中,传输速率不匹配,会导致数据丢失的情况发生。为此引入异步FIFO技术,用于存储、缓冲多个异步时钟之间的数据传输,实现不同时钟系统之间快速准确地传输实时数据[11-12]。使用FPGA提供的IP核,构造2个16位256双字节大小的双端口DPRAM模块用于实现异步FIFO,分别取名为ET_RAM和PCI_RAM。ET_RAM用于存储通过PDI接口从ET1100读取到的数据,PCI_RAM用于存储通过PCI总线读取到的数据。

由于存在多个数据组合逻辑以及寄存器逻辑,在FPGA的顶层模块中构建有限状态机实现预期的数据交互等逻辑操作。最终设计FPGA顶层模块框架如图5所示。

图5 FPGA顶层模块设计框架Fig.5 FPGA top-level module design framework

通过状态机不同状态迁移实现的逻辑操作如下:读取PCI总线数据并写入到PCI_RAM中,从PCI_RAM中获取数据通过PDI接口输出;读取PDI接口数据并写入到ET_RAM中,从ET_RAM获取数据通过PCI总线接口输出。

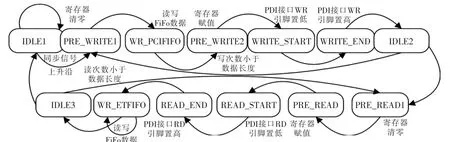

3.2 FPGA状态机

状态机是整个软件设计中最核心的部分,各种控制、数据交换、命令都在状态机的管理下进行[13]。状态机一方面将存入FIFO数据结构中的PCI输入信号通过PDI接口发送出去,另一方面将读取PDI接口的输入信号存入FIFO,使应用层用户能够顺利的执行读写操作,完成数据交互。状态机通过设置数据长度,对多字节数据进行连续的读写操作,极大程度地提高读写效率。

该状态机共由13个状态组成,采用异步复位方式,所有的状态转移都发生在时钟上升沿。具体的控制流程如图6所示。

图6 FPGA状态机Fig.6 FPGA state machine

4 测试验证

4.1 模块功能性测试

Altera公司Quartus 16.1软件中的SignalTapII在线逻辑分析仪,可以在线监视FPGA的数据引脚。Windriver是Jungo公司推出的一套设备驱动程序开发工具,可以对PCI总线进行配置和读写。Twin-CAT System Manager为倍福公司的总线配置工具,可以实现解析XML配置文件,管理从站状态,实现主从站之间数据的传输[14]。

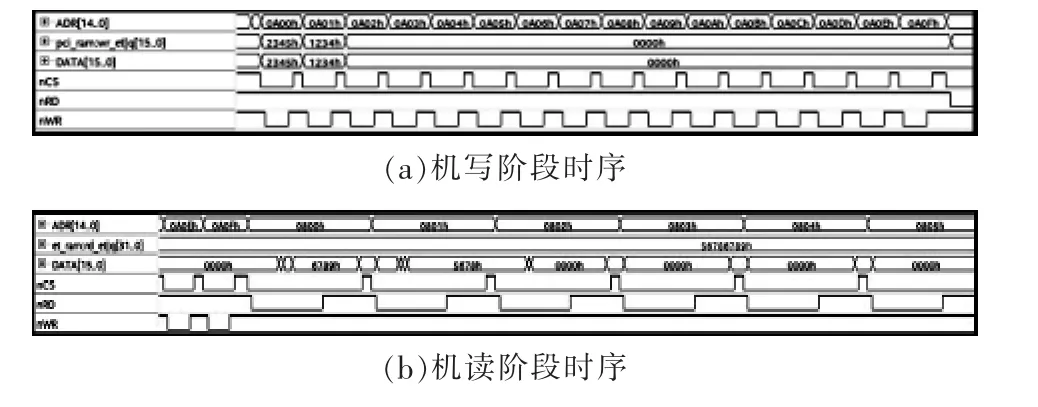

测试时,使用Windriver读写PCI总线数据,使用TwinCAT与从站网卡设备进行数据通信,使用逻辑分析仪监测FPGA状态机与PCI和PDI模块通信时是否正常运行。

首先使用Windriver工具识别PCI设备,再由TwinCAT识别从站设备并使其进入OP状态。使用Windriver向PCI设备的0xA00地址写入数据0x12342345。FPGA顶层模块获取到PCI数据0x12342345后,根据地址写入PCI_RAM。观察逻辑分析仪,当FPGA状态机进入PRE_WRITE1状态后,从PCI_RAM中根据地址获取到1个双字节数据0x2345;接着WR和CS引脚被置低,数据0x2345通过PDI接口写入ET1100中,WR和CS恢复高电平,写操作结束。数据长度为16个双字节,故此处循环写入16次。打开TwinCAT从站界面,正确读取到从站0xA00地址输出的数据0x12342345。

接着使用TwinCAT工具对地址0x800输入0x56786789。当FPGA状态机进入PRE_READ1状态时,RD和CS引脚被置低,通过PDI接口读取到ET1100地址输出0x800,输出数据0x6789,将此时的数据和地址值存入ET_RAM中,接着RD和CS恢复高电平,写操作结束。数据长度为16个双字节,此处循环读取16次。顶层模块会获取ET_RAM相关数据并输出到PCI总线中。在Windriver工具上正确读取到0x800地址的数据值0x56786789,测试过程中FPGA状态机逻辑分析仪读写阶段的时序如图7所示。观察控制信号和数据信号变化,可以看出数据传输过程准确且快速。

4.2 测试平台搭建

图7 FPGA状态机读写阶段的时序Fig.7 Timing of FPGA state machine reading and writing phase

为测试相机和工控机作为EtherCAT从站是否能正常工作,搭建了基于EtherCAT总线网络的机械手流水线抓取系统。工业相机将抓取到的图像数据通过千兆网卡传输到工控机端,经过图像处理得到机器人坐标值,再通过PCI总线传输到从站网卡中,主站通过连接从站网卡和机器人驱动器,实现机器人对流水线目标物体的抓取。经过试验测试,主站能正常接收到从站网卡发送的坐标值并控制机器人抓取目标物体。

在工控机上安装Wireshark网络数据包捕获软件,捕获上述主从站通信过程中收发的EtherCAT数据帧并进行统计分析,数据帧发送到转发的时间间隔为25 μs至几μs之间。这个时间包括从站接收数据帧、从站处理数据帧、从站转发数据帧的时间。可以看出该EtherCAT网络的实时性能够满足设计需求。

5 结语

作为一种工业实时以太网技术,EtherCAT因其高性能、高灵活性及完全开放性而引人注目。文中阐述了基于FPGA和PCI接口的EtherCAT从站网卡设计方案,并介绍了从站网卡软硬件设计细节,为开发从站设备提供了有力的参考。使用具有EtherCAT从站功能的FPGA板卡,通过PCI接口将工控机作为具有图像采集及图像处理功能的从站模块接入EtherCAT总线系统中,构建了一种工业相机和工控机融合的EtherCAT从站系统。该方案改变并拓宽了EtherCAT从站形式,通过试验验证了该设计从站能够很好地工作。