基于DDS技术的多功能信号源设计

2018-10-19毛群

毛 群

(阿坝师范学院电子信息与自动化学院,四川 汶川 623002)

0 引言

在通信、自动化或电测系统领域,如特种电源,电机控制等变频驱动中常用到高精度变频三相正弦信号源,同时,为适应不断变换的使用环境和对象,对信号源多功能性、稳定性及扩展性等方面也有更多需求。传统信号源设计常用模拟电路实现,模拟硬件对环境影响敏感,输出信号稳定性较差、频率范围小、扩展性差。近年来,信号源设计多采用DDS专用芯片加单片机等微处理器方案实现三相正弦信号输出[1-3],但其灵活性和可升级换代性能相对较差,本文在此基础上进一步改进,利用直接数字频率合成(Digital Frequeney Synthesis,DDS)[5,6]及 EDA 技术[7,8],采用自顶向下方法,以高性能数字器件FPGA芯片作为主要硬件资源设计多功能三相信号源[9,10]。

1 DDS技术基本原理分析

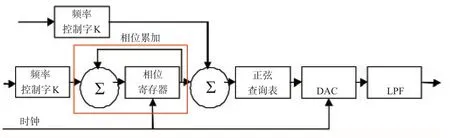

DDS技术理论基础是依据取样定理,对连续时间信号进行抽样量化,得到一个与频率相对应的相位序列,以此寻址,得到幅度序列,经数模转换获取模拟信号输出。结构如图1所示。

图1 DDS基本电路结构

DDS由参考时钟源,频率控制字,相位控制字,相位累加器,查询表、DA转换器和LPF构成[11-12]。参考时钟由高稳定度晶体振荡器或时钟源产生,作用是控制DDS各组成电路同步协调工作;相位累加器由加法器和相位寄存器组成,相位累加器是DDS系统中最重要的,其类似一个计数器,在参考时钟控制下,对频率控制字进行连续线性相位累加,合成信号的相位即相位累加器输出数据,DDS输出信号频率即相位累加器溢出频率;正弦查询表是一个可编程只读存储器,用于存储一周期的波形幅值;相位控制字控制输出信号初始相位,把相位控制字和相位累加器求和数据作为地址对正弦查询表寻址,查询表把输入地址相位信息对应到波形信号幅度上,从查询表得到代表波形信号幅值的离散量化值,经数模转换和低通滤波器(LPF)滤波,得波形信号[13],故DDS是以数控振荡器方式产生频率、相位可调波形的一种信号合成技术。

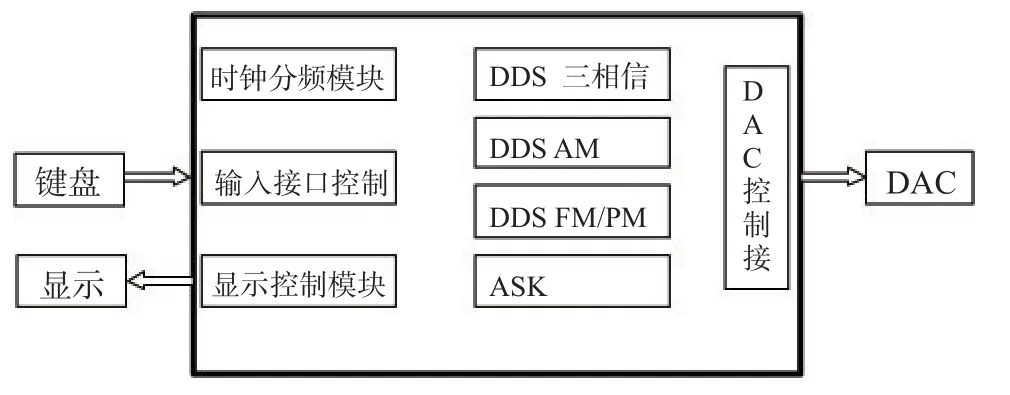

2 信号源系统设计

信号源系统设计以FPGA为核心[14],如图2所示。系统设计指标:(1)产生同步输出相差120°三路正弦信号;(2)三相正弦信号频率范围50~1 KHz,频率可调;相位差不随频率变化发生明显变化;(3)语音信号频率300 Hz,载波频率100 K,调制度0.5,输出AM调制波形;(4)能实现FM调制、ASK调制。

图2 系统组成框图

2.1 三相正弦信号FPGA设计

2.1.1 系统时钟设计

系统时钟50 MHz,利用计数器分频获得8 Hz,1 KHz,1 MHz三个时钟信号,分别用于扫描按键输入、数码管动态扫描和控制DDS系统工作。

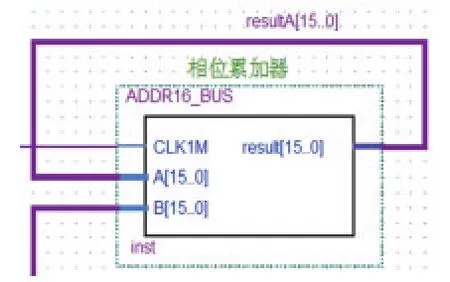

2.1.2 相位累加器设计

改变ROM的地址即可输出对应波形信号,信号频率计算如DDS方程(1)所示

式中fout输出频率,fc采样时钟,N相位累加器位数,K频率控制字。根据要求:欲三相正弦信号输出频率范围50~1 KHz,累加器按步进为1(频率控制字K=1)累加直至溢出一遍频率即为频率步进值[5],也是输出信号最低频率,当N取16,最小输出频率可达15 Hz,满足系统最低输出50 Hz要求,由输出频率达到1 KHz,可得三相正弦信号最大频率字输入K=66,为使输出波形不失真,频率控制字位宽取7位,高位添0,加法器为16位[6],本设计中存储器深度256字,地址线和输出数据线均8位,取相位地址输出高8位寻址,舍低位,相位累加器位宽取16位,时钟控制下对频率控制字累加,相位累加器累加结果高8位作为正弦ROM地址。

2.1.3 三相相位控制器设计

由DDS原理,改变相位控制字可控制信号相位偏移,因此通过相位控制字模块设计实现三个正弦波初始值设置。欲实现相差120°三相正弦信号,原理同单相,只需增加两个具有固定相偏的相位控制加法器控制基准信号外的两路信号初始相位,及三个波形数据存储器[7],利用相位控制字设置三个正弦波初始值。相位偏移公式见式(2)。

式中Poffset相位偏移量,Pc相位控制字。具体设计:相位加法器字长位宽N取8,由式2计算三个相位偏移量分别为P1=0;P2=28×120°/360=85.3°,取整85;P3=28×240°/360°=170.6°,取整171,设定上述相位偏移量,可实现相差120°的三相正弦信号[8]。

图3 相位累加器

图4 三相相位控制器

2.1.4 波形存储器设计

通过Matlab或C生成.mif数据文件作为ROM内波形数据文件[15],采用调用QuartusII的宏功能模块LPM_ROM完成ROM设计。

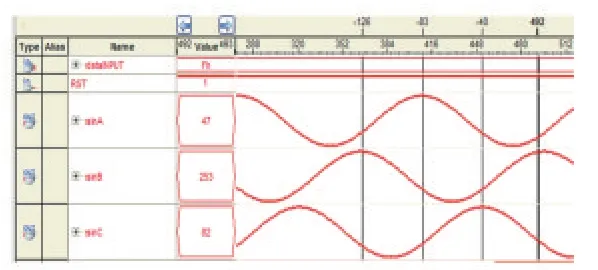

按DDS原理,调用上述模块元件进行三相正弦信号顶层设计,例化成三相正弦信号模块如图5,仿真图6表明设计正确。

图5 三相正弦信号发生器模型

图6 三相正弦信号仿真图

2.2 AM和FM的FPGA设计实现

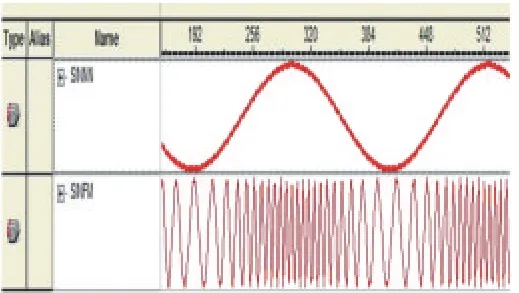

结合DDS技术和幅度调制(AM)、频率调制(FM)原理,采用DDS实现AM、FM调制电路[16-17],AM设计模型和仿真见图8和图9,FM设计模型和仿真见图8和图9。

图7 AM电路

图8 AM仿真

图9 FM电路

图10 FM仿真

2.3 ASK调制的FPGA设计实现

调制解调模块设计:由随机序列发生器产生随机二进制序列,送给ASK调制模块,调制输出信号,再送给解调模块解调,还原随机序列,设计原理图如图11所示。

图11 ASK调制解调原理图

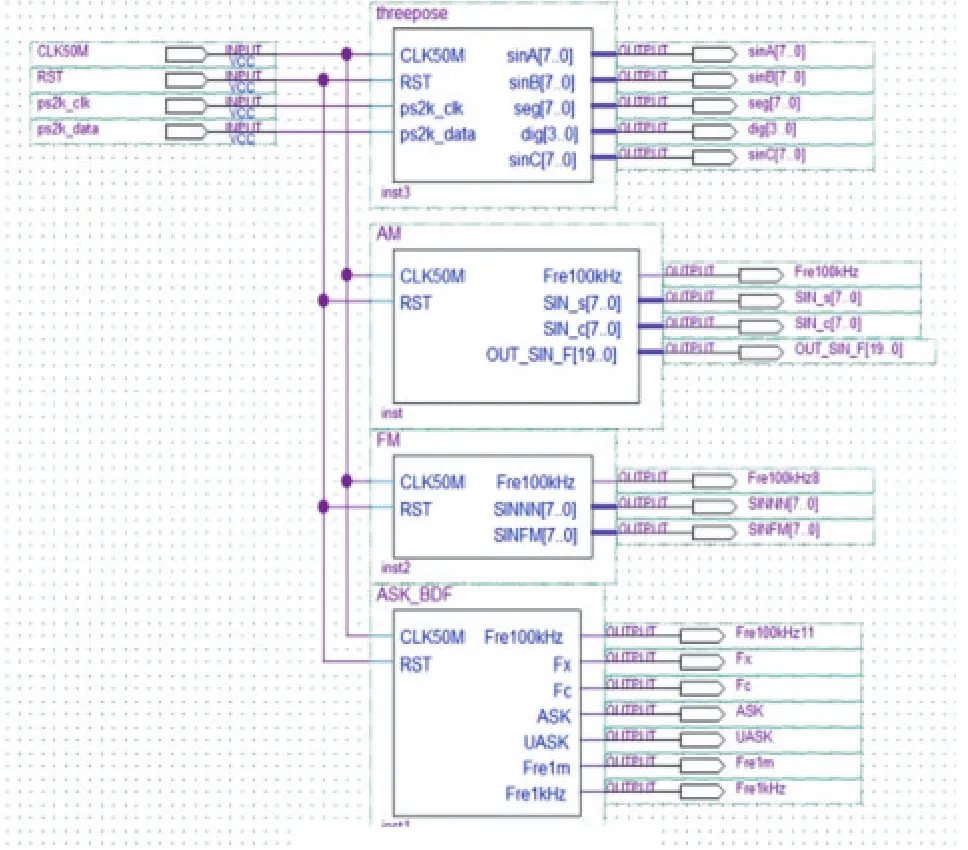

2.4 系统FPGA设计实现

采用层次化设计方法,综合各功能模块,可得信号源,设计原理图如图12所示。

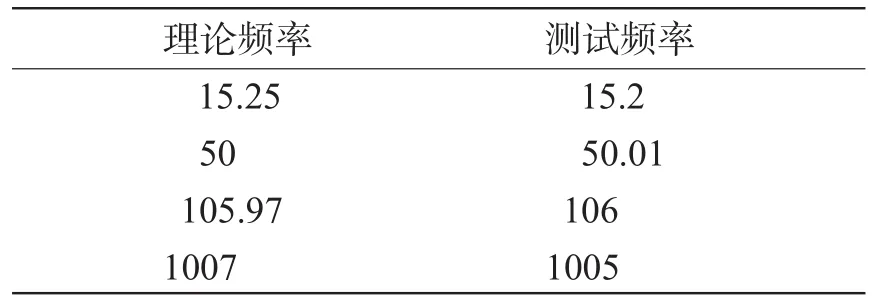

3 系统指标测试

三相正弦信号示波器测试数据见表1,利用每两路信号峰峰值时间差可判定,信号间相位互差120°,输出频率越高,输出波形质量相对变差,这由周期内采样点数变化引起。AM,FM,ASK调制仿真测试成功,满足系统设计要求。

图12 系统原理图

表1 三相正弦信号频率测试表Hz

4 结语

利用FPGA可重构特点以及ROM的可编程性,改变存储波形可以实现任意波形三相信号发生器,同理,本设计的AM、FM模块调制信号及ASK调制解调信号也可以灵活更改,还可在现有硬件资源上增加PSK,FSK等高精度数字调制和正交调制,以适应更宽领域需求。