基于FFT的DBPSK多路并行接收机设计

2018-10-18赵敏荐候号前

刘 皓,赵敏荐,候号前

(电子科技大学通信抗干扰技术国家级重点实验室 成都 611731)

大规模并行接收机能够并行接收并解调一定带宽范围(宏通道)内,调制在不同载波子信道的大量时域混叠信号,这些时域混叠的信号来自不同的发送端[1-2]。在诸如传感网络等用于大量发送节点应用中,多路并行接收机能够满足大量发送节点的并行处理需求。

本文提出了一种高效的基于FFT的多路并行下变频算法,借助FFT的高效结构,资源消耗少,且结构简单易于实现。将该算法应用于DBPSK系统中,实现了上千路DBPSK发射信号的接收与解调,最终使用Xilinx FPGA完成硬件平台的搭建和测试,并取得了良好的性能。

1 DBPSK多路并行接收机

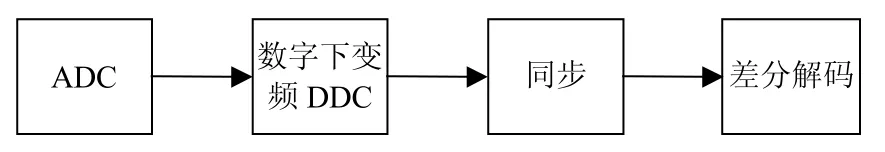

传统的DBPSK接收机由射频前端接收数字中频采样信号,经过DDC模块完成单载波信道数字下变频,再由同步模块完成定时同步和频偏估计,最终完成解调,系统框图如图1所示。

图1 传统DBPSK接收机框图

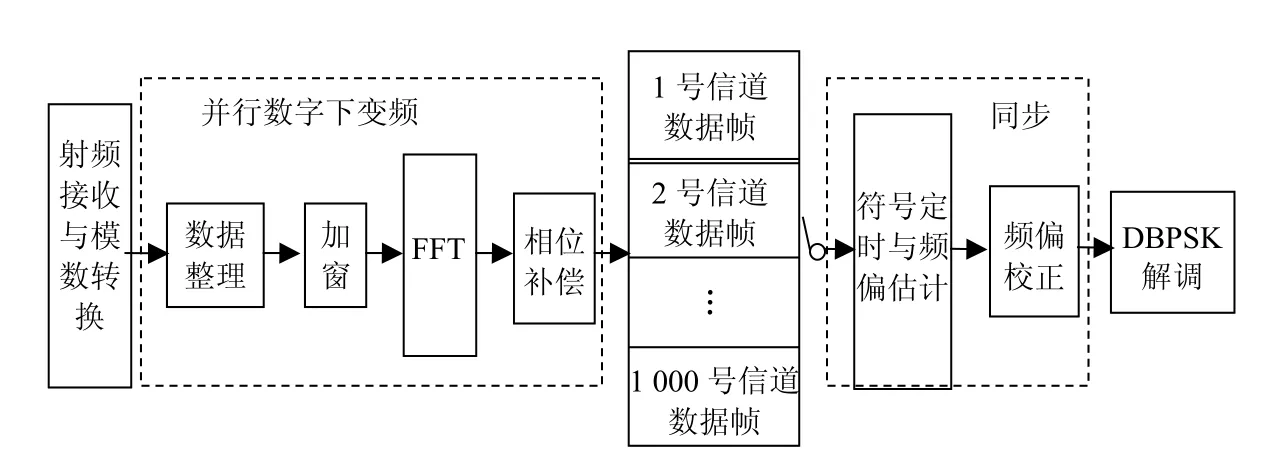

多路并行DBPSK接收机借助基于FFT的多路并行下变频算法可以完成上千路子信道的并行下变频计算,再经由同步和解调处理得到解调结果,从系统资源角度,同步和解调模块可以复用。其中多路下变频模块含:数据整理、加窗、FFT多路分离与下变频[3-4]、相位补偿。多路并行接收机[5-7]的处理流程如图2所示。

图2 多路并行DBPSK接收机框图

2 基于FFT的多路并行下变频算法

2.1 算法原理

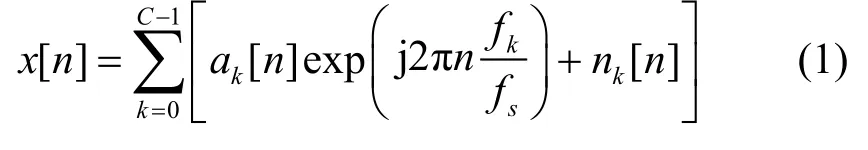

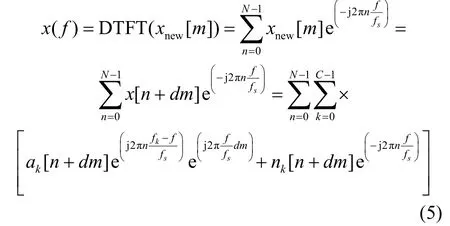

假设第k个子信道调制信号载频为fk,共有C个子信道,信号采样率为fs,输入复信号:

滑动点数d由中频信号采样率fs,信号波特率b和抽取因子D确定:

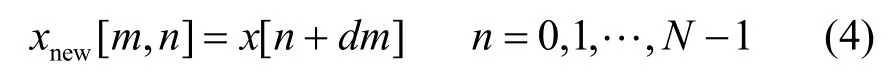

重组信号为:

式中,m代表组号;n代表每组数据中的采样点。该过程可以看作是使用长度为N的矩形滑动窗口对信号进行截断,并进行D倍抽取。对分组后的数据依次进行离散时间傅里叶变换(discrete time fourier transform, DTFT):

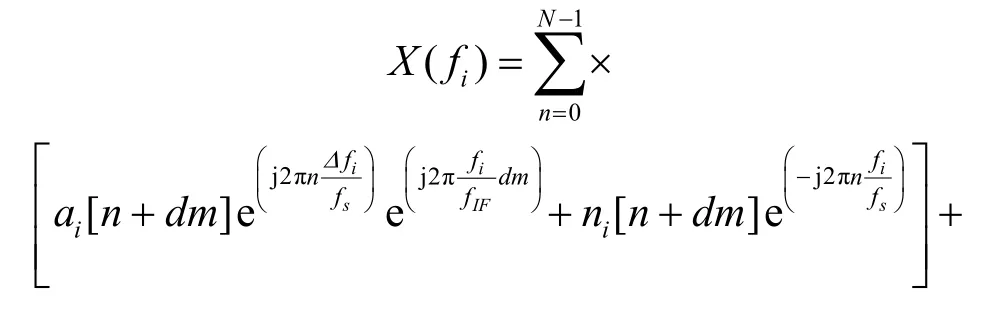

取第i个子信道的DTFT运算结果:

式中,Δfi为第i信道的频偏;第一项为第i个子信道的有效信号下变频结果,含信道噪声;第二项为邻道干扰。若不考虑邻道干扰和噪声,对应第k路的有效信号离散傅里叶变换(discrete fourier transform,DFT)结果为:

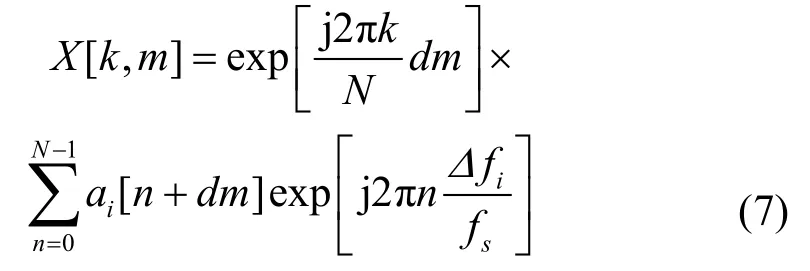

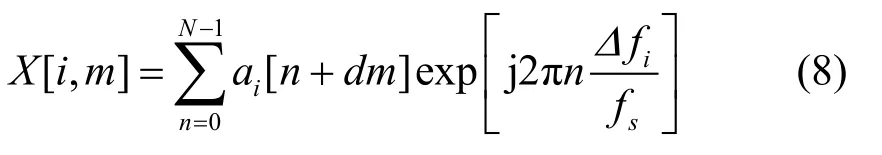

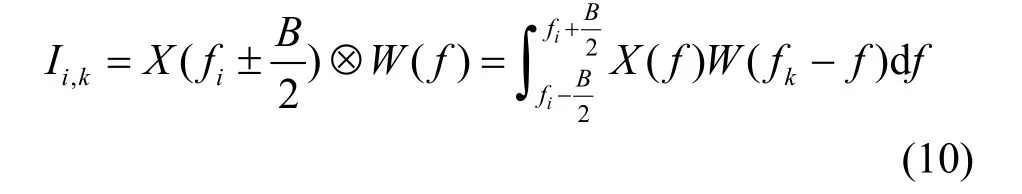

DFT的实现可以利用高效的FFT代替。需要进一步抵消相位增量,它来源于两部分,第一部分由频偏产生,需要在后续同步处理时频偏校正;第二部分由数据整理引入,通过每次FFT结果乘上相应信道的相位增量即可抵消。补偿后的结果为:

由此可以得出:通过数据整理,FFT运算和相位补偿,可以实现N路时域混叠的不同载波子信道信号的并行下变频计算,经过上述算法处理之后,即可按照一般接收机的设计完成同步与解调处理[8-9]。相对于传统下变频算法资源占用和设计复杂度大大降低。

2.2 并行下变频的邻道干扰抑制

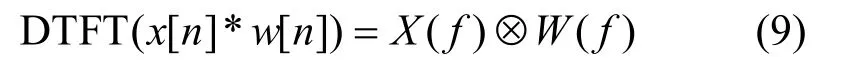

由于数据整理时域信号的截断效应,能量泄漏产生邻道干扰。影响接收机整体的接收性能。通过选择旁瓣衰减更大的窗函数,对整理后的数据加窗,可以有效地抑制邻道干扰。假设输入数字中频信号整理后为x[n],使用w[n]加窗。则对中频信号进行整理和DTFT运算可以表示为:

假设子信道带宽为B,那么信道i对信道k产生的邻道干扰为:

MATAB仿真4个相邻子信道发送信号时对中间信道产生的邻道干扰,通过对数据整理使用汉明窗,使得中间信道受到的邻道干扰下降了10 dB。

3 并行解调

3.1 并行解调原理

通过前面的分析,已知加窗可以有效抑制邻道干扰,假设在加性高斯白噪声(additive gaussian white noise, AWGN)信道中,不考虑邻道干扰和频偏,利用基于FFT下变频的第i路信号可以表示为:

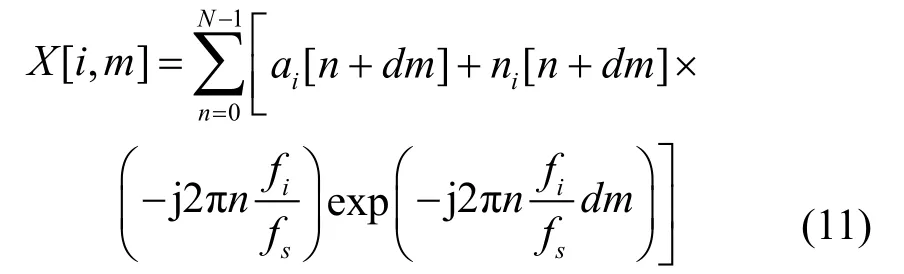

第i信道的频域噪声功率为:

式中,σ2为基带信号的噪声功率;N0/2为噪声双边功率谱。可以得到:

且对于二进制相移键控(binary phase shift keying, BPSK)调制复信号有:

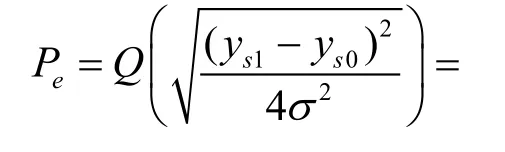

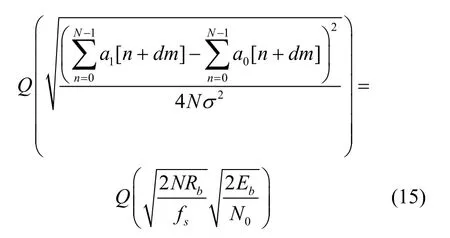

Ni仍然服从高斯分布,其方差为Nσ2。依据二进制脉冲幅度调制(binary pulse amplitude modulation,2PAM)的最小平均误码率有[10]:

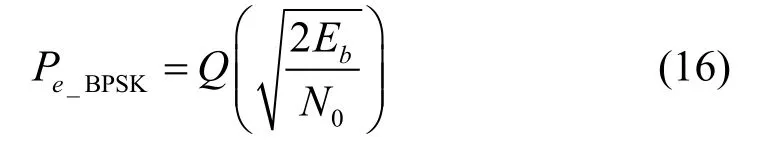

式中,Eb0为基带平均码元能量;Eb为载波调制后的平均码元能量;N0噪声功率。已知采用匹配滤波器的相干解调接收方法,BPSK理想误码性能为:

由于DBPSK调制采用差分解码,因此相较于BPSK调制,其误码率性能下降约3 dB。

由式(15)看到,与传统的BPSK接收机解调性能相比,基于FFT的并行多路接收算法可以通过选取合适的FFT点数N,达到与传统BPSK接收机相同的误码性能,但实际应用中存在的临道干扰会影响解调性能。

3.2 并行解调性能仿真

为了比较基于FFT的并行多路接收算法与传统接收机的性能差异,本文进行仿真。

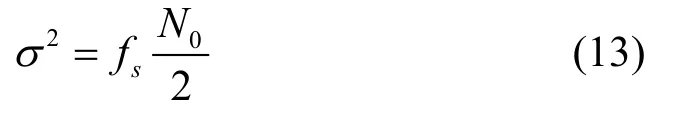

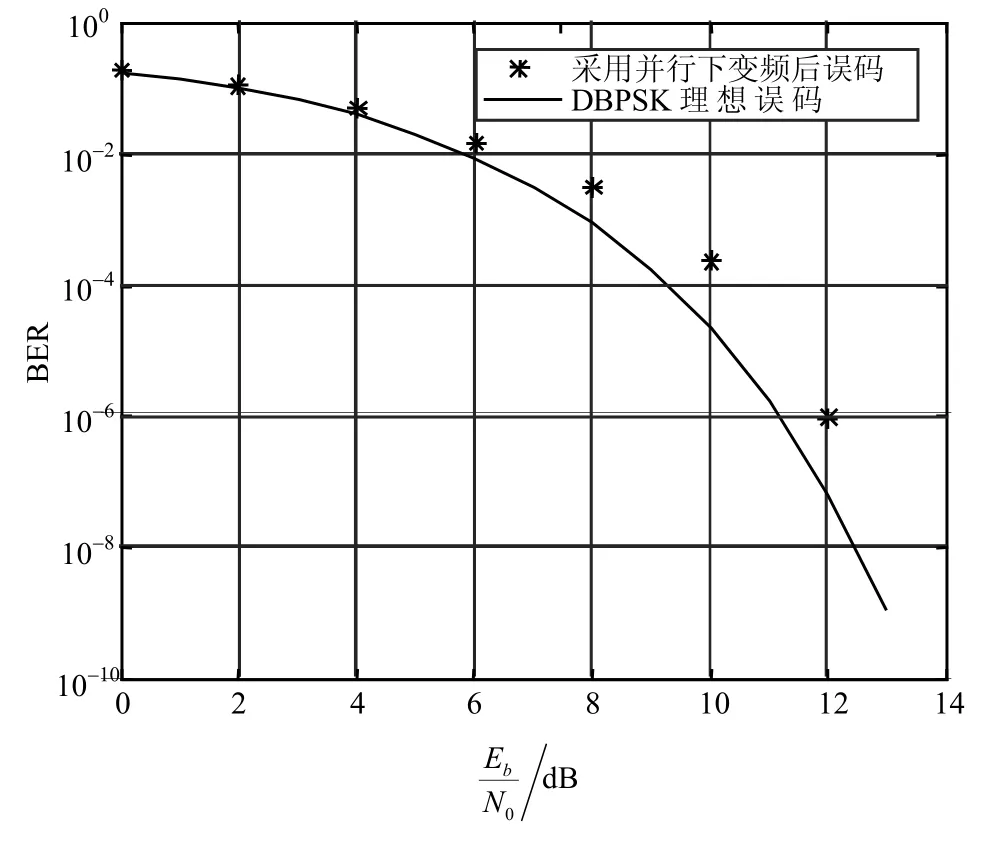

图3 基于FFT的多路DBPSK接收机误码性能

考虑发射端发送信号为DBPSK调制信号,数据波特率100 b/s,采用滚降因子为0.25的升余弦成型滤波器,基带子信道信号带宽125 Hz,相邻信道载频间隔为200 Hz,子信道间隔B=200 Hz,接收机为中频采样率的DBPSK多路并行接收系统,发射机在第500子信道(即载波频率1 kHz)上发送的信号,接收机设置FFT点数N=2 048。得出该系统参数下的解调性能,第500子信道的Matlab误码率曲线如图3所示。

仿真比较了传统DBPSK接收机的理想误码性能与基于FFT多信道DBPSK接收机的误码性能,可以看到相同误码率下传统接收机的信噪比与新算法相差1 dB,这是由于领道干扰和信号截断导致的能量泄漏引起的。仿真验证了基于FFT多信道DBPSK接收机[11-12]具有良好的解调性能。

4 硬件实现与测试

依据前文所述原理,完成了原型样机的硬件实现。基于FFT并行多路接收机的硬件实现方案采用了ADI公司的捷变收发器AD9361,借助其接收器功能,完成射频信号接收和模数转换。使用Xilinx公司的Kintex-7 FPGA KC705评估套件完成基带信号处理;采用基于微处理器(Microblaze)嵌入式架构实现配套的软件处理算法。

AD9361接收时域混叠的射频信号,转换为中频数字信号并传输到FFT并行下变频处理模块;经过FFT下变频处理后得到各子信道的基带数据,然后对各个子信道数据进行有效帧检测,提取有效帧信息;Microblaze启动直接内存访问(direct memory access, DMA)将完成有效帧检测的各路子信道数据存入双倍速率同步动态随机存储器(double date rate synchronous dynamic random access memory, DDR SDRAM)中;软件算法将子信道中的有效帧提取出来,利用DMA发送给同步模块以完成同步和解调;解调完成后进行循环冗余校验(cyclic redundancy check, CRC),Microblaze通过AXI4总线读取解调数据,并利用用户数据报协议(user datagram protocol,UDP)发送至网络终端。

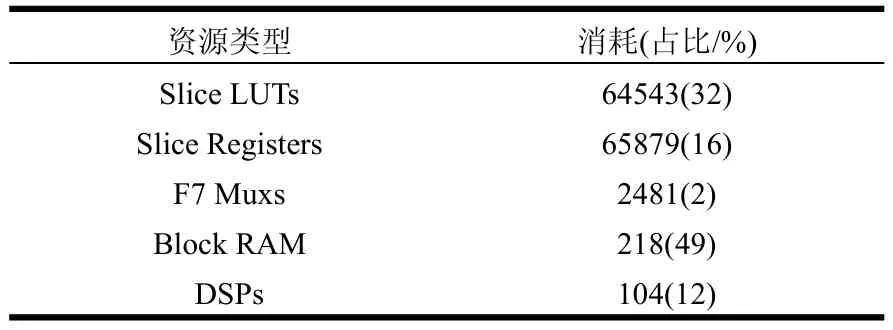

XC7K325T FPGA资源消耗如表1所示。

表1 设计资源消耗

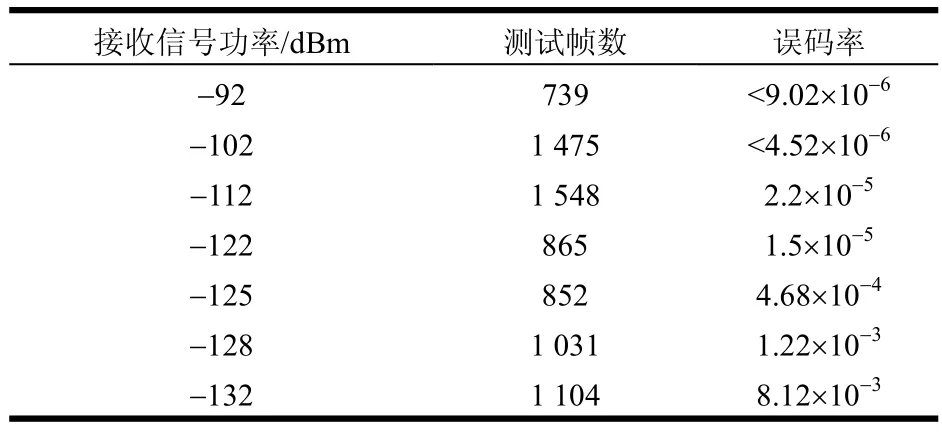

样机能够完成上千路子信道信息的接收解调,系统参数同3.2节仿真参数。表2给出FPGA实现接收机的灵敏度测试结果,实现接收机接收灵敏度低于−132 dBm。

表2 FPGA实现接收机灵敏度测试

5 结束语

本文提出了一种基于FFT的并行多路下变频新型算法,给出了分析和仿真结果,验证了算法的有效性。将该算法应用于DBPSK多路并行接收机设计中,得到了良好的性能。最后给出了基于AD9361和Xilinx FPGA的实现方案,验证了算法的可实现性和良好性能。该方法充分利用了FFT的高效实现,相对于传统的并行下变频算法具有资源利用率高、实现复杂度低的特点,且解调性能与传统DBPSK接收机性能仅相差1 dB,可以适用于大量终端节点并行通信的应用需求。