高分辨率程控宽带信号源的设计

2018-09-25杨保亮杨守良王鑫

杨保亮,杨守良,王鑫

(重庆文理学院电子电气工程学院,重庆,402160)

0 引言

信号源在测控、通信、导航、雷达、医疗等领域应用广泛,频率精度、稳定度、相位是一个信号源中的重要指标。传统的波形发生器产生的波形少,精度低,而且体积大,灵活性差[1]。直接数字频率合成是20 世纪60 年代末出现的第三代频率合成技术,它的频率转换速度快,频率分辨率高,并在频率转换时可保持相位的连续。目前,市场上出现了许多DDS专用芯片,而DDS专用芯片输出波形种类单一,频率、幅值相位等参数不可调节,不能灵活满足于实际需求[2-3]。利用FPGA的高速、高性能和可重构性可实现各种比较复杂的信号源功能[4]。本文在深刻剖析DDS的基础上,利用单片机和FPGA实现一种组合型的DDS信号源,实验证明,该信号源可以产生高速度、高带宽、高分辨率、相位连续高的信号源,该波形发生器结构组成比较简单、由于采用采用在线编程技术,功能灵活可变,可以任意的扩展。

1 DDS原理分析

正弦波的主要组成要素是幅度、相位、频率,其中幅度不符合线性规律,但是它的相位符合线性增加的规律,DDS根据这里规律来产生正弦信号的,主要由N位的相位线性累加器和寄存器构成,在工作的时候,相位累加器在时钟脉冲控制下不断对频率控制字K进行累加,然后将累加器的数值作为波形存储器ROM的地址,获取波形存储的波形数据,最后对得到的数据进行一定调幅、优化、数模转换、滤波等调理进一步得到理想的波形信号。DDS的原理如图1所示。

图1 DDS原理框图

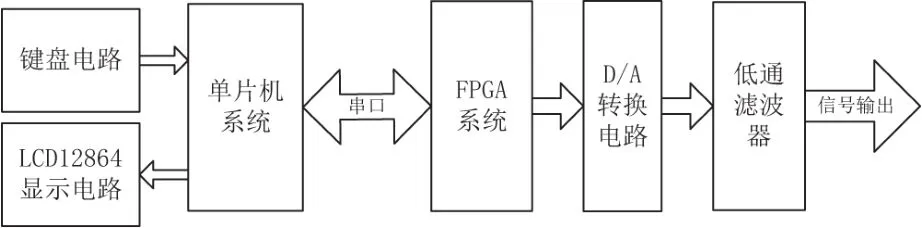

2 设计框图

本设计以FPGA为核心设计DDS信号源,低速的部分采用经典的单片机进行处理,然后通过串行通信和FPGA进行信息的交换,系统设计总框图如图2所示。总体方案的主要包含FPGA、单片机、D/A转换、滤波、输出和输入等六个部分。其中FPGA子系统部分主要完成DDS核心模块的实现;单片机、键盘、显示电路主要完成频率控制、带宽设置、分辨率设置等功能;D/A转换以及滤波电路主要完成将数字信号转换为模拟信号,得到光滑的波形信号等[6]。

图2 系统设计总框图

3 DDS模块设计

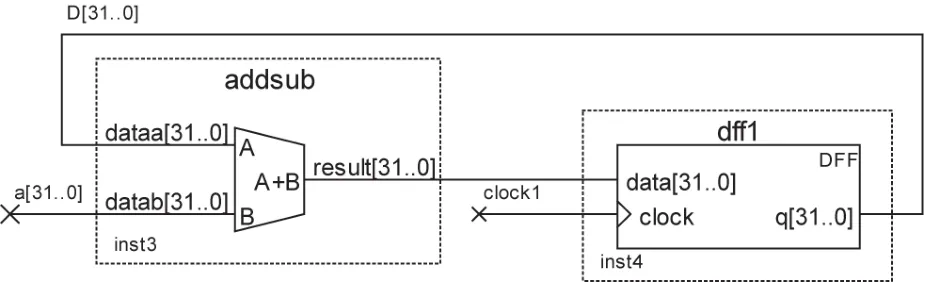

3.1 相位累加器模块

相位累加器是DDS的核心模块,其主要用于产生查找ROM表的地址,从而输出储存在ROM中的相位幅度值。本设计相位累加器位数N设为32,FPGA输入频率为50MHz,通过锁相环可以把频率增大到250MHz。故频率分辨率为0.058Hz。根据设计要求可调步长为1Hz,且0.058*17≈0.986,故每次增加17,即可实现1Hz的增长。由于所设计的字长N=32,故采用一个32位的加法器以及一个32位的D触发器构成相位累加器,其输出值在同步时钟的控制下按照所给输入频率字长进行递增。相位累加器模块原理图设计如图3所示,其中a[31..0]为频率控制字输入引脚,D[31..0]为累加器输出。

图3 相位累加器原理图

3.2 FPGA与单片机的接口通信设计

为了进行对DDS各种参数的设定,需要接收外部输入设备的命令,但是由于输入设备低速直接接到FPGA会影响其性能,因此采用了单片机获取输入设备的参数,然后通过单片机的串口把相应的数据传递给 FPGA。由于单片机的串口每次只能发送8位的数据,而接收频率控制字的加法器和数据寄存器都是32位的,故我们需要单片机需要把32位的频率控制字分为4个8位数据由高位到低位连续发送四次给FPGA系统。

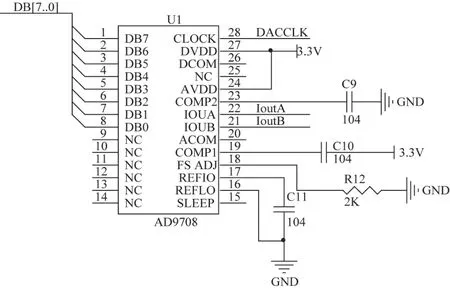

4 DA转换电路设计

DAC芯片是系统波形产生过程中的核心器件,根据系统对带宽和分辨率的参数的要求设计要求,我们选用AD公司的AD9708芯片,该芯片是一款8位,125Mbps的DA转换芯片,内置1.2V的参考电压,差分电流输出,其外围电路如图4所示。为了提高AD9708芯片输出电流的稳定性和抗干扰能力,设计电路中接入了7阶巴特沃斯低通滤波器,带宽为40MHz。

由于AD9708转换结果是以电流形式输出。我们需要的是一个电压信号,这里通过个高输入阻抗的线性运算放大器把电流信号变换成电压信号的,本设计中选取了145MHz带宽的高性能运放AD8065,同时该电路具有差分变单端、幅度调节等功能。AD8065是常用的单路电压反馈型放大器,它具有FET输入功能,可实现5-24V电压变换。在实际的应用中,输出波形的幅度一般是可变的,为此,我们有设计了反相比例放大电路单片机,反馈电阻选用的是5K大小的电位器,电流转电压以及电压幅度调节电路如图5所示。

图4 AD9708应用电路

5 系统测试

根据设计需求搭建好系统的硬件后,在软件设计过程中,首先根据模块的思想进行程序设计,编译成功后,把•sof文件下载到先前搭建硬件电路中的FPGA芯片,通过RIGOLDS1022C数字示波器对输出各种波形、频率进行了测试和观察。通过示波器观察到的高频信号波形如图6所示。高频段(1MHz以上)三角波、正弦波、方波输出波形。图6 信号源输出波形

图5 电流转电压以及电压幅度调节电路

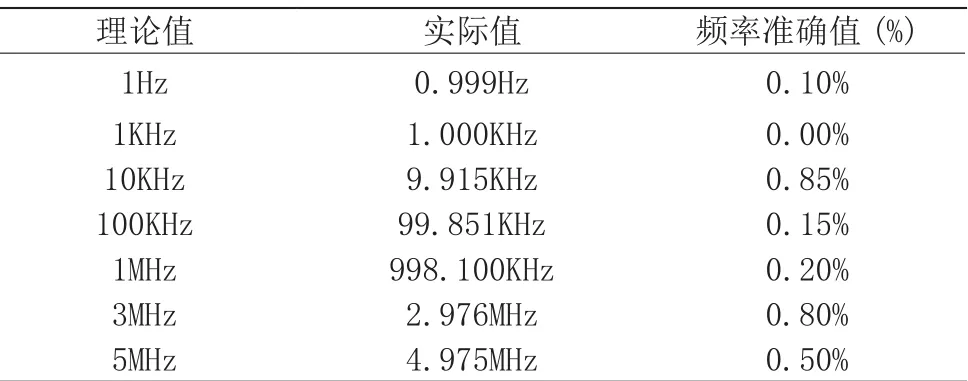

本设计可以实现的信号频率范围是1Hz-5MHz。从图7可以看出,本设计输出波形的频率为2MH、电压的最大值1.0V,所以频率准确度比较高,并且波形无明显失真。以正弦波为例,记录其13个频率输出值,并对输出频率的准确度进行分析,如表1所示。

表1 正弦波输出频率准确度分析

通过计算得出输出信号的平均频率准确度为0.34%。从实验结果可以看出,本文设计实现方案结构简单、修改方便、能够实现多种频率可调而且输出波形的质量高,能够满足一般测试和设备的需求,具有一定的市场。

6 结论

本文提出基于高速FPGA与低速单片机双核的DDS设计方案,然后详细描述了DDS的工作原理、电路的结构、设计基本思路以及实现方法,最后系统方案的要求搭建了硬件和软件,主要包括参数计算、电路图设计、程序设计等。经过仿真、实物测试,结果表明输出波形频率可调范围宽、波形稳定,总体达到设计指标,可以直接作为信号源使用。