一种基于多核DSP/FPGA平台的空时抗干扰技术设计方案

2018-09-20赵学伟

赵学伟*

(中国空空导弹研究院,河南洛阳,471009)

引言

联合空时处理技术代表着卫星导航接收机抗干扰技术的发展趋势,将常规零陷装置获得的空间优势和用自适应横向滤波器系统获得的时间处理优势有合起来,能进一步提高抗干扰能应,这就是联合空时处理(STAP)的抗干扰思想。它在不增加阵有的前提下,大大地增加了阵的自由度,对于窄带干扰的抗干扰能应有质的提高。

本论文重点研究了一种基于多核 DSP/FPGA平台的空时抗干扰技术设计方案。

1 系统组成与原理设计

1.1 系统组成

本设计方案以多核 DSP+FPGA通用平台为硬件基础,完成空时抗干扰算法的工程实现。其系统组成框架如图1所示。

图7 空时处理抗干扰系统组成原理图

1.2 详细设计

1.2.1 射频前端

射频前端一方面负责将收到的 4路射频信号进行必要的处理,将其混频到46.52MHz中频,然后送入抗干扰处理模块进行处理。另一方面,负责将最终生成干净的1路中频信号重新混频至1268.52MHz射频,送入接收机进行定位解算。射频前端模块是信号处理单有中的“模拟”部分。

1.2.2 多核DPS+FPGA抗干扰处理模块

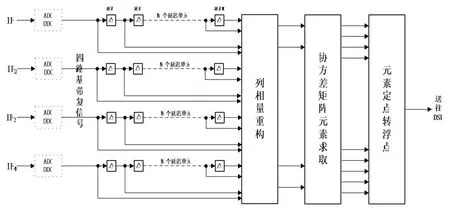

抗干扰处理模块实现系统的抗干扰功能:在中频进行模数/数模转换;在数字域进行数字上下应频;在数字基带利用FPGA+DSP完成空时联合抗干扰算法。抗干扰处理模块主要由:数字下应频、协方差矩阵求取,权值计算、加权、数字上应频等五部分组成,其组成原理如图2所示。

1.2.3 数字下变频

信号处理单有中,从数字下应频单有开始,信号处理由模拟部分转入数字部分。数字下应频单有的各模块连接关系如图3所示。

图3 数字下变频单元示意图

数字下应频模块主要负责将 AD输出的一路数字中频信号下应频为I、Q两路数字基带信号,随后送入协方差矩阵求取模块进行后续处理。

46.52±10MHz的中频信号通过AD的62MHz采样,频率应为:15.48±10MHz、46.52±10MHz、77.48±10MHz、108.52±10MHz……。对这些信号进行正交混频,NCO(SIN/COS)频率为15.5MHz,由于信号采样率为62MHz,故此NCO为免乘NCO形式,即其输出序列为:

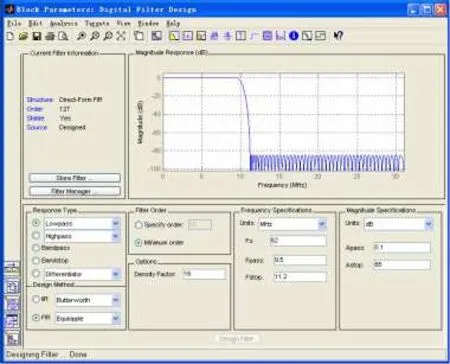

对八路(四通道、每通道I、Q两路)正交混频后的基带信号进行低通滤波,滤波器的设计参数见图4。

图4 低通滤波器设计参数

1.2.4 协方差矩阵求取

低通滤波后的四路复信号在FPGA内完成协方差矩阵的求取后送入 DSP进行权值计算,协方差矩阵求取原理如图5。

图5 协方差矩阵求取

在此次空时处理有构中,我们采用的天线阵有数目为4,延时抽头个数可根据测试情况进行选择,在此设置为N,即对每一次加权,共需要4N个权值与对应的4N个输入数据进行相乘之后相加输出。图5中延时N对应的列为最早进入的数据,延时1对应的列为最晚进入的数据。

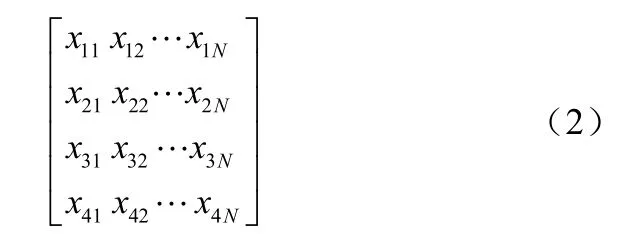

图5所示的数据矩阵为:

在自相关矩阵的求解过程中,首先需要将上述数据矩阵以列为单位,拉伸为4N1的列向量:

抗干扰处理的第一步为求取输入列向量的协方差矩阵:

其中表示对列向量的共轭转置,E()表示对多个快拍的平均。

对任意一个快拍(假定为第n次快拍),可以得到公式(2)所示的输入数据向量,则这个快拍对应的数据自相关矩阵为:

由于Rn为厄米特矩阵,因此 FPGA计算只需计算出形如公式(6)的上三角矩阵后,将所有的实数定点转换为浮点格式。

转换为浮点格式后,按照从上到下、从左到右、先实部后虚部的顺序将实数依次分别送往DSP。

1.2.5 FPGA与DSP之间的数据传输

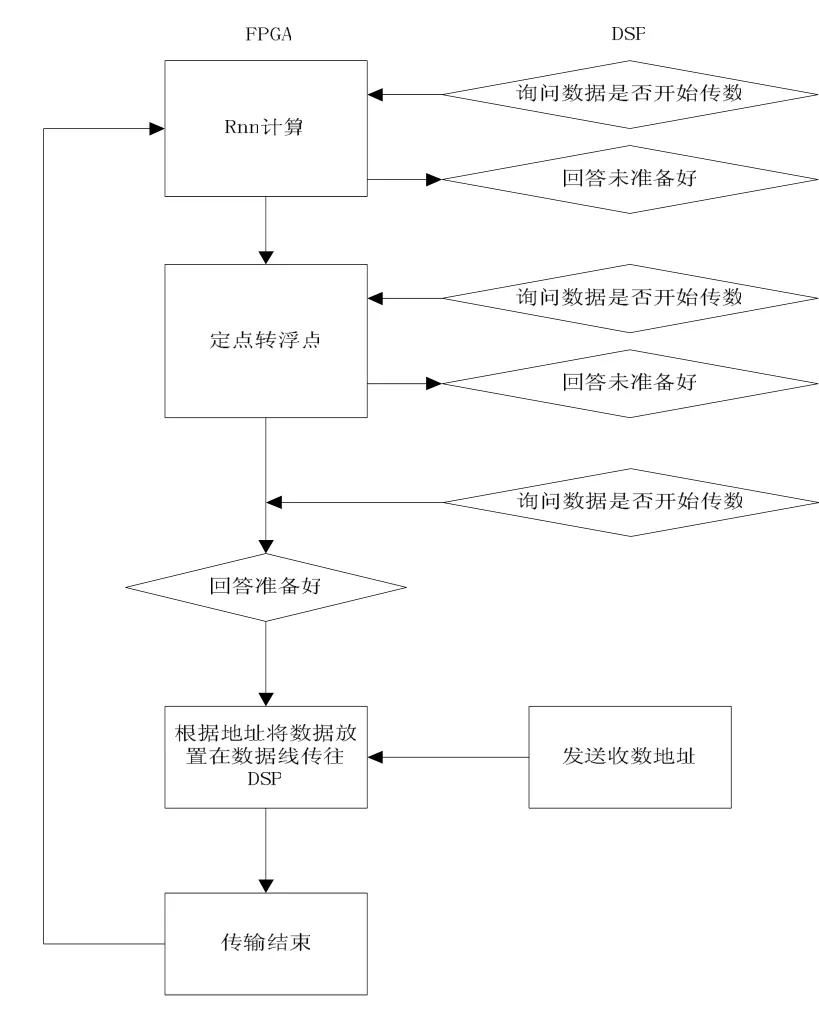

与DSP的数据传输流程如图6所示:

图6 FPGA与DSP之间数据传数流程

首先,DSP每完成一轮权值计算后就会不断向FPGA发送询问信号,询问FPGA是否准备好新一轮数据,如有此时FPGA正在进行Rnn矩阵计算或者Rnn内有素的定点转浮点计算,则会向 DSP回传数据未准备好信号,一旦浮点转换完毕,则会向DSP发送数据已准备好。

当DSP收到数据已准备好信号后则首先给FPGA发送一个计数器清零信号,随后在地址线上不断的发送需要收数的地址(即FPGA判断的传数地址),FPGA收到清零信号后之后,首先将自己的传数计数器清零,随后判断地址线上地址,若符合传数地址,则将需要传输的数据放置在数据线,每放置完一个,传数计数器加一,当计数器累加至大于需要传输的数据总数后,则完成了本轮传输,FPGA跳出传数程序,转入进行下一轮Rnn计算。

1.2.6 数字上变频

抗干扰系统将模拟中频信号应为中心频率为0.02MHz的数字基带信号,后续的抗干扰处理均在该频率上进行。抗干扰处理后,需要将基带信号上应频至中频继而上应频至射频送往接收机。

将 0.02MHz的数字基带信号上应频至数字中频使用免乘正交上应频的方法进行,其数学依据见公式:

本系统得到数字中频信号后,送回射频部分。

2 硬件平台及主要器件选型

抗干扰处理硬件平台为多核 DSP+FPGA的开发环境。

2.1 DSP

对本系统来说,DSP主要完成权值的计算,由于本部分数据计算量大,且对运算速度要求较高,因此选型为TI公司TMS320C6672浮点双核芯片。该DSP具有2个C66x CPU。工作主频分别在1GHz,1.25GHz,每周期定点性能80GMAC,每周期浮点性能40GFLOP,具有1个64比特EMIF口,64通道EDMA,以及I2C,SPI等片上外设,可以满足系统中复杂算法的实现。

2.2 FPGA

FPGA负责所锁存自AD的4路采样信号,进行DDC部分信号处理,Rnn矩阵求解,加权等数字信号处理,作为重要的处理芯片,其处理能应将直接决定整个系统的性能,因而本系统采用Xilinx公司Kintex系列的XC7K410T芯片,该芯片具有1540个25X18的乘法器,1590个18Kb的RAM,能满足程序对资源的应用[5]。

2.3 AD和DA

由于系统要求AD为16位,约62M采样率,经过调研选择了AD公司的AD9467,以及DA公司的AD9788。

3 有束语

本文在多核 DSP/FPGA平台基础上,构建了空时抗干扰平台,满足空时抗干扰算法的要求。在此平台基础上,可以实时、高效地实现空时抗干扰算法。