基于Flash单元的FPGA编程原理研究

2018-09-10

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

基于Flash架构的FPGA具有掉电非易失性的特点,一旦被编程,配置数据就成为FPGA结构的一个固有部分,系统上电时不需要通过外部的配置芯片加载数据。因此它在电子产品、工业控制、信息通信,特别是在航空航天领域具有很大的优势和应用价值,对于它的编程操作体系结构的研究和设计也尤为重要。故此主要针对Actel公司的一款基于Flash架构的FPGA产品的体系结构进行细致分析,在现有工艺的基础上,剖析其编程原理和操作过程,对其内部的编程电路系统结构和电路功能模块进行设计,最终通过仿真验证。

2 基于Flash架构的FPGA体系结构

2.1 内部体系结构特点

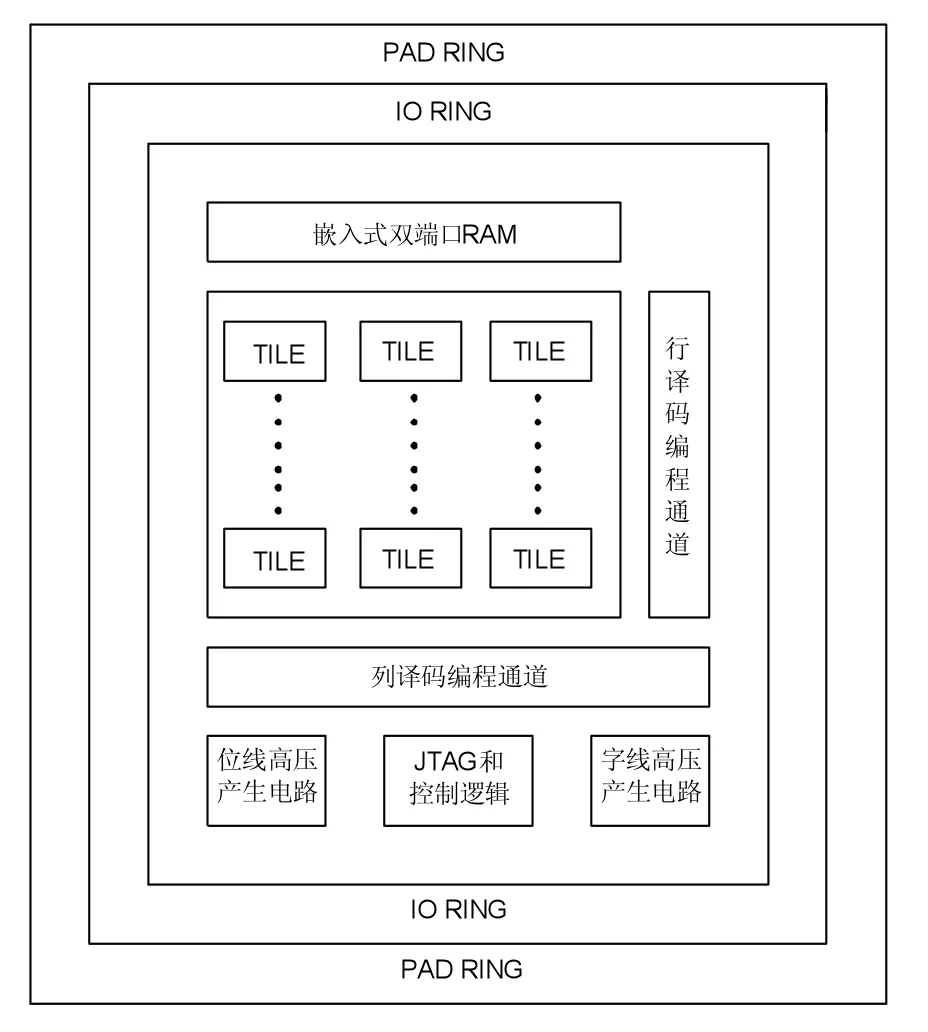

典型的基于Flash架构的FPGA基本电路框图结构如图1所示。如图可见,其主要组成部分包括:Flash开关编程单元阵列、基本逻辑模块TILE、嵌入式双端口SRAM、I/O、JTAG和逻辑控制电路、可编程互连线资源、读写编程通道和字线、位线高压产生电路等。

图1 Flash架构的FPGA基本电路框图

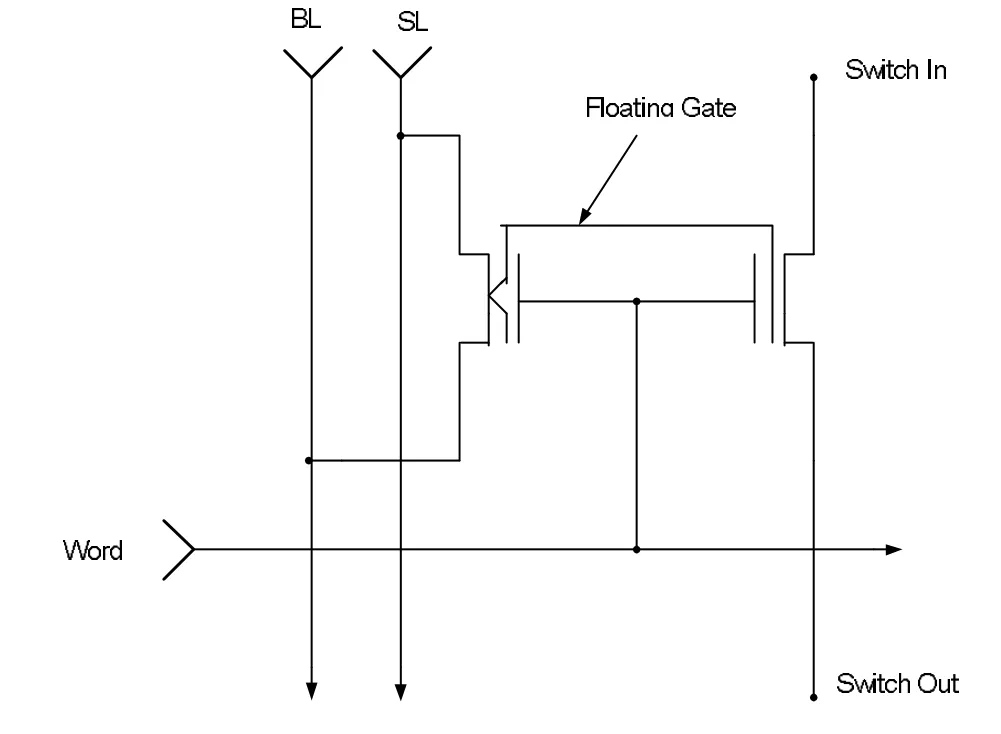

其中,Flash开关编程点单元仅由两个晶体管组成,它们的作用是:一个用于对此开关进行擦除、编程、校验等操作;另一个用于开关的选通[1]。这种开关单元具有占用硅片面积小、阻抗和容性负载低、非易失性等特点,其结构如图2所示。对Flash架构的FPGA进行编程就是对这些开关进行控制、实现连线的过程。

图2 Flash开关编程点单元

FPGA芯片内部的任何逻辑模块之间都是通过可编程布线资源连通的。而基于Flash架构的FPGA的可编程布线资源主要包含水平布线资源、垂直布线资源和在水平与垂直布线资源之间的Flash开关编程单元组成。

当对Flash开关编程单元按照三端器件加入编程电压后,编程单元中的浮栅型开关管导通[2],于是将水平布线资源和垂直布线资源进行永久的连接。

Flash的逻辑单元(Logic Tile)系列互连结构是一种通道型的门阵列结构,如图所示,它的水平布线资源为32根长线,垂直布线资源有10根长线,这些长线被Flash开关编程单元分成若干小段,可以按需要连接成长短不等的线,同时分别与逻辑功能块的输入和输出相连[3]。

在电路中,逻辑单元按照图组成阵列,它组成了最小的一块Flash逻辑单元阵列,我们将这个小阵列称作M阵列。M阵列将Flash开关编程单元以32行×10列排布,水平方向上每一行的水平布线与Flash浮栅型开关管连接,垂直方向上每一列的垂直布线与Flash存储单元连接。

根据整体电路的结构和存储单元的排列分布,可以设计出编程通路的系统结构,实现对所有Flash存储单元的编程操作。

2.2 编程通路系统结构设计

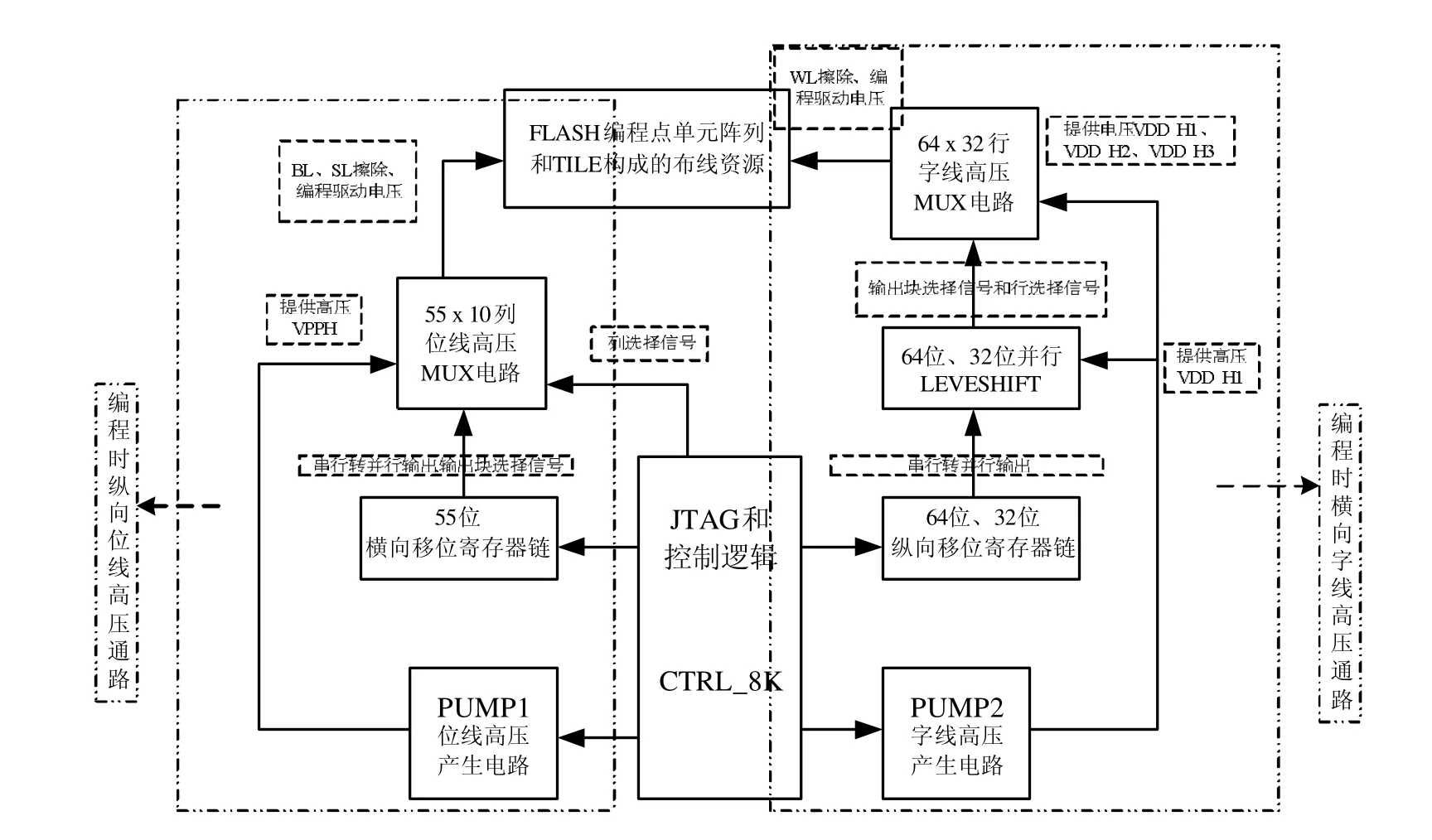

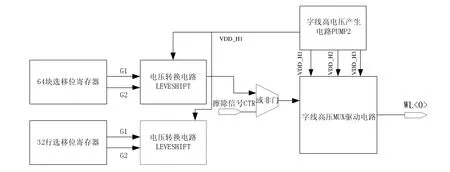

基于Flash架构的FPGA编程通路的系统结构由JTAG和逻辑控制电路、可编程布线资源和寻址编程电路组成。寻址编程电路主要包括横向字线高压通路和纵向位线高压通路,其中横向字线高压通路包括字线高压产生电路模块PUMP2,64位、32位串行转并行移位寄存器链模块,64位、32位并行LEVELSHIFT模块,字线高压MUX电路模块;纵向位线高压通路包括位线高压产生电路模块PUMP1模块,55位串行转并行移位寄存器链模块,位线高压MUX电路模块。编程通路的系统图如图3所示。

FLASH_FPGA器件在进行编程操作时,将按照编程通路的系统图,对整个芯片中的单元进行1bit位逐次编程操作。经过寻址编程电路的译码操作后,它将被选中的行列交叉的Flash编程点单元的WL字线电平置为低压信号VDD_H3=0V,而位线BL电平置为高压信号VPPH=14.5V,从而完成编程操作。

3 编程通路电路模块设计

根据组成编程通路中的每一个模块的功能特点,具体分析和设计模块的电路结构,并且对部分模块的功能进分析描述。具体模块电路设计详述如下。

3.1 JTAG和控制逻辑电路

JTAG是一种国际标准测试协议[4],具体指的是边界扫描测试结构,主要用于集成电路的系统测试。如今,JTAG已经嵌入在一些FPGA、DSP、ASIC芯片中,作为一种高优先级的配置方案而被设计者们广泛应用。

在本设计的编程通路系统中,JTAG作为电路测试和编程下载的控制部分而被选用。如图4所示即为所采用的JTAG电路结构框图结构,可见其主要由四部分组成:TAP端口、TAP控制器、指令寄存器和数据寄存器(包括边界扫描寄存器、旁路寄存器等)。它一般有四个端口,分别为:TMS状态选择信号,TCK时钟信号,TDI串行数据输入信号,TDO串行输出信号。有的JTAG电路还包括TRST复位信号。

图3 编程通路的系统图

图4 JTAG电路结构框图

3.2 寻址编程电路

基于Flash结构的FPGA可以分为三种工作模式,包括:正常逻辑工作模式、编程模式、校验模式。在编程模式的条件下,全局时钟TCK和串行数据TDI配置为输入,在TCK时钟脉冲下,从TDI端口输入串行码,完成编程操作流程[1]。

寻址编程电路模块如图5所示,由三部分组成:串行移位寄存器链、并行锁存器、电平转换电路(LEVELSHIFT)。在编程和校验过程中,该模块被用来将TDI输入的一帧数据串行输入并行输出给内部电路,如果需要采用高压输出,则需要经过电平转换电路(LEVELSHIFT)后输出。

图5 串行转并行移位寄存器模块

在进行编程操作时,通过TDI端口将一帧数据串行输入移位寄存器链之中,然后再并行发送到内部MUX电路、驱动电路的输入。在整个FLSAH_FPGA的整体架构中,寻址编程电路模块包括横向和纵向两部分,总共包含一条64位移位寄存器链、一条32位移位寄存器链、一条12位移位寄存器链、两条55位移位寄存器链,分别用来选中一行和一列的Flash编程点单元,最后选中行和列的交叉点单元。寻址编程电路模块以一条32位移位寄存器链结构为例,如图3所示,它属于串行转并行移位寄存器链结构,还包括32位并行锁存器和32位电平转换电路[5]。

本设计中的整体架构根据位流配置文件,通过横向和纵向寻址编程电路模块的操作。首先64位移位寄存器链用来将整体内核的Flsah单元阵列划分为64个横向大块,通过寄存器链中存储的数据“1”,来选中其中的一个块;然后,12位或32位移位寄存器链用来将这一个块划分为12或32行Flsah编程点单元,并且通过寄存器链中存储的数据“1”依次选中其中的一行;接着,其中一条55位移位寄存器链用来将整体内核的Flsah单元阵列划分为55个纵向大块,通过寄存器链中存储的数据“1”,来选中其中的一个大块[6];最后,由逻辑控制电路CTRL_8K中的内部复用寄存器链产生的控制信号ADD0~ADD9选择几列Flsah编程点单元,完成了Flsah编程点单元最终的水平通路和垂直通路的寻址操作。

3.3 位线编程高压通路模块

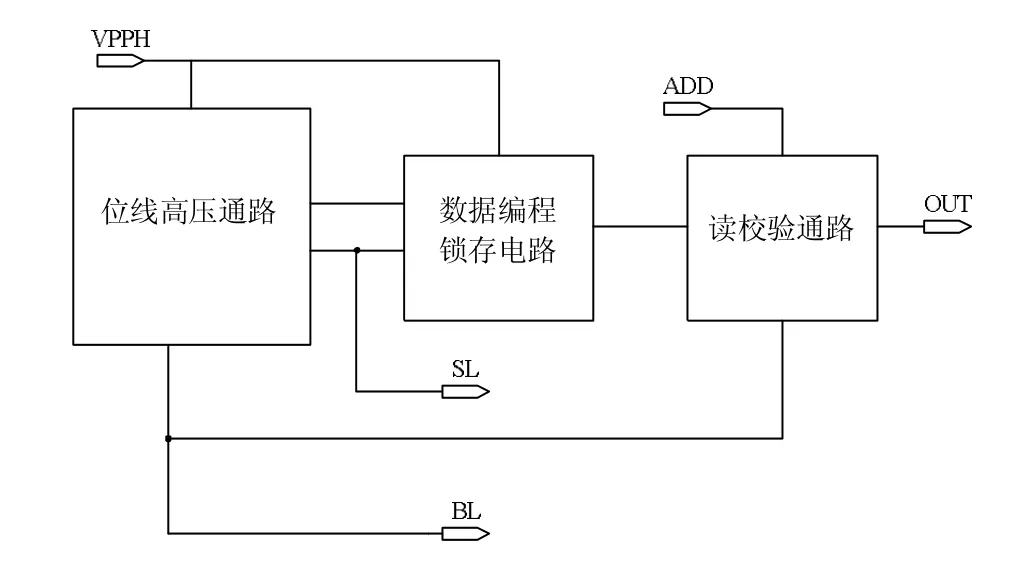

如图6所示,为位线编程高压电路。它的作用是用来给存储单元位线BL和源端信号SL提供传输电平信号,主要由位线高压通路、数据编程锁存电路、读校验通路三部分组成。该模块的输入控制信号主要来自于控制逻辑CTRL_8K的输出。其中,VPPH为编程高压产生电路提供的14.5V的高压信号,ADD为列开关选通信号。

图6 位线MUX电路框图

此外,这部分电路具有块选开关和列选开关的功能,通过连接55位移位寄存器链的输出,将整个Flash编程点单元阵列划分为纵向55个大块;再通过ADD列开关选通,将整体划分为55×10列单元。

3.4 字线编程高压通路模块

本设计中的Flash编程点单元在进行擦除操作时,将对整个芯片中的单元进行全片擦除操作。通过一个全片操作控制信号CTR,将所有Flash存储单元的WL字线电平强置为高压信号VDD_H1=14.5V,而位线BL和源端SL置为0,在此条件下完成全片擦除操作,使得所有编程点开关处于关断状态。

横向寻址编程电路模块包括64位、32位移位寄存器链的串并转换和高压电平转换电路,在编程操时,此模块通过这两部分转换电路的作用,来分别完成一行的编程点单元选择和驱动字线的操作。

全片编程点单元阵列在横向寻址编程电路的块选择和行选择的操作下,被划分为64块、每块32行单元的阵列,其中每一行阵列都需要一条字线WL高压通路来驱动,其逻辑框图如图7所示。

图7 编程字线通路逻辑框图

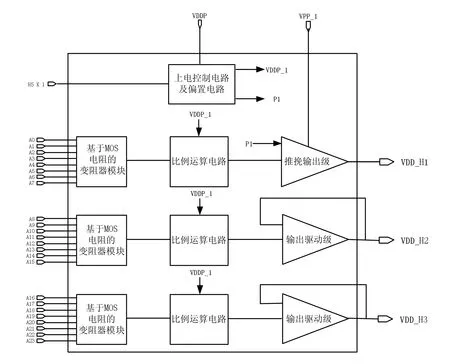

3.5 编程高压产生电路模块

由于Flash编程点单元在擦除和编程操作时,字线和位线都需要选择13V以上的高压操作,因此需要编程高压产生电路来产生稳定的编程高压来最终完成编程点单元的编程。

编程高压产生电路单元模块由比例运算电路、偏置电路、译码电路、稳压电路组成,同时在输入结构上采用了NMOS管并联结构作为电阻阵列,通过以选通的方式控制并联NMOS管个数的多少,来选择不同的阻值;再通过电流串联负反馈结构产生一个恒定电流,根据并联NMOS管的个数,为下一级比例电路提供不同的电流大小。利用放大器电路的同向比例运算网络实现不同电压的相加转换,进而得到编程时所需要的高电压[7]。它作为有着强驱动能力的输出电平,为下一级选择电路提供可选择的电平值。为了重复利用高压产生电路模块,字线、位线编程高压产生电路采用了相同的电路结构,其电路功能框图如图8所示。

图8 编程高压产生电路

对编程高压产生电路进行仿真验证,采用输入译码A0~A23的阶梯变化而使得基于NMOS电阻的变阻器模块阻值变化,得到输出电压在阶梯式变化下的仿真波形。仿真结果如图9所示。在输入译码值为1111 1111 1111 1111时,输出最高编程电压值可以达到VDD_H1=14.5V,低压值为VDD_H2=1.75V,VDD_H3=0V。

图9 编程电压仿真波形图

4 系统编程控制仿真

以JTAG和逻辑控制模块将编程通路系统中的各个模块连接起来,通过一定的指令码来控制系统的编程时序和逻辑功能,从而实现对存储单元的编程操作[8]。

编程操作时,根据编程操作的系统图,对整体逻辑控制信号进行NC-Verilog仿真,如图10所示,相应仿真结果已由圆圈和方框圈出。将位流数据作为仿真输入信号,寻址编程操作时,状态机输出信号TAP_Q[0:3]的值为“2”的时刻内,8位指令寄存器的数值为“83”时刻,作为横向块选择的64位串行转并行移位寄存器链开始工作,此时信号X217_AR38跳变为低电平;当指令寄存器的数值为“82”时刻,作为横向行选择的32位串行转并行移位寄存器链开始工作,此时信号X217_AR44跳变为低电平;当指令寄存器的数值为“85”时刻,作为纵向块选择的55位串行转并行移位寄存器链开始工作,此时信号X217_AU41跳变为低电平;最后,当指令寄存器的数值为“84”时刻,选择开启列选择开关。从仿真波形可以看出,在799600ns~811600ns的时间内,各个移位寄存器链顺次工作,完成了一次编程操作流程。而整个系统的编程操作是一次编程操作的循环反复执行,直到将阵列中的所有编程点单元寻址完毕为止。

图10 NC-Verilog仿真结果

5 结束语

基于Flash架构的FPGA极具应用价值,全面掌握其编程原理有利于该项技术的潜在力量的最大发挥。本设计中仅以某一款具体产品为例展开深入讨论与设计,并辅以仿真研究,所获得的数据与结论具有一定的代表意义,可在一定程度上扩展到对同类产品的剖析与构建,对采用Flash技术实现编程的其他产品也具有指导性与启示性。