概述CMOS集成电路应用面临的问题

2018-09-10杨涛

杨涛

摘 要:目前,CMOS集成电路的应用已经渗透到人们生活的方方面面,小到手机、计算机,大到汽车、航天飞机等都有对它的应用。它不仅使工业技术发展地更快更好,也让人们的生活起居、衣食住行变得更方便更快捷。但是随着科技的日益成熟,人们对产品质量的要求不断提高,CMOS集成电路的发展也将面临一些问题,比如功耗、延迟、晶体管的数目等方面。本文主要就这几类问题进行探讨。

关键词:CMOS集成电路;晶体管数目;延迟;功耗

中图分类号:TN432 文献标识码:A 文章编号:2096-4706(2018)02-0060-02

An Overview of the Problems Faced by the Application of CMOS Integrated Circuits

YANG Tao

(Anhui University of Science and Technology,Huainan 232001,China)

Abstract:Currently,the application of CMOS integrated circuits has infiltrated all aspects of people's lives,ranging from mobile phones,computers,large cars,space shuttles and so on. Make the development of industrial technology faster and better,make people's daily life,clothing,food,shelter more convenient and faster. However,with the development of science and technology,the demand for product quality is constantly increasing. The development of CMOS integrated circuits will face some difficulties,such as power consumption,delay,and the number of transistors. This article mainly on these types of issues.

Keywords:CMOS integrated circuits;number of transistors;delay;power consumption

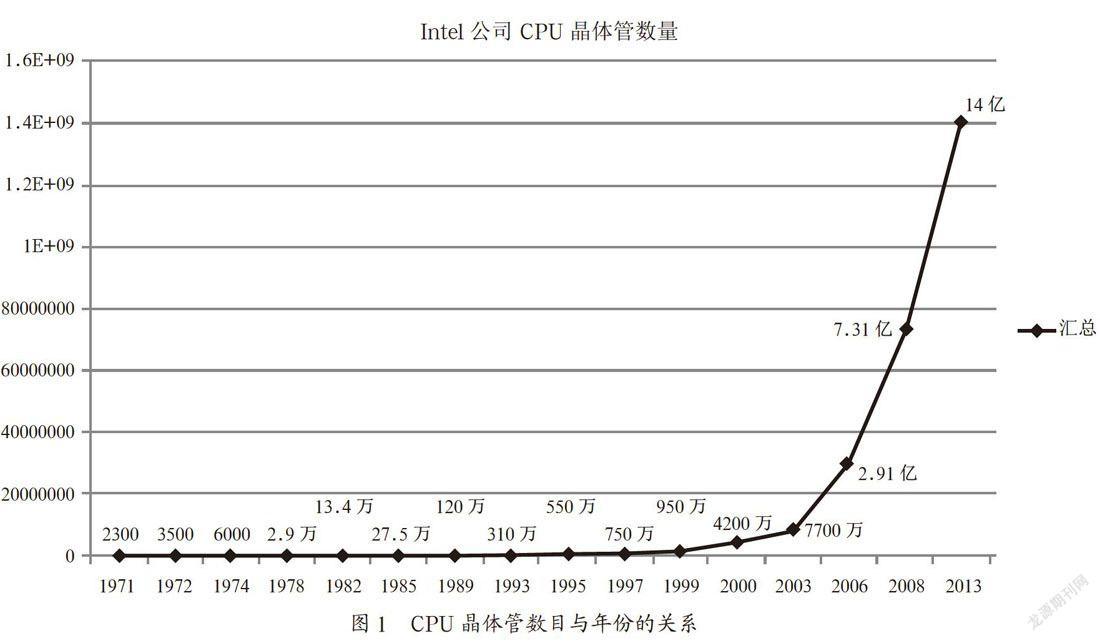

1 晶体管的数目

1958年,世界上第一个晶体管在美国诞生,并且只有2个晶体管。然而2008年,一个存储器中包含的晶体管就达到了惊人的40亿个之多,其指数倍的增长速度引起了人们的重视。有数据显示,单芯片上的晶体管数目每18个月就会翻一番,这就是著名的摩尔定律。Inter微处理器中晶体管数目与年份的关系如图1所示。在图中可以清楚的看出,从1971年到2011年,微处理器的晶体管数目呈直线上升,而且丝毫没有下降的迹象,2005年达到将近20亿个。专家们预测在未来10年还可以持续按比例缩小晶体管的尺寸,但是10年之后这个方法就没有效果了。

晶体管数目越多,随之产生的功耗就会越大,延迟也会增大,这会给工业生产和制造带来很大的影响,比如成本会相应地提高。虽然可以按比例缩小晶体管尺寸,从而减小延迟与功耗,但是当晶体管数目增加到无法缩小的时候,就会造成功耗过大、运行速度减缓的问题。

因此,我们可以提出一些猜想。

(1)从晶体管的制造材料入手。晶体管由半导体硅材料制作而成,而大自然中存在着丰富的元素,等待着人们去发掘和应用。如果我们发现了比硅更适合做半导体的元素,那么问题也许会得到解决。或者随着科技的发展,通过人工合成某种材料来制作晶体管,如此一来,晶体管数目的问题也可能被解决。

(2)改变晶体管中掺杂的杂质。我们都知道硅是一种不良导体,向里面注入掺杂剂才能起到导电的功能,如砷、硼等。那么,我们可以改变传统的掺杂剂,也许能起到意想不到的效果。

2 功耗

对于功耗,是CMOS集成电路的发展一直需要解决的一个问题。现在各种移动设备已经应用到人们的生活中,比如移动电话、手提电脑、电话手表等,这些电子产品早已与人们密不可分,它们使人们的生活更便捷,更加丰富多彩。但是随着用户数量越来越多,对能源的消耗已不容忽视。有这样一组数据:美国的数据中心和服务部门一年消耗了610亿度电,相当于15个发电厂的能量输出、45亿美元的消费。现在,全球都在推行低碳环保、绿色生活的理念,所以设计一个低功耗的CMOS集成电路成为当务之急。

CMOS集成电路的功耗分为静态功耗和动态功耗。理论上,CMOS集成电路在电路稳定状态下不存在从电源直接到地的路径,因此不会有静态功耗生成,但是在电路实际运行中,CMOS管会出现两种漏电流分量,包括反向漏电流和亚阈值电流,这两种电流会产生静态功耗。动态功耗是CMOS集成电路中最主要的功耗,在电路功耗中占据着主导地位,由动态功耗公式P=CV^2f可知,电源电压、电路中的连线电容、晶体管电容和晶体管的反转频率都会对动态功耗产生影响。因此,我们可以采取这样的措施:

(1)降低电源电压:动态功耗与电压的平方成正比,所以电源电压的影响还是比较大的,降低电源电压可以显著地降低电路的动态功耗;

(2)降低電容:由公式可知,功耗与电容成比例,所以降低电容也可以降低功耗。电容存在于连线和晶体管中,设计电路时,可以通过合理的硬件布局来降低电容,比如合理地选择器件的大小来减少器件之间的连线。

(3)降低活动因子:这是一个非常有效的方法,即当电路不在运行时,彻底的关掉电路,此时电路的活动因子就会将为零,功耗也就为零。

除此之外,我们可以对未来的发展提出猜想:如今由于光伏发电越来越受到重视,科学家们也比较看好光伏发电的前景,所以随着光伏发电技术的日益成熟,在未来我们可以利用光伏发电的原理对CMOS集成电路进行光伏供电,这样不仅绿色环保无污染,而且光是可再生资源,可以对生活和工业生产进行充分地供电。

3 延迟

在CMOS集成电路运行时,延迟是影响电路运行速度的重要参数。一个晶体管的延迟可以小到忽略不计,但当几十亿个晶体管一起运行时,产生的延迟对电路性能的影响将是非常大的。延迟过大会使工业生产和制造的效率下降,对工业产品的質量也有很大的影响。电路的延迟是由很多因素造成的,比如说器件本身、连线造成的传输延迟、信号的输入延迟以及信号输出的延迟等。一般情况下会利用一些模型对系统的延迟进行分析,常见的有RC延迟模型、ELMORE延迟模型、线性延迟模型等。

在进行电路设计时,为了减小系统的延迟,可以采取以下措施:

(1)合理布局器件版图。对于器件本身来说是存在寄生延迟的,即当门驱动零负载时的延迟。在确定器件后版图的平面规划就显得非常重要,因为尽可能地减少器件和连线能缩小器件和导线的生延迟,而且良好的单元版图也能减少器件的寄生电容。

(2)选择最优的逻辑级数。合理的逻辑级数可以使延迟最小化。假设一条具有N级的路径、路径努力为F、路径的寄生为P时,则它可能的最小延迟为:D=NF^1/N+P。这是确定最优级数的一个非常重要的办法。这样我们就不必根据晶体管的尺寸来估算电路的延迟。

4 结 论

尽管除了上述的几大类问题,CMOS集成电路的发展与应用会遇到各种的问题,但是在如今科技高度发达的时代,CMOS集成电路的设计会得到最大程度的优化,其应用也会越来越广泛。我相信,随着科技的进步,一切皆有可能。

参考文献:

[1] 韦斯特(著).周润德(译).CMOS超大规模集成电路设计(第四版) [M].北京:电子工业出版社,2012.

[2] 艾尔斯(著),杨兵(译).数字集成电路分析与设计(第二版) [M].北京:国防工业出版社,2013.

[3] 王昱阳,尹说(译).CMOS超大规模集成电路设计 [M].北京:机械工业出版社,2016.