基于集成芯片的软件无线电射频前端设计与实现*

2018-09-03曾荣鑫翟旭平

曾荣鑫,翟旭平

(1.上海大学特种光纤与先进通信国际合作联合实验室,上海 200444;2.上海大学上海先进通信与数据科学研究院,上海 200444)

1 引言

软件无线电是一种以开放式体系架构为基础,在通用硬件平台上应用软件技术实现具有最大灵活性和适应性的各种无线通信方式和功能的系统,其基本设计思想是以一个模块化、标准化的硬件平台为基础,通过编写不同的程序从而实现不同功能[1-2]。因此在实际的硬件平台设计中,为了在已定的硬件结构中最大化地发挥软件可重构的优势,应将射频模拟信号与数字离散信号尽早地转换,并让数字部分所占比例尽量高,这就要求宽带AD/DA转换模块尽量靠近天线部分,减少模拟部分,最好是能将从天线进来的射频信号不经过任何混频,只需放大后直接进入AD进行采样。然而工作频段大于2 GHz时,根据Nyqiust采样定理,采样率不能低于信号带宽的2倍,也就是需要采样率高达4 GHz,这样的AD/DA是很难实现的,即使能实现成本也很高。对此,本文采用高度集成芯片LMS6002D作为模拟射频前端的收发芯片,其内部采用宽带中频带通采样结构[3-6],可有效解决AD直接采样带宽不够的问题,且只需要较少的外部器件就能实现射频信号到中频数字信号的转换,提高了系统的集成度。

图1 硬件模块分布图

LMS6002D作为模拟射频前端的收发芯片,其内部集成了低噪声放大器(L N A)、数字频率合成器(PLL)、功率放大器(PA)、低通滤波器(L P F)、混频器(M I X E R)、收发功率控制器(VGA)和12位的ADC/DAC模块,使得软件无线电平台的集成度大大提高,极大地简化了系统的硬件设计。该器件可通过SPI(Serial Peripheral Interface,串行外设接口)进行编程,并提供一个完整的校准功能。对于片内AD/DA采样模块无法满足通信要求时,在发送链路,可以采取片外将数字基带信号转换为模拟信号后再输入到LMS6002D的模拟输入端,而接收链路则可以在滤波放大后从模拟输出端输出模拟中频基带信号。

2 射频前端整体硬件设计

2.1 射频前端实现方案

在软件无线电平台的设计中,射频前端作为硬件设计中模拟信号与数字信号之间的转换,其性能的优异直接决定着系统的整体性能,因此其设计是关键。

本文射频前端的实现以射频芯片LMS6002D为核心,辅以其它必要的外部电路作为收发链路的主要实现方案,主要由电源供应电路、时钟电路、射频电路和高速数字接口模块组成,整体硬件模块分布如图1所示。

2.2 硬件电路设计

射频前端的硬件设计主要包括了电源电路、时钟电路、射频模块电路、数字端电路。

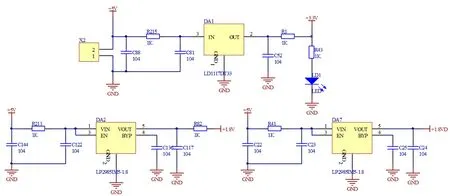

图2 电源电路图

(1)电源模块。在任何硬件系统设计中,电源模块的设计都是最基本和至关重要的。在此次设计中,射频前端所有模块的电源供应都是由外部输入5V直流经过DC-DC变换得到。根据系统所有器件的供电分析:LMS6002D芯片内部的VGA、PLL、LNA等模块都需要+3.3 V的模拟工作电压,以驱动I/O端口的高低电平输出和模块电源供应;内部ADC和DAC模块是模拟电路和数字电路的桥接,需要提供模拟+1.8 V、模拟+3.3 V和数字+1.8 V参考电压;后级的功率放大电路和低噪声放大电路采用+5 V供电,以提供足够大的功率输出。电源电路如图2所示。

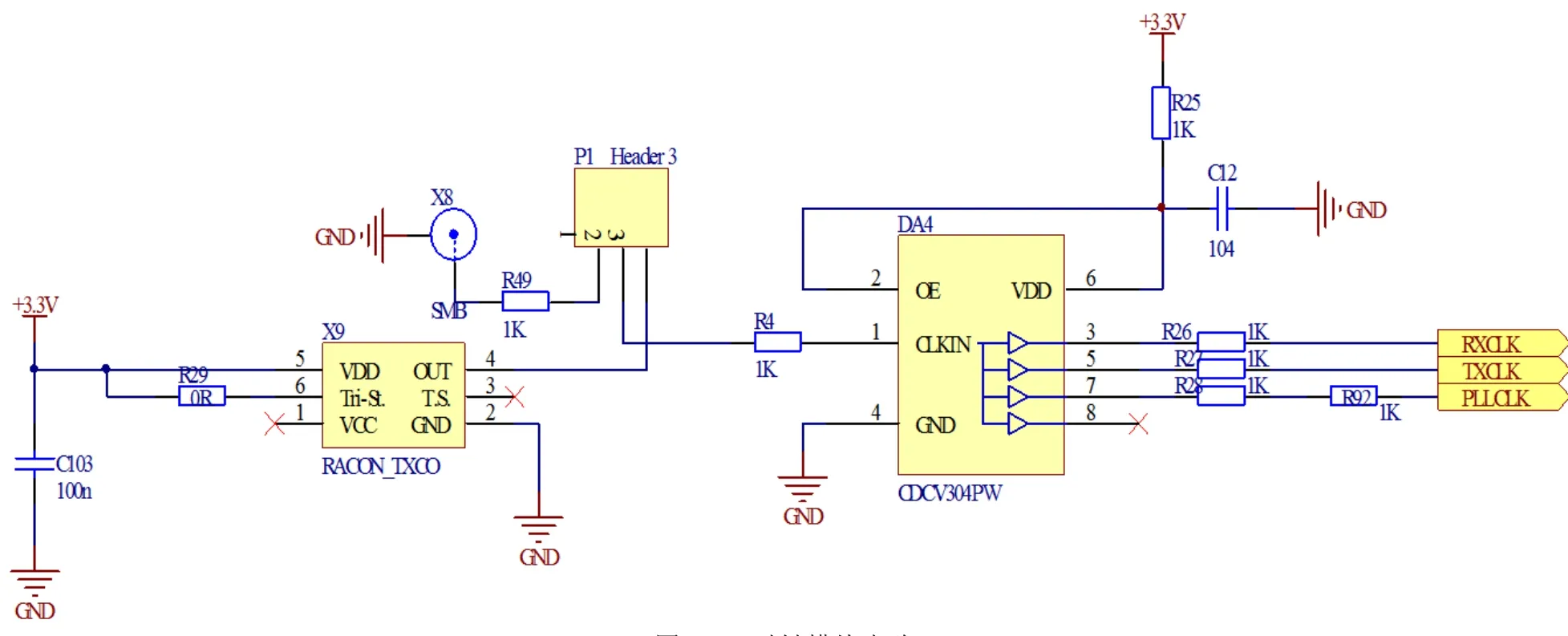

(2)时钟电路。在本文设计的射频前端硬件中,LMS6002D器件需要从外部提供的时钟信号有3个:PLL模块参考时钟输入PLL_CLK、接收链路接口数据时钟RX_CLK、发送链路接口数据时钟TX_CLK。此处将采用具有温度补偿特性的有源晶振作为PLL_CLK时钟,当然对于不同需求时也可以通过SMA接头外部输入,具有较大的灵活性。考虑到TX_CLK和RX_CLK时钟频率是ADC/DAC采样率的2倍以上,而不同应用场景下基带IQ数据流的采样率是不一样的,例如WCDMA制式下的下行ADC采样率为15.36 Msps,而GSM制式下的下行ADC采样率为1.083 Msps,因此TX_CLK和RX_CLK时钟采取从外部数字基带接口输入,也可以直接使用PLL_CLK的缓冲时钟。整个时钟模块的硬件实现如图3所示。

(3)射频模块电路。LMS6002D器件的发射链路有两个输出端口TXOUT1和TXOUT2,接收链路有三个输入端口RXIN1、RXIN2和RXIN3,且每一个端口为了有效抑制输入输出共模噪声,均采取了差分传输模式,即TXOUT1实际输出端口为TXOUT1N和TXOUT1P。因此射频模块主要是将差分信号经过单双端转换电路转换为单端信号[7-9],再把多路单端射频信号输入射频开关电路。对于每条输入输出口的平衡——非平衡信号转换,低频段与中频段部分采用的分立元件电容电感组成的π型结构,宽带部分则采用了巴伦TC1-1-13MA器件,这种转换电路可提高信号传输时的抗电磁干扰、抗电源噪声能力和抑制偶次谐波,另外还可以起到前后电路阻抗匹配的作用。在接收回路中,对于不同频段的输入端口RXIN1、RXIN2和RXIN3,需要两位GPIO口控制;发送回路有TXOUT1和TXOUT2,只需一位GPIO口控制。射频模块电路如图4所示,射频开关GPIO的真值表如表1所示:

表1 射频开关GPIO真值表

图3 时钟模块电路

(4)数字端电路。此处主要包括了发送TX_DATA和接收RX_DATA通路的数字中频信号(其位宽都是12 bits),串口SPI通信接口SCLK、SEN、SDIO、SDO以及其他的一些使能端口所组成的数字接口,方便与数字处理系统进行数据地交互。

2.3 硬件PCB版图设计

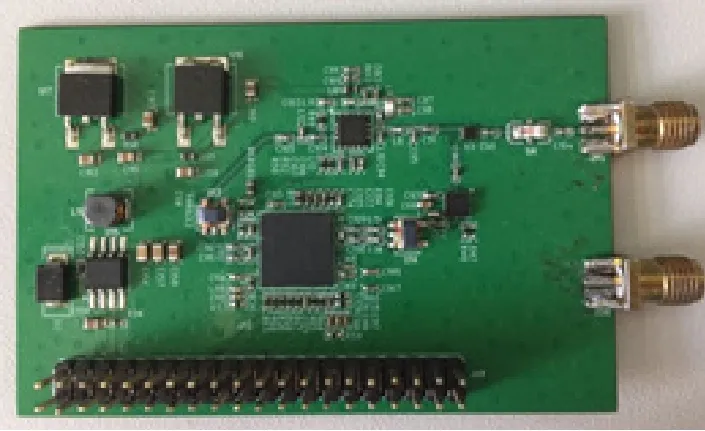

在前文2.2节所设计的原理图基础上,使用硬件设计工具进行PCB版图设计,最终实现本文所设计的射频前端硬件电路板,以便后续的板级测试。由于此射频前端最高需要支持3.8 GHz的射频信号,因此在PCB的布局布线时不仅需要考虑到电源完整性、信号完整性设计,还要对寄生效应、耦合作用等因素加以控制。例如在双端差分信号线布线时,由于是差分对,元件布局需要呈对称性,走线长度要一致且尽量短,以减少高频信号对外的发射和相互间的耦合作用。数字信号的地线和模拟信号的地线是要做隔离的,可以采用在合适位置单点互联的方式,或者采用高频扼流磁珠互联的方式。高频信号线路中尽量减少过孔的使用,可有效减少引入的分布电容。考虑到以上各种因素后,并参考相关高频电路的设计,最终的实物如图5所示:

图4 射频模块电路图

图5 最终实物图

3 射频前端参数配置

3.1 配置方式

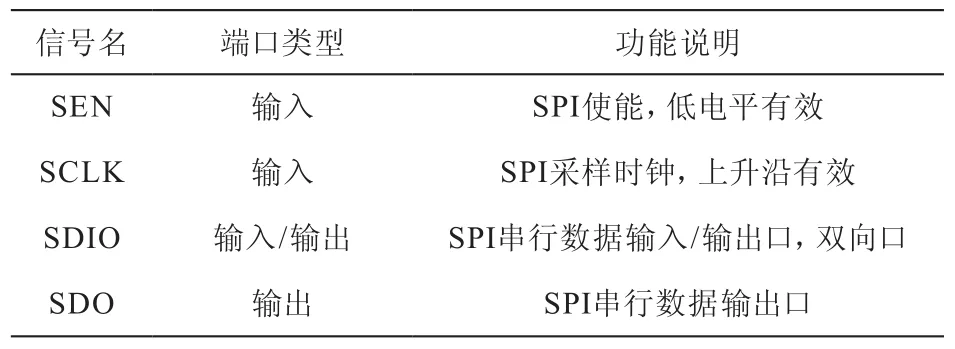

LMS6002D不同模块的参数设置是通过同步串行SPI通信修改模块寄存器的值实现的。SPI通信可以配置成3线或4线操作模式,其信号名、端口类型和功能说明如表2所示:

表2 SPI信号及功能说明

每个配置寄存器位宽为8位,一个读写时序包含16 bits,前8 bits为指令字节,后8 bits为待读写的数据比特。其中指令字节的最高位是SPI读写指示位,1代表写,0代表读,其余7 bits表示寄存器地址,因此每次的读或写操作都需要16个SCLK时钟周期。对于SPI通信时的定时定性如下:数据最小建立时间tES=1 ns,数据最小保持时间tEH=0.2 ns,使能最小建立时间tES=2 ns,使能最小保持时间tEH=0.2 ns。

3.2 参数配置程序

根据设计的需求,可通过建立S P I通信对LMS6002D内部寄存器进行读写访问,从而实现所需功能。根据模块的不同功能将寄存器划分为8个不同的逻辑块——3 bits表示,每个逻辑单元含有16个寄存器——4 bits表示,共同组成7 bits的配置寄存器地址。

参数配置程序是在FPGA上使用Verilog HDL语言编写一个SPI串口通信程序[10],该程序主模块采用了主从状态机结构,主状态机是从顶层模块的初始化一直往下去配置PLL、VGA增益、LPF失调补偿等子模块,子状态机则是每个不同模块内部的具体配置过程,只有当子状态机配置完成后才会跳到主状态机进行下一个模块配置,具体实现流程图如图6所示。

图6 参数配置程序流程图

4 仿真与实测

根据3.2节的内容,本文在FPGA上编写参数配置程序,然后通过SPI串口通信将参数值传入射频前端,寄存器的配置值可参考芯片手册。图7是SPI参数配置程序在ISim平台上的时序仿真,可以看到SPI的MOSI端口可以连续将不同的配置参数转换为串口输出,且时序基本满足通信要求。

配置程序仿真通过后,将程序下载到FPGA中,再搭建好射频前端的硬件测试平台,测试在不同中心频率时能否输出射频调制信号。以下为测试环境:

(1)DC直流电源:为射频板和FPGA供电;

(2)Agilent 80 MHz信号源:为射频板提供30.72 MHz外部参考时钟输入;

(3)Agilent任意波形发生器:提供单一频点的模拟正弦测试信号;

(4)R&S基带信号发生器:产生模拟中频IQ调制测试信号;

(5)Agilent示波器:射频输出信号测试;

(6)R&S频谱分析仪:射频信号的频谱分析。

图7 参数配置仿真图

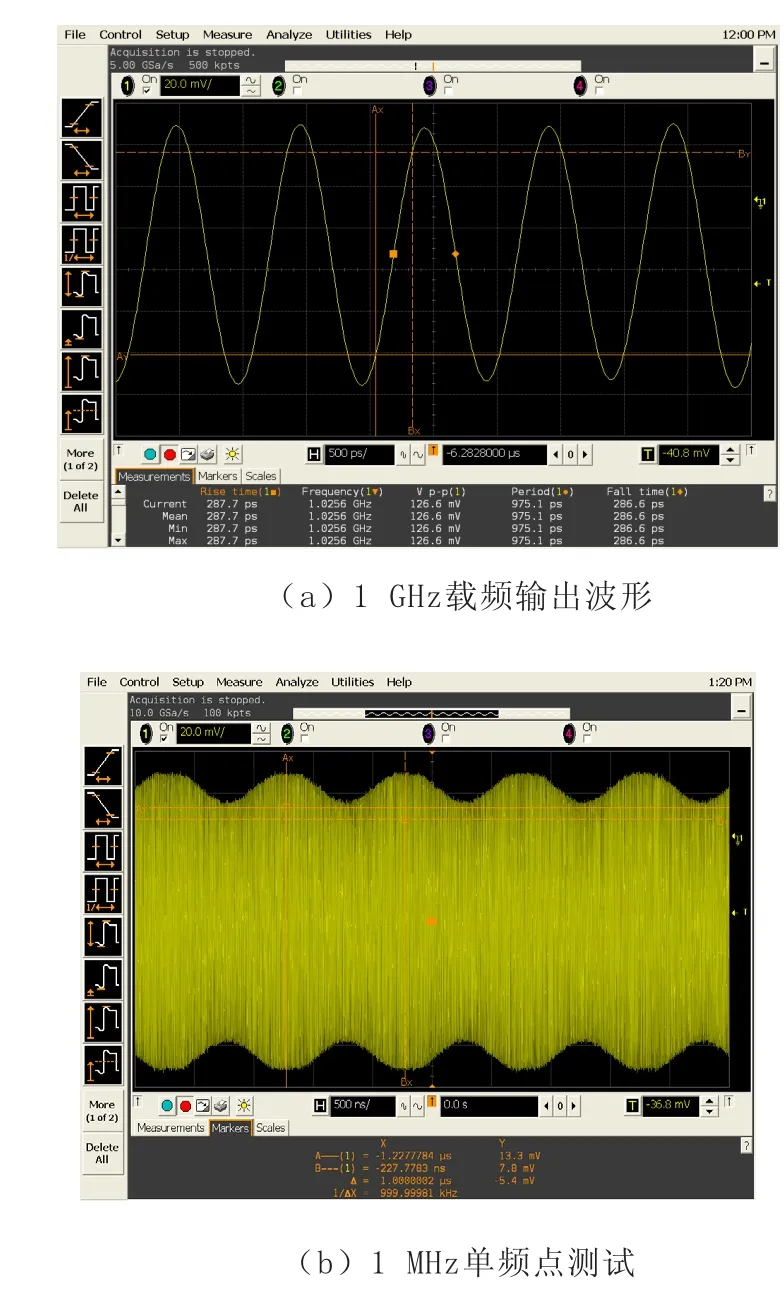

首先测试系统PLL模块能否正常输出不同频段本振信号。如图8为本振信号输出波形,从图中可以看到,本振频率为1 GHz,和程序参数配置值一致,说明PLL模块可以正常工作。将TX链路的低通滤波器带宽配置为最大带宽14 MHz,从TXINI和TXINQ端口输入不同单频点1 kHz、10 kHz、100 kHz、1 MHz、10 MHz和14 MHz信号,以测试射频前端的基带传输带宽是否能达到集成芯片的最大可传输带宽。

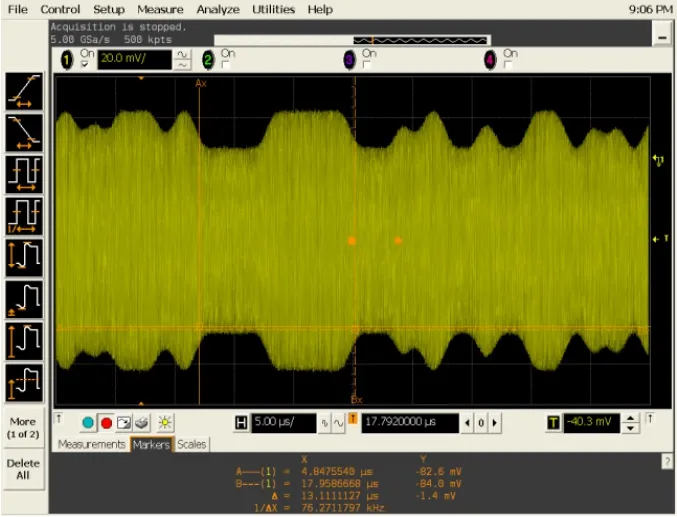

图8中输出信号的包络周期为1 MHz,与输入信号频率一致,说明发射链路的各个模块工作正常,经过测试其它频点也能调制输出。再测试输入模拟基带IQ调制信号,使用基带信号发生器产生1 Msps BPSK数据格式的IQ调制信号,图9为IQ路调制信号波形图,图10为模拟上变频后的射频输出波形。

图8 本振信号输出波形

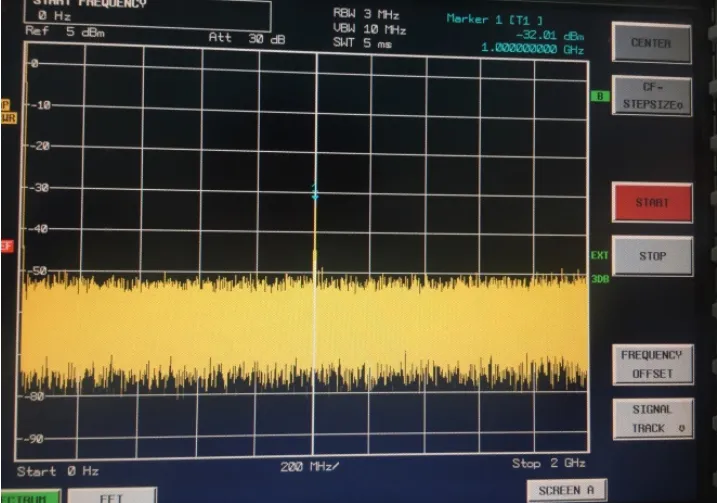

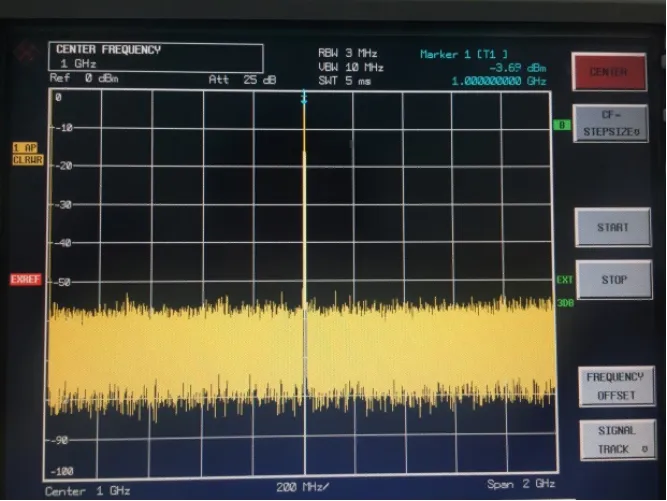

理论上,I路和Q路输入信号相加组成的波形应该和射频输出信号的包络一致。在图9和图10中,横坐标每个格子的时间尺度都是5 μs,经过比对,模拟上变频后的射频输出信号的下边包络与IQ合成波形是基本相同的,说明IQ输入信号成功调制到了1 GHz载波上。为了测试发射链路的输出功率范围,需要调整发射链路的增益。图11、图12为输出射频信号的频谱分析图:

图9 IQ路输入信号

图10 射频输出波形

图11 增益最小时的输出信号频谱图

从图11和图12中可以看出,发射功率主要集中在1 GHz,该射频前端的发射功率范围为-32 dBm~-3 dBm。

图12 增益最大时的输出信号频谱图

5 结束语

本文基于集成芯片LMS6002D的软件无线电射频前端,根据前文所提出的设计需求,设计出了一个射频前端硬件平台,可将数字基带信号经过DA后模拟上变频为射频信号,也能将射频信号模拟下变频至中频信号,再经过内部集成的AD模块采样为数字中频基带信号,便于后期的数字系统处理。经过测试,该射频前端支持0.3 GHz~3.8 GHz频段载波,最大支持28 MHz信道带宽,输出功率最大可达-3 dBm,基本满足前文所提出的设计需求,整个硬件平台集成度高,可根据需求灵活配置参数,符合现代软件无线电系统平台的小型化、集成化的设计理念。