基于SCA的硬件抽象层设计

2018-09-01石磊

石磊

(中国电子科技集团公司第二十研究所,西安 710068)

0 引言

软件无线电(Software Defined Radio)是指用软件定义的、能实现多种功能的无线电通信系统。SCA(Software Communication Architecture)[1]架构是为了解决传统无线电波形可移植性差的问题而提出的一个顶层设计规范,其目标是最大化软件的可移植性和可配置性,提高无线电波形的可移植性、可复用和可互操作性等特性,使无线电波形系统升级方便简单,降低无线电波形开发和操作管理成本。

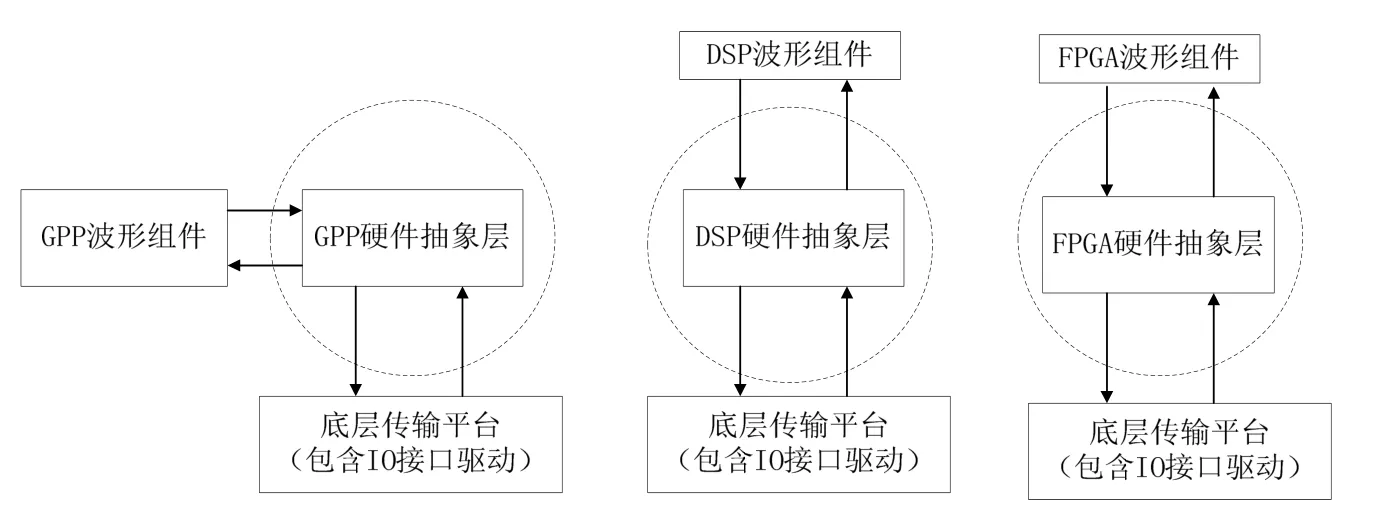

SCA规范要求各波形组件之间的通信由CORBA中间件[2]来完成。但是,目前仅通用处理器(例如 CPU)能够运行 CORBA,FPGA、DSP等异构处理器无法运行。FPGA、DSP等专用的处理器则通过硬件抽象层设计为FPGA波形组件设计标准化的接口,将波形组件与外部处理单元的通信功能和自身的信号处理功能相分离,极大地降低了波形组件与具体硬件平台的耦合度,从而使波形开发人员能够从繁琐的数据交换过程中解放出来,只需关注波形处理算法本身和软件平台架构的设计,因此能够在很大程度上降低新波形的开发周期和开发成本,增强波形的可重用性和可移植能力,与传统开发方法相比,具有明显的优势。

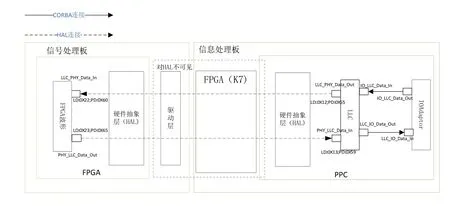

1 硬件平台架构

图1是本文使用的硬件平台架构图,其中主控板负责波形的加载管理,部署核心框架和部分设备服务;信息板主要负责处理收发的信息,该模块的两个GPP分别映射到后端的两个信号处理通道上,部署核心框架和部分设备服务;信号处理板是波形业务处理模块,需要部署硬件抽象层。GPP内部组件通过 CORBA中间件通信,GPP-FPGA以及FPGA-FPGA组件间通过硬件抽象层进行通信。参考最新 SCA4.0规范[3],通过设计软件平台各核心模块的结构和相互之间的互联接口,建立满足多种波形运行需求的通用软件平台,为硬件平台加载各种通信波形提供支撑环境。

图1 硬件平台架构图

图2 硬件抽象层与波形组件关联模型

图3 硬件抽象层设计

2 硬件抽象层设计

硬件抽象层设计是为了提高波形跨平台可移植性,屏蔽与硬件平台紧密相关的硬件驱动和底层通信机制,与波形组件使用标准的通信接口,实现波形组件间通信方式与具体硬件平台的分离,保持波形组件底层通信访问接口的一致性,硬件抽象层与波形组件之间的关联模型如图2所示。

硬件抽象层由通信函数和接口组件两部分组成。接口组件提供消息传输功能,负责将硬件抽象层消息通过外部传输链路向外部发送,或者从外部传输链路中接收硬件抽象层消息。GPP和DSP硬件抽象层接口组件为硬件驱动程序,FPGA硬件抽象层接口组件为硬件接口实体模块;通信函数提供硬件抽象层消息的路由功能,负责将接口组件接收到的硬件抽象层消息或解析后的数据转发到特定的信宿函数,或者将特定信源函数传递过来的硬件抽象层消息或数据通过接口组件向外发送。

本文中采用的硬件抽象层设计如图3所示。

在信息板GPP上增加一个HAL Device组件,在信号板 FPGA(KU085)上,同样需要增加一个HAL硬件抽象层。对于HAL组件来说,FPGA(K7)和FPGA(KU085驱动)对HAL是透明的, LLC通信链路与FPGA(KU085)的波形组件互相通信。信息板启动后,GPP硬件抽象层 HALDevice组件在其初始化阶段需要配置到FPGA硬件抽象层控制端口的路由。

2.1 硬件抽象层编码方法

当硬件平台和波形主要功能开发完成后,需针对设备组件、服务组件以及该波形所包含的所有组件的端口进行LD编号,编号的规则为:

(1)设备端口LD格式:<5位板卡编号>_<4位芯片编号>_<6位端口编号>,设备端口编号范围从0~31,芯片编号在板卡内部唯一,板卡编号在整个平台内唯一,板卡编号可为槽位号。其中,端口号为全0表示硬件抽象层设备控制端口。

(2)波形组件端口 LD格式:<5位波形编号>_<4位组件编号>_<6位端口编号>,端口编号在组件内部唯一,同时,波形组件的端口编号不能与设备和服务的端口编号冲突,由于设备和服务端口编号为0~31,所以波形组件端口编号范围是32~63。波形组件编号在一个波形内部唯一,波形编号由软件平台通过硬件抽象层配置报文进行配置。

2.2 设备LD编码

板卡地址根据槽位号确定,以保证各板卡地址不会相互冲突。板卡所在的槽位号可以静态配置也可以动态配置,如果采用动态配置方案,则需要驱动程序能够读取当前板卡的槽位号;如果板卡不需要换位置,则使用静态配置的方式。本平台板卡设备编号如表1所示。

表1 设备LD编号

芯片编号主要用于表示各个板卡上的处理器芯片,芯片编号如表2所示。

表2 芯片编号

2.3 硬件抽象层消息格式

硬件抽象层消息帧格式如图4所示。

图4 硬件抽象层消息帧格式

硬件抽象层消息帧各字段的含义见表3。

表3 硬件抽象层消息字段

LD字段用来表示消息应被送达的信宿函数的地址,每个信宿函数都有一个LD。LD是在CE域内定义的整型常量,指向一个具体的接口,如DSP函数、FPGA节点等。

IU字段用来标识波形组件是否已完成消息处理。波形组件在消息处理结束之前必须设置该字段,以声明消息还在处理。

Length字段表示硬件抽象层消息帧的长度。消息从LSB字节到MSB字节以地址递增的方式进行排列。引用该数据单元的指针指向LSB字节。

信源函数完成消息预处理,信宿函数根据接收到的消息指针访问数据。硬件抽象层通信的流量控制可根据需要,在数据发送端或数据接受端实现。硬件抽象层通信服务可根据需要,采用推模式或拉模式,即可以将数据写到目的地址,也可以从目的地址读取数据。

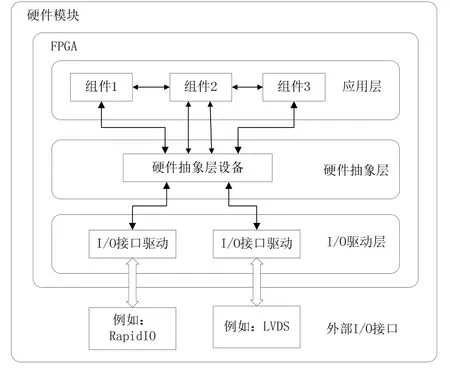

3 FPGA上HAL的实现

FPGA硬件抽象层为运行于FPGA中的波形应用提供标准、统一的接口,并为FPGA与其他处理器之间提供消息传输机制。硬件平台开发人员负责FPGA中硬件抽象层的实体模块,FPGA波形应用开发人员将硬件抽象层模块集成到自己的设计中,编译综合后形成加载文件,实现完整的FPGA功能。FPGA硬件抽象层实现底层屏蔽、数据路由、配置查询等三方面功能。

如图5所示,FPGA中程序逻辑分成三个层次,由下至上分别为驱动层、硬件抽象层和应用层。硬件抽象层可将具体的底层硬件驱动屏蔽为统一的逻辑接口供应用层调用。由于波形组件与波形组件、波形组件与硬件抽象层之间采用了统一的硬件抽象层接口进行交互,因此,将一个波形应用由平台A移植到平台B时,无需修改波形应用即可进行移植,进一步地降低了波形移植的复杂度,提高了FPGA波形应用的可移性。FPGA硬件抽象的收发信号定义如图6所示,由基本信号和可选信号、扩展信号组成,完成收发两个组件间数据交换,其读写时序如图7所示。

图5 FPGA硬件抽象层结构框图

图6 FPGA硬件抽象层基本信号定义

图7 FPGA硬件抽象层读写时序

4 波形实时性测试

系统测试波形具有数据通信和音频传输功能,对传输的实时性要求较高。在未采用SCA架构前,以传统手段开发的波形运行时端到端传输时延不大于1秒,采用轻量化SCA核心框架架构,使用CORBA中间件和硬件抽象MHAL后开发、移植波形后,波形传输时延增加了 500μs,基本可满足系统波形传输实时性要求,同时提高了波形了可移植性。

5 结论

采用基于 SCA体系架构硬件抽象层设计改造的某波形具有良好的可移植性和通用性,降低波形开发难度,降低开发费用,同时能保证波形指标,经测试采用CORBA中间件和硬件抽象层后实时性可以满足某些实际应用需求,对于更低时延要求的波形的支撑还需要进一步优化和研究。