简易系统级芯片内置高精度阻容振荡器的校准方法

2018-08-21张岩松梁步阁赵党军杨德贵

张岩松 梁步阁 赵党军 杨德贵

摘 要: 通过实验探究一种适用于超大规模集成电路(VLSI)领域系统级芯片片内阻容(RC)振荡器的校准方法。针对集成电路内部阻容振荡器输出时钟频率容易出现温漂、工艺离散导致不精确等现象,通过改良片内时钟校准逻辑,得出一种易于实现的、高效的、低成本的、可靠的方法。经试验验证,该方法可以有效保证振荡电路的输出精度,解决工艺、温度、电压等改变引起振荡器输出频率变化的问题。

关键字: 超大规模集成电路; 系统级芯片; 高精度校准; 阻容振荡电路; 时钟校准逻辑; 频率变化

中图分类号: TN784+.1?34 文献标识码: A 文章编号: 1004?373X(2018)16?0031?04

Abstract: A calibration method of RC oscillator in SoC suitable for the field of very large scale integrated circuit (VLSI) was explored by experiment. In allusion to the phenomenon that the output clock frequency of the RC oscillator in integrated circuit is prone to temperature drift and inaccuracy caused by process indiscretion, an easy?to?implement, high?efficient, low cost and reliable method is obtained by improving the calibration logic of the on?chip clock. The test verification indicates that the method can effectively guarantee the output precision of the oscillation circuit, and solve the problem of oscillator′s output frequency variation caused by the changes of process, temperature and voltage.

Keywords: VLSI; SoC; high?precision calibration; RC oscillation circuit; clock calibration logic; frequency variation

阻容振荡器因其频率容易调节、元件体积小、低成本低能耗等特点被广泛用于定时器和脉冲源中。它可以无需外部激励信号就可以将直流信号转化成周期性交流信号。然而,在实际应用中阻容振荡器会受到工艺和温度的限制,输出频率可能产生较大的误差。而传统的阻容振荡器仅是达到对波形进行整形的目的,本质上没有提高RC振荡器周期精度的作用。因此,一种简单、高效的校准阻容振荡器方法显得格外重要。

1 SoC内置高精度RC Oscillator的校准原理

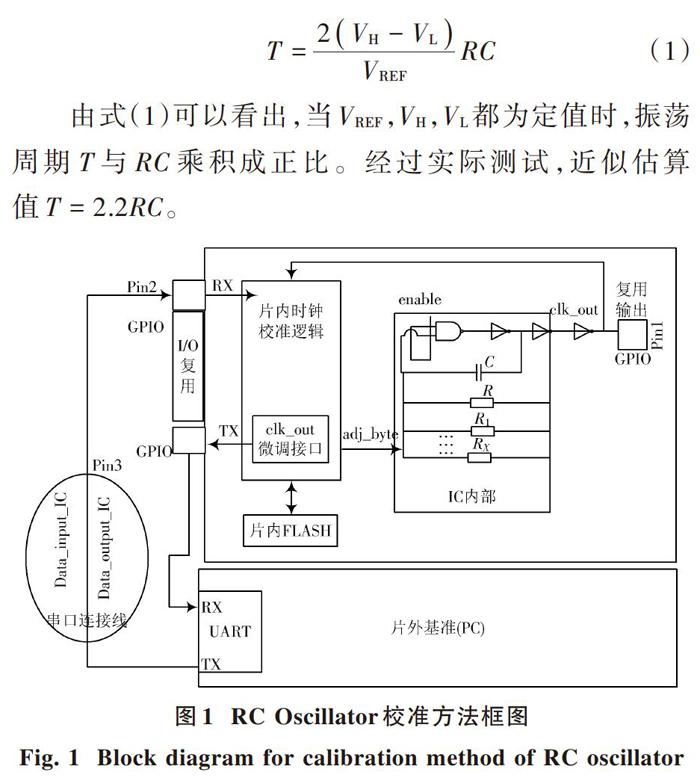

图1为RC Oscillator的校准原理设计框图,其由通过复用I/O连接的集成电路和片外基准电路构成。集成电路主要由RC振荡电路、片内FLASH和时钟校准逻辑电路组成。根据RC振荡电路内部结构可以得出,振荡电路的输出时钟clk_out的振荡周期T与RC关系:

在R下方有R1,R2,…,RX网络,可以补偿电路,用于微调R的值(通过数字接口adj_byte 来实现微调)。片内RC振荡电路设置有与可微调电阻连接的第一接口,通过接口执行代码来控制是哪一组电阻并联进电路中。通过改变并联电阻的数量和阻值来实现对R值的微调。由电阻并联公式可知:

当电路中电阻并联的个数越多,系统的总阻值越小;并联的阻值越大,调节幅度越小。

接口执行代码如下:

判断RC值是否大于预定值,如果大于预定值,则通过调节电阻值减小时间常数:

if((adj_cnt>16′h15f8)&&!(adj_up||adj_low))

beginadj_up<= 1′b1 ; bad_tr_en<= 1′b1 ;

adj_reg_24M<= adj_reg_24M ? 5′h1 ; end

判断RC值是否小于预定值,如果小于预定值,则通过调节电阻值增加时间常数

else if((adj_cnt<16′h15f8)&&!(adj_up||adj_low))

beginadj_low<= 1′b1 ;bad_tr_en<= 1′b1 ;

adj_reg_24M<= adj_reg_24M + 5′h1 ; end

当RC值正好等于预定值时,无需调整

else if((adj_cnt==16′h15f8)&&!(adj_up||adj_low))

beginadj_ok<= 1′b1 ; ok_tr_en<= 1′b1 ; end

当时间常数被调高后,再次判断是否频率与预定频率有偏差:

else if(adj_up)

begin if((adj_cnt<=16′h15f8)||(!adj_reg_24M))

beginadj_ok<= 1′b1 ; ok_tr_en<= 1′b1 ;end

else if(adj_cnt>16′h15f8)

begin adj_reg_24M<= adj_reg_24M ? 5′h1 ;

bad_tr_en<= 1′b1 ;end

end

同理还有调低的判断:

else if(adj_low)

begin if((adj_cnt>=16′h15f8)||(&adj;_reg_24M))

beginadj_ok<= 1′b1 ; ok_tr_en<= 1′b1 ;end

else if(adj_cnt<16′h15f8)

begin adj_reg_24M<= adj_reg_24M + 5′h1 ;

bad_tr_en<= 1′b1 ;end

end

片内时钟校准逻辑基于clk_out工作,解析RX的信息,依据其调整adj_byte的值,并通过TX反馈信息至片外。最终校准后的信息被保留在图1中所示的片内FLASH当中。与以往利用数字校准技术对输出频率进行微调的方法相比,该方法的CMOS FLASH macro具有极佳的反复操作性,因此,校准的RC振荡电路具备反复校准的功能。这样可以更好地解决温度漂移、电压变化等因素所引起的输出频率变化问题。复用I/O接口是集成电路与外界通信的端口,复用形式的I/O可以控制芯片面积,保护电路。I/O端口电路如图2所示。

2 SoC内置高精度RC Oscillator的校准流程

2.1 外部基准PC操作流程

整个校准过程片外仅需所述的片外基准PC辅助,无需时钟采样设备,可以通过RS 232端口或者USB端口跟被测IC建立物理连接。首先,外部基准PC启动校准界面,完成初始化,根据设置的目标时钟来初始化波特率,配置串口模式为:1位起始位(0)+8位数据+1位停止位(1)的模式。等待发出校准指令。以设定好的波特率发送00H,则会产生9 bit宽度的低电平信号。发送完成后立刻进入收数据模式,收完1 B数据后判断是否为AAH,为AAH则表明校准完成,内部已经达到目标频率,等待确认,并发送写入命令。此处写入是指将此时记录的adj_byte写入片内FLASH当中。在MPW shulte以及full mask初期需要加入等待确认,full mask后期此处为顺序执行,即校准完成后自动将adj_byte写入到片内FLASH当中。发送了写命令后,IC内部自动将此命令翻译为擦除+写操作,以支持重复写操作。如果校准没有完成,则计算是否到达扫描边界,如果到达边界,则表明片内时钟频率无法达到设定的目标,校准已经到达边界。达到上边界应该提示将目标频率调低,否则,调高。调整后重新进入收数据模式,再次校准。如果没有到达边界,则重新发送基准,重复校准。最后,等待写入完成。

2.2 片内时钟校准逻辑操作流程

校准阻容振荡器的重点是如何简洁、高效地衔接好内外数据。而管理好数据的存储、导出是方法的成败所在。在adj_byte为8 bit的情况下,8 bit的校准字节在一般的CMOS工艺下(例如CMOS 180 nm,110 nm)可以保障clk_out的误差范围控制在1%以内。如果要求更高(例如0.1%),可以扩展adj_byte的位宽(例如12 bit)。所以要将adj_byte值减小,clk_out频率增大。片内时钟校准逻辑采用的是二分法自动递进式修正校准字节adj_byte,以实现对片内RC振荡电路的内部电阻R的微调,从而补偿输出时钟。这样不仅提高了效率而且比传统方式更加简洁,即外部设置数值,当RX上升沿到来时,计数值大于目标值,即二分法判决到下半区,否则在上半区。系统将校准信息存储在片内FLASH中,片内时钟校准逻辑从片内FLASH中导出校准信息到片内时钟校准逻辑。判断导出的数据信息是否有效。因为擦除后的CMOS FLASH Macro,所有空间都为FFH,读出FFH表明此空间没有存储过信息,校准字节也不允许为FFH;如果判断数据为FFH,则将adj_byte 信息加载到adj_byte。判断Date_input_IC(片内RX)是否有下降沿到来。Uart的空闲状态下是高电平,一旦有下降沿到来,表示有信息进入IC。启动计数器,用clk_out计数低电平信号的宽度。片外基准PC以固定的波特率發送00H字节,因此,应该收到9 bit宽度的低电平。判断Date_input_IC(片内RX)是否有上升沿到来。上升沿到来表示一个字节传递结束。记录此时计数器的值,与目标值进行对比如果小于目标值表明内部频率偏小,则将adj_byte设置为最小值00H,即clk_out此时输出最大频率;否则将adj_byte设置为最大值FFH,即clk_out此时输出最小频率。

当输出最大频率时,通过片内TX,返回错误字节55H。并将计数器清零,并进入standby模式,等待Date_input_IC(片内RX)下一次下降沿到来。启动计数器,用更新后的clk_out重新计数低电平信号的宽度。判断clk_out是否调整为最大频率。如果不是则在最大频率大于目标频率的前提下,进入顺序微调频率的过程。在顺序调整过程中,必然有adj_byte等于00H的条件下记录宽度大于目标值,因此,顺序增加adj_byte就能使clk_out逐渐逼近目标。监测Date_input_IC(片内RX)上升沿到来时,记录计数器的值,一旦出现记录值小于目标值,则跳出停止校准返回OK=AAH(意味着内部频率达到目标);否则将adj_byte加1,经过微调后,再通过TX返回ERR=55H,继续校准。否则在 adj_byte等于00H的条件下,判断内部最大频率是否大于目标。如果大于则具备调整的条件,从而逐次顺序微调,否则不具备调整的条件,应该直接停止校准,返回OK=AAH。

当计数值大于目标值时,进入二分法的下半区,过程与上半区大致相同。校准成功后,立即返回AAH。正常情况下,将导出的有效校准信息加载到adj_byte。

3 仿真与实验结果

本文仿真实验利用Nc?verlog软件编写算法。图3是模拟仿真时序流程图。从图中可以看出通过不断的校准,振荡器的波形误差在逐渐减小。第一次时,可以通过时序图看见数据,因为偏差较大使数据在最后一位发生错误,数据0变成了1,结果变得不准确。第二次,经过校正后的数据偏差变小,虽然数据仍有偏差,但是本文方法有着很好的容错性,数据没有发生错误。经过几次校正后,可以看见误差几乎没有,系统校正效果较好。校正结束后,信号写入FLASH内。

在实际工程应用中,已经成功将此方法转换成芯片模式生产出来,并应用在实际中。为测试该方法的性能,搭建芯片测试环境,如图4所示。借助串口助手软件将设计的电路板与软件相连。电路板分为两部分,接口部分与芯片部分。调节电路,进入工作模式,在串口助手的界面中如图5所示,输入00,然后观察返回的数据,当界面出现AA是代表校正完成。

从图6可以看出,校正中,频率一直在逐步减小靠近目标值,并在几次之后达到AA。而从对应的示波器显示的波形,可以清楚的看到,频率一直在细微的减小趋近目标值。

4 结 论

本文设计的阻容振荡器校准方法缩短了设计周期,需求的外部辅助设备很少,且常见,并不占用IC的I/O资源,合理地降低了设计风险,是一种易于实现的、很有效的RC振荡器校准方法。经过仿真验证和实际硬件测试均可以有效地证明该方法与以往的方法相比更加可靠高效。

参考文献

[1] 李琳.RC正弦波振荡器的仿真研究[J].黑龙江科技信息,2016(2):16.

LI Lin. RC sinusoidal oscillator simulation research [J]. Heilongjiang science and technology information, 2016(2): 16.

[2] 王展飞,鲁文高,李峰,等.一种频率线性可调的正交正弦波振荡器[J].北京大学学报(自然科学版),2009,45(1):49?53.

WANG Zhanfei, LU Wengao, LI Feng, et al. A linearly tunable quadrature sinusoidal oscillator [J]. Acta Scientiarum Naturalium Universitatis Pekinensis, 2009, 45(1): 49?53.

[3] WANG Guangyi, CAI Bozhen, JIN Peipei, et al. Memcapacitor model and its application in a chaotic oscillator [J]. Chinese physics B, 2016, 25(1): 010503.

[4] 劉帘曦,杨银堂,朱樟明,等.一种新型高精度RC振荡器电路设计[J].电路与系统学报,2005,10(1):147?150.

LIU Lianxi, YANG Yintang, ZHU Zhangming, et al. Design of novel high?accuracy RC oscillator [J]. Journal of circuits and systems, 2005, 10(1): 147?150.

[5] 李松松.基于Multisim的电子线路设计与仿真[M].杨凌:西北农林科技大学出版社,2014.

LI Songsong. Electronic circuit design and simulation in Multisim [M]. Yangling: Northwest A&F; University Press, 2014.

[6] 李城鑫.微波光子振荡器的研究[D].成都:电子科技大学,2015.

LI Chengxin. Research on microwave photonic oscillator [D]. Chengdu: University of Electronic Science and Technology of China, 2015.

[7] 王华,宋千,周智敏.利用对比度最优准则的压控振荡器调频非线性误差估计与校正方法[J].国防科技大学学报,2015,37(2):65?71.

WANG Hua, SONG Qian, ZHOU Zhimin. Method of voltage controlled oscillator frequency nonlinearity estimation and correction based on contrast optimization [J]. Journal of National University of Defense Technology, 2015, 37(2): 65?71.

[8] 徐卫林.无线射频通信片上系统的压控振荡器与电源管理的研究[D].武汉:武汉大学,2011.

XU Weilin. Research on voltage controlled oscillator and power management of radio frequency communication SoC [D]. Wuhan: Wuhan university, 2011.

[9] 牛萍娟,于莉媛,毛陆虹,等.基于共振隧穿机制的太赫兹波振荡器特性模拟[J].电工技术学报,2014,29(12):102?106.

NIU Pingjuan, YU Liyuan, MAO Luhong, et al. Simulation of characteristics of terahertz oscillator based on resonant tunneling mechanism [J]. Transactions of China Electrotechnical Society, 2014, 29(12): 102?106.

[10] 苏玉刚,谢诗云,呼爱国,等.LCL复合谐振型电场耦合式无线电能传输系统传输特性分析[J].电工技术学报,2015,30(19):55?60.

SU Yugang, XIE Shiyun, HU Aiguo, et al. Transmission property analysis of electric?field coupled wireless power transfer system with LCL resonant network [J]. Transactions of China Electrotechnical Society, 2015, 30(19): 55?60.

[11] 魏克银,徐俊霞,韩辉,等.带阻容负载的独立发电机整流系统的静态稳定性研究[J].电工技术学报,2012,27(10):228?234.

WEI Keyin, XU Junxia, HAN Hui, et al. Study on steady?state stability of generator?rectifier system with capacitor?resistor load [J]. Transactions of China Electrotechnical Society, 2012, 27(10): 228?234.