一种细步进频率源的设计

2018-08-04林彬王洪林

林彬 王洪林

一种细步进频率源的设计

林彬 王洪林

中国船舶重工集团公司723所,江苏 扬州 225001

介绍了一种采用直接式数字频率合成技术和锁相源技术相结合产生超低频率细步进频率源的设计。该模块工作频段为10 kHz~1 GHz,步进10 kHz;功率8±3 dBm;内置LAN接口,可以通过标准SCPI指令进行控制。

直接式数字频率合成;锁相环;超低频率;SCPI指令

现在,微波信号源在雷达与电子对抗系统和电磁兼容系统中的应用日趋广泛,数量日趋增多。然而,现在常用的微波信号源体积庞大、功耗大、价格高。本模块采用成熟的锁相环(PLL)技术、直接数字频率合成(DDS)技术、嵌入式控制技术和LAN通信技术相结合的方式成功地克服了上述缺点,具有体积小、功耗低、操控方便、价格低廉的特点。

1 设计指标要求

(1)输出频率:范围10 kHz~1 GHz,步进10 kHz;(2)输出功率:范围8±3 dBm;(3)相噪:<﹣100dBc/Hz@1 kHz;(4)杂散:<﹣70 dBc;(5)置频时间:<1 ms;(6)结构尺寸:110×95×18 mm。

2 方案设计

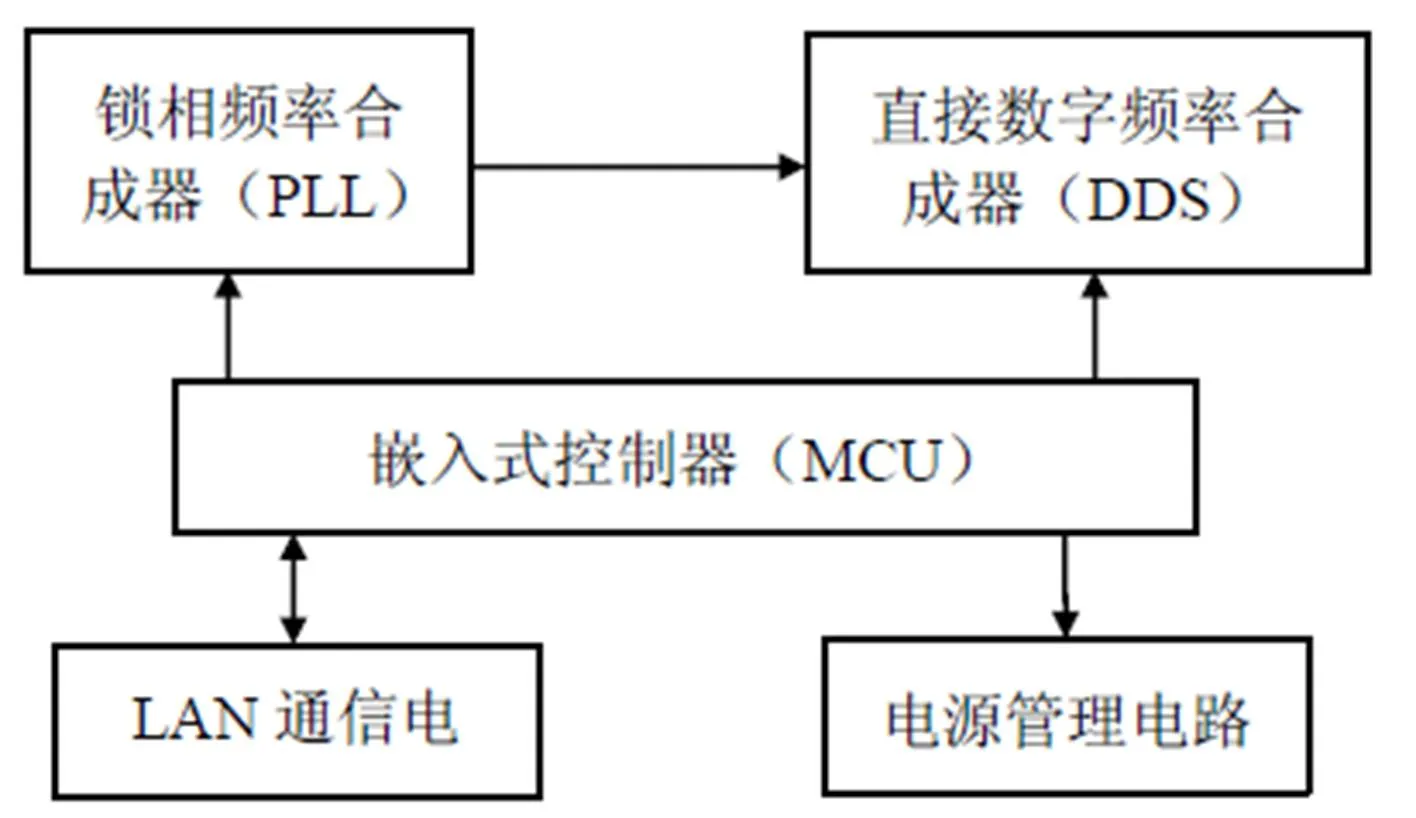

根据设计指标要求,模块做如下设计(见图1)。

该模块主要由嵌入式控制器(MCU)、PLL电路、DDS电路、数控衰减器、开关滤波与放大电路、电源管理模块和LAN口通信电路等7个部分构成。

(1)MCU是模块的控制中心,我们采用了ST公司的ARM32处理器STM32F107VCT6。主要负责解析LAN口收到的控制指令并根据指令要求设置PLL和DDS的寄存器,控制PLL和DDS输出正确的频点,输出正确的数控衰减码,选通正确的滤波与放大通道,控制模块输出正确的射频信号。

图1 方案设计框图

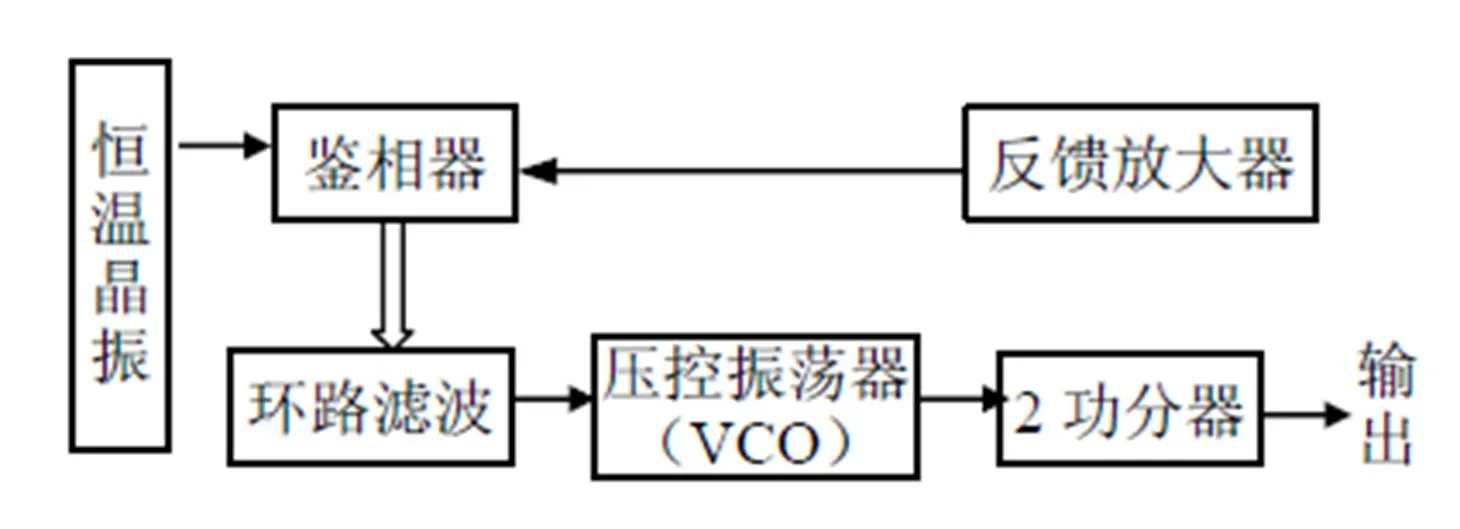

(2)PLL电路为DDS提供参考时钟,决定了最终输出信号的相噪水平。我们采用如下方案(见图2)。

图2 锁相频率合成器

主要器件型号如下:

恒温晶振:黑土PFOC10-0106;

鉴相器:ADI HMC704LP4E;

VCO:Z-Com V810ME08-LF。

锁相频率源产生2.75~3.5 GHz的信号,放大至﹣0±2 dBm为DDS电路提供参考时钟。

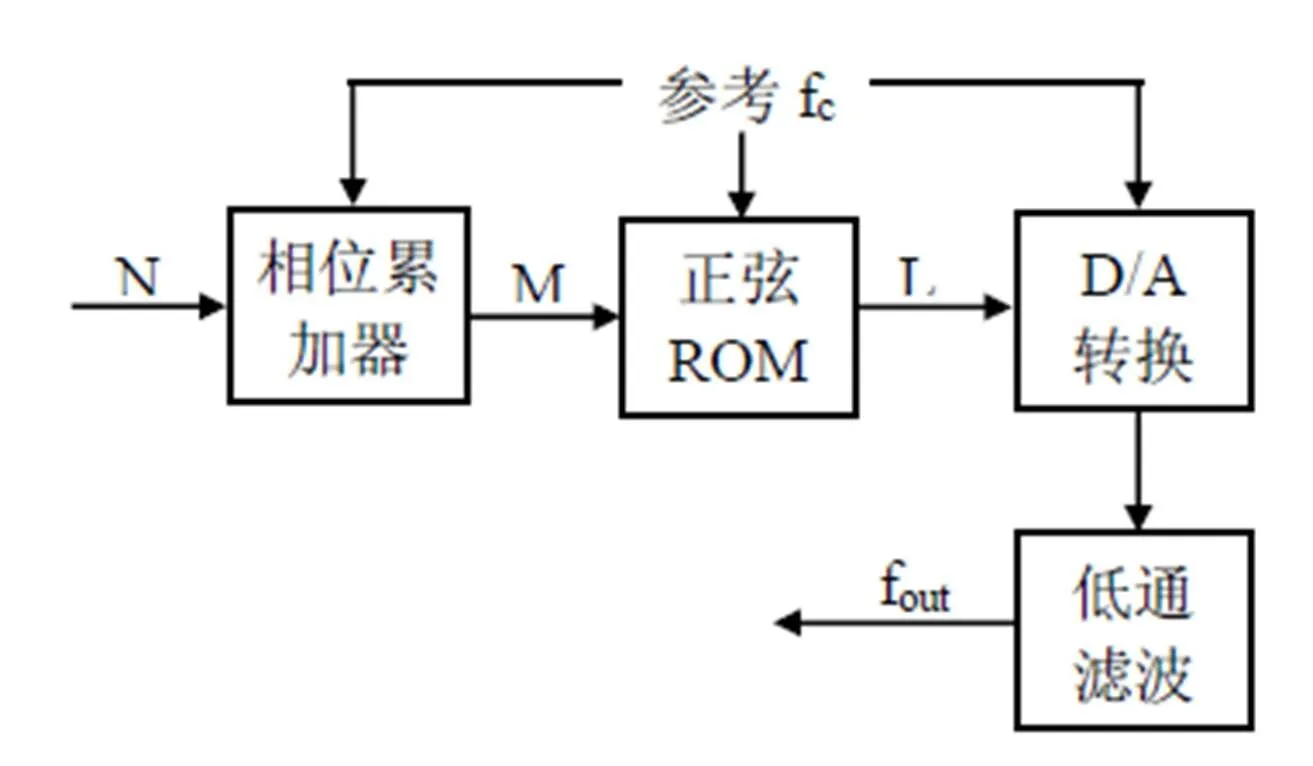

(3)DDS电路由相位累加器、正弦ROM查找表、数模转换DAC、低通滤波器构成。其原理框图见图3。

图3 DDS工作原理

该部分电路我们采用ADI公司的AD9914,该芯片具有参考频率高、相位噪声低等特点。其差分输出用巴伦转换成单端信号,分10 kHz~50 MHz和50~1 000 MHz两路分别匹配放大至8±3 dBm。

(4)电源管理模块设计:稳压芯片采用低噪声稳压模块LT3060ITS8和LM1117IMPX-3.3及LT1764EQ,电源的输入和输出端都用磁珠和钽电容滤波将电源引入的噪声降到最低。

(5)LAN口通信模块采用有人科技的SPI-LAN模块USR-ES1,MCU控制模块工作在TCP/IP Server模式,支持标准SCPI指令控制。

3 设计指标及难点分析

本信号源的相噪指标由PLL和DDS共同决定。PLL采用低相噪(﹣155 dBc/Hz@1 kHz)的100 MHz恒温晶振做参考,鉴相器采用10 MHz鉴相的整数分频模式。这样就可以提供一个频率变化范围2 700~3 500 MHz,步进10 MHz的参考时钟信号。用ADI公司的ADISimPLL软件计算相噪水平可以达到﹣108 dBc/Hz@1 kHz。而后端DDS的相噪优于﹣128 dBc/Hz@1 kHz,对于整体指标优于﹣100 dBc/Hz@1 kHz不会产生影响。因此此项指标满足要求且余量充足。

杂散指标一直是DDS频率源的设计重点和难点,主要由DDS决定。由DDS的工作原理可知相位截断误差、幅度量化误差、时钟混叠和数字信号串扰是产生杂散的主要因素。我们采用加载线上串接电阻的方式可以方便地滤除数字串扰信号,在此不再赘述。对于相位截断、幅度量化和时钟混叠带来的杂散,由于牵涉到极大数的计算问题,受PC机性能所限误差较大,很难计算准确,加上频率范围较宽点数多很难将杂散信号一一计算到位。我们采用时钟拼接的方式进行设计。具体操作步骤如下:(1)选择合适的时钟信号频率;(2)使用自动测试手段测试频率范围内所有信号的杂散值,剔除超标的频点;(3)更改时钟信号的频率;(4)重新测试原先测试超标的频点,进一步剔除超标的频点;(5)重复步骤3和4,直至所有的频点都满足指标要求,记录下每个频点对应的时钟频率和控制字;(6)将上述测试结果拼接在一起针对不同的频点加载不同的时钟和控制字,最终定型完成。

4 测试结果

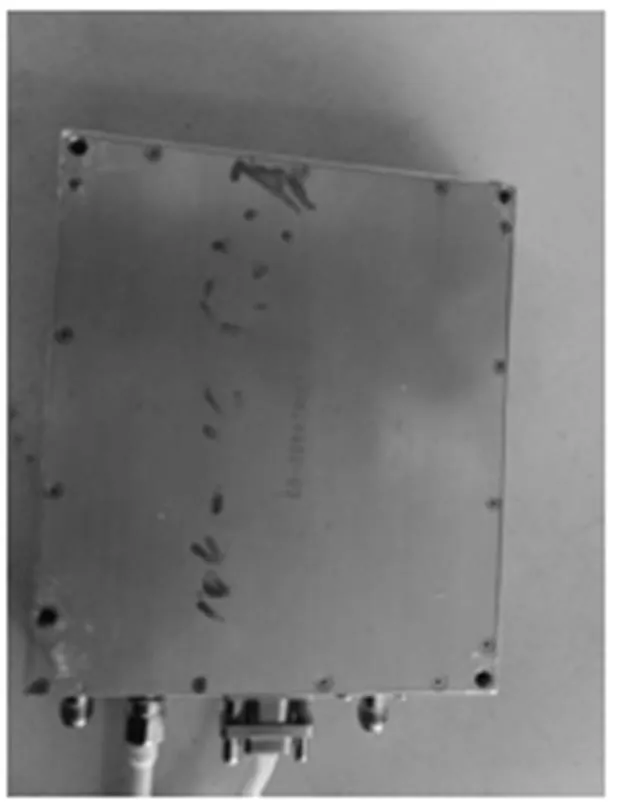

用安捷伦频谱仪N9030A测试的频率源的输出如图4,输出频点1 GHz,输出功率6.46 dBm,杂散优于﹣60dBc,相位噪声﹣106 dBc/Hz@1 kHz。实物如图5所示。

图4 输出结果

图5 实物图

5 结束语

本文介绍了一种低频率细步进微波频率源的实现方案,电路结构上采用整数分频的锁相频率源技术、DDS技术和LAN通信技术相结合,可以通过LAN口发送标准SCPI控制指令设置输出频率和功率。实测结果表明输出信号指标都满足设计要求。由于体积小、功耗低和兼容SCPI指令控制,可以方便地应用于雷达与电子对抗系统和电磁兼容系统中。

[1]张厥盛,等. 锁相技术[M]. 西安:西安电子科技大学出版社,1998.

[2]廖承恩. 微波技术基础[M]. 西安:西安电子科技大学出版社,2011.

[3]ADI.HMC704 Datasheet[Z].

[4]ADI.AD9914 Datasheet[Z].

[5]田新广,张尔扬. DDS 幅度量化杂散信号的频谱研究[J]. 通信学报,2003,24(7):79-85.

[6]高建华. 可编程仪器的标准指令(SCPI)[Z]. 中国惠普公司.

[7]孙续. 自动测试与可程控仪器[M]. 北京:电子工业出版社,1994.

Design of a High Frequency Band PLL Signal Generator

Lin Bin Wang Honglin

CSIC 723 Institute, Jiangsu Yangzhou 225001

A Signal Generator based on DDS and PLLs, which is working at the band cover from 10 kHz to 1 GHz. The Frequency Step is 10 kHz. Output Power Range is 8±3 dBm. It Can be controlled by standard SCPI CMD through LAN Port.

DDS; PLLs; Low Freq-Band; SCPI CMD

TN74

A