基于PSoC编码检测器的设计及实现

2018-07-31刘亦萍李德运何学诚陈陶龙康杨奇凡

刘亦萍, 李德运, 何学诚, 陈陶, 龙康, 杨奇凡

(上海第二工业大学 工学部,上海 201209)

0 引 言

CYPRESS公司在全球率先实现了在单芯片内的“模拟和数字全混合阵列”[1],对未来电子系统的设计方法产生了深远的影响,在半导体技术高速发展的今天,芯片集成度越来越高,使得在单芯片上实现复杂系统成为可能,Cypress公司率先在业界实现了完全意义上的PSoC解决方案,即在单芯片上实现了MCU、数字和模拟系统的高度集成[2]。PSoC技术的不断发展将大大推动电子系统设计方法的创新,并且对未来嵌入式系统设计领域带来深远的影响。

本项目研究有限自动状态机(Finite State Machine,FSM),利用摩尔状态机设计编码检测器[3],用PSoC芯片实现数字编码检测器。

本文将介绍通过控制逻辑电路,对计数器控制查找表产生的1001序列进行检测,再通过编写代码实现在LCD屏幕上显示出检测到1001的次数。图1是编码检测系统总框图。

图1 编码检测系统总框图

1 检测信号发生

图2中a模块是设计集成的十六进制计数器,通过Q3,Q2,Q1,Q0状态输出控制查找表LUT实现所需1001信号的发生[4]。

图2 信号发生集成图

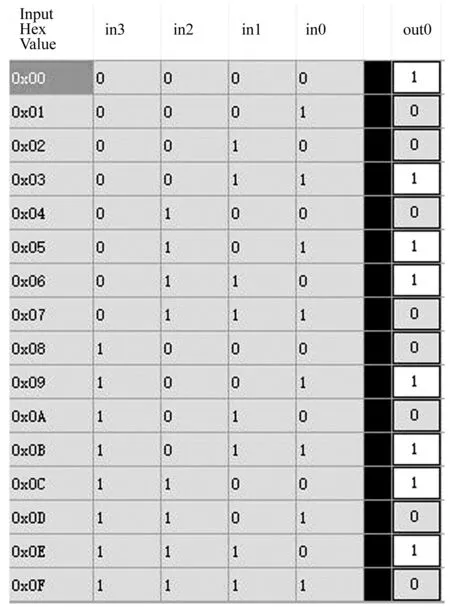

图3为由查找表设计的检测信号,in3,in2,in1,in0为Q3,Q2,Q1,Q0控制,Out0为检测信号的输出,其中含有2个1001序列。

图3 1001检测信号设计

2 序列检测模块

设计1001序列检测器的逻辑电路图[5],因为检测器通过分析有5种独立的状态,所以使用了3个D触发器(当n=3时会产生23=8种状态)。

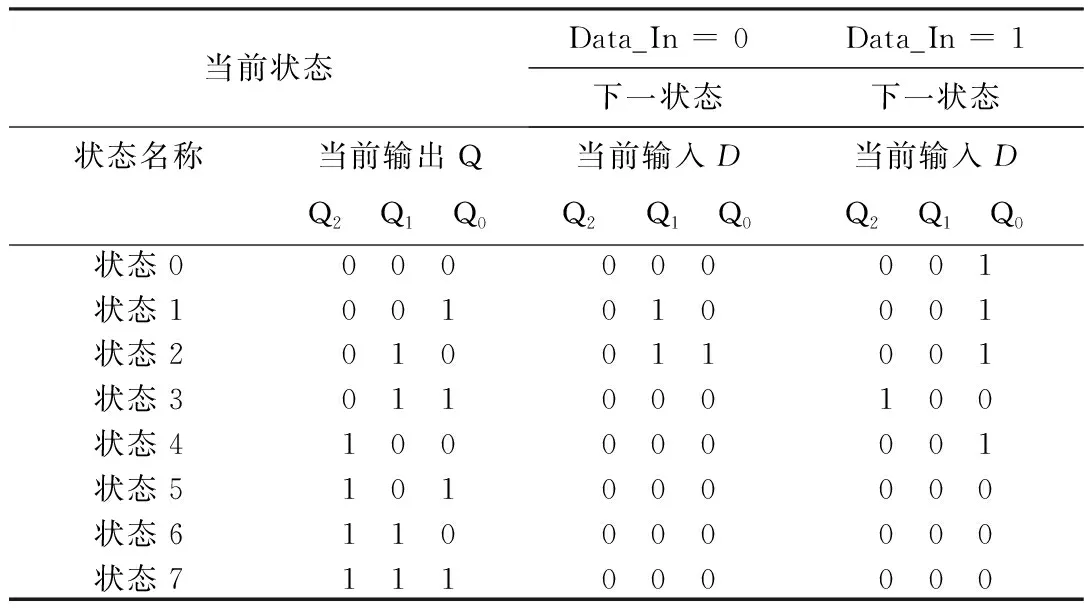

表1是检测器的状态转换表,状态转换表列出了数据输入端(Data_In)情况,并且状态机将随着输入信号变化到两种可能的下一状态中的其中一个。

表1 1001序列检测器状态转换表

通过状态转换表可得出各触发器的布尔逻辑表达式与检测器的输出布尔逻辑表达式:(Data_In代表输入,Detected代表输出)

根据以上表达式,在PSOC 3.3平台上设计出逻辑电路如图4所示。

图4 1001序列检测器电路图

将原理图4集成为图5中所示的jiance原理图符号,简称为“1001逻辑序列检测”[6]。

将1001信号发生与1001序列检测相连,实现了1001序列检测。

图5 1001序列检测模块图

3 计数显示

对检测出的1001信号的次数可以在LCD显示屏上显示[7]。图6为计数显示程序框图。

图6 计数显示程序框图

4 系统集成

图7为1001序列检测系统集成原理图。打开引脚分配见表2,进行相应的引脚分配[8],通过十六进制计数器和查找表产生的1001信号,经过数字电路构成的1001序列检测器检测,由LCD显示检测出的1001的次数。程序经编译、下载到PSoC开发板上,并在PSoC板上连接好外部接线[9],经过软硬件联调可见,1001序列检测到则LED亮,并可在LCD显示屏上显示检测到的次数。

表2 引脚分配

图7 1001序列检测系统原理图

5 结束语

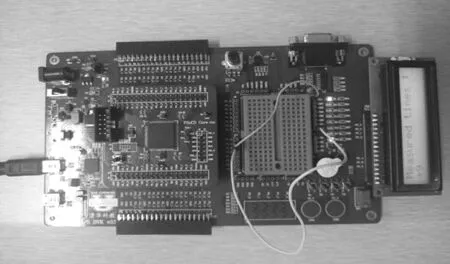

图8 基于PSoC编码检测器的硬件实现

在数字系统中,有限自动状态机(FSM)的应用研究不多,在本项目里,通过Cypress公司开发的PSoC开发板上设计实现了1001序列的检测,并通过PSoC C语言编程,实现了对检测结果的计数和LCD的显示[10]。图8为基于PSoC编码检测器的硬件实现图。

运用有限自动状态机的设计方法,同时使用PSoC开发板与Cypress公司的PSoC 3.3开发平台设计相结合缩短了开发周期。