基于USB的多功能音频同步收发开关矩阵设计

2018-07-27张雷邹德军张海庆

张雷,邹德军,张海庆

(中国电子科技集团公司第41研究所,山东青岛,266555)

0 引言

短波通信控制器在短波通信系统中扮演着神经枢纽的角色,其性能对于整个通信系统的总体性能有着直接且至关重要的影响。随着通信装备的发展以及测试要求的提高,以往采用单台测试仪器针对单一测试指标进行工位式人工测试的方式已无法满足短波通信控制器测试规程中对于多功能、多参数、高精度、高效率、低成本、自动化的测试要求。因此,需要采用自动测试的方式来提高短波通信控制器在调试、生产、维修过程中的效能。基于被测件的测试需求,本文提出了一种基于USB的多功能音频同步收发开关矩阵,对于短波通信控制器的高效、自动测试具有重要意义。

1 总体设计

开关矩阵对外接口主要包括16通道差分音频测试接口、8通道受送话器测试接口、16通道RS-232/422测试接口、16通道PTT/MUTE信号测试接口、示波器接口、信号源接口以及音频测试接口,其主要功能主要包括:被测设备测试接口的互通互联测试、通道内部收发通路的短接直连测试、多种采样率音频信号的同步采样存储和模拟输出、串口数据的收发、PTT/MUTE信号的读取和发生功能以及测试信号的激励和监控功能。

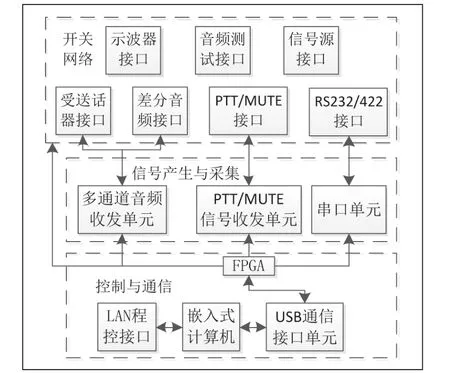

开关矩阵主要分为硬件部分和软件部分。其中硬件部分主要由嵌入式计算机、USB通信接口单元、FPGA、开关网络、多通道音频收发单元、串口单元以及PTT/MUTE信号收发单元等组成,如图1所示;软件部分主要为上位机软件。

嵌入式计算机为以Intel处理器为核心的嵌入式CPU处理器,它作为开关矩阵的主控机,通过USB通信接口实现与FPGA的通信。FPGA作为下游电路的控制核心,通过对嵌入式计算机发送的指令和数据进行翻译、缓存和时序的处理,实现对各个其余各个功能单元的控制和数据的发送。另外FPGA还负责读取开关网络、信号产生与采集部分的状态和数据,通过USB通信接口单元发送到嵌入式计算机中进行处理和显示。

图1 开关矩阵组成框图

开关矩阵支持本地以及远程两种控制方式,能够通过嵌入式计算机的LAN程控接口,实现控制命令和数据的交互,以便支持在自动测试系统中进行自动控制。

2 开关网络设计

开关网络主要实现同类多通道测试接口间的短接直连、通道内部收发通路的短接直连,并为信号的检测、数据的收发以及激励信号提供通路。

开关矩阵采用内部数据总线的基本构架进行开关网络的搭建,共包括受送话器、差分音频、RS232/422、PTT/MUTE4种总线类型,分别用来传输相应类型的数据和信号。外部同种类型的任意两测试接口通过内部开关实现与同一内部数据总线的互联,从而实现任意两通道的互通互联。示波器接口通过开关与开关网络内部所有总线建立连接,可根据不同的测试需求,实现与差分音频测试接口、受送话器测试接口、RS-232/422测试接口、PTT/MUTE信号测试接口中任意通道的连通,实现测试信号的监控。音频测试接口、信号源接口可实现与差分音频测试接口、受送话器测试接口任意通道的直连,从而可实现音频信号的测试和激励。

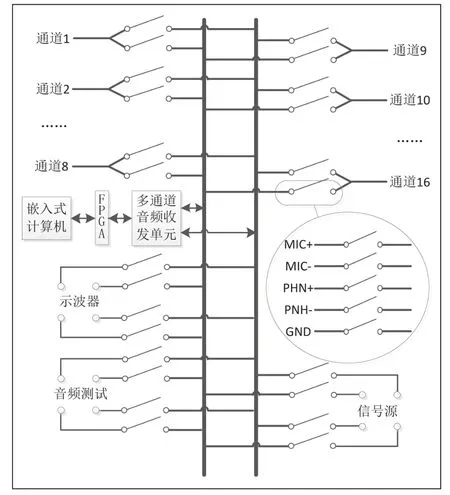

如图2所示,为差分音频开关网络的基本构架,其中任意两通道可通过一根总线实现短接互联,同时可使用示波器和音频综合测试仪通过示波器通道和音频测试通道实现对音频信号的监控和分析。另外可根据不同的测试需求,可通过信号源接口对任意通道的测试激励信号进行加载。通过多通道的短接互联,能够实现多台被测设备收发通道的同时测试,开关矩阵最多可实现同类通道中任意4通道的短接直连,极大程度上提高了测试效率。

图2 差分音频开关网络构架

对于内部开关的通断控制,开关矩阵采用USB批量传输的方式实现命令的发送,控制命令经过FPGA的翻译和时序处理,通过SPI总线控制开关驱动器进行相应通道开关的通断操作。

3 音频同步收发实现

■3.1 音频收发基本原理

开关矩阵是通过多通道音频收发单元、USB通信接口单元、嵌入式计算机以及FPGA四者实现音频数据的同步收发的。多通道音频收发单元主要由8片音频编解码芯片(TLV320AIC3206)及相应的开关通道构成,TLV320AIC3206具有配置灵活、多功能、低功耗的特点,片上配有可编程的输入/输出接口、可编程音频放大器、可编程PLL以及可灵活配置的音频ADC/DAC,采样率支持8kHz~192kHz灵活配置,可完全满足开关矩阵的功能需求。

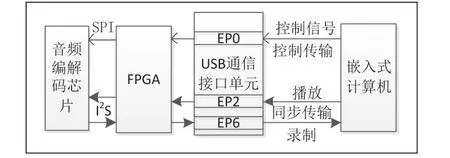

嵌入式计算机作为主控机发起数据的传输,其传输数据主要包括:音频收发控制信号(音频编解码芯片的配置信息、采样率设置、音量设置、静音)和音频数据。控制信号的方向主要由嵌入式计算机经过USB接口和FPGA到多通道音频收发单元,其传输数据量较小,主要通过USB的控制传输方式实现;音频信号的传输是双向的,本文采用USB的同步传输方式实现,同步传输方式是专门针对音频、视频等流媒体的特点所使用的传输模式,它能够提供稳定的带宽给采用该模式的设备或端点。

FPGA为数据传输过程中的缓冲单元以及多通道音频收发单元的控制模块,保证控制信号以及音频数据能够以正确的时序发送给下游的音频编解码芯片,控制信号和音频数据分别采用SPI总线和I2S总线实现数据的收发。开关矩阵的音频收发原理如图3所示。

图3 开关矩阵的音频收发原理图

■3.2 音频同步收发方案

音频同步收发是开关矩阵的关键技术之一,能够实现多通道音频数据的低延迟收发,做到音频的实时播放和录制,保证音频数据的准确性和音频播放时的听觉效果。

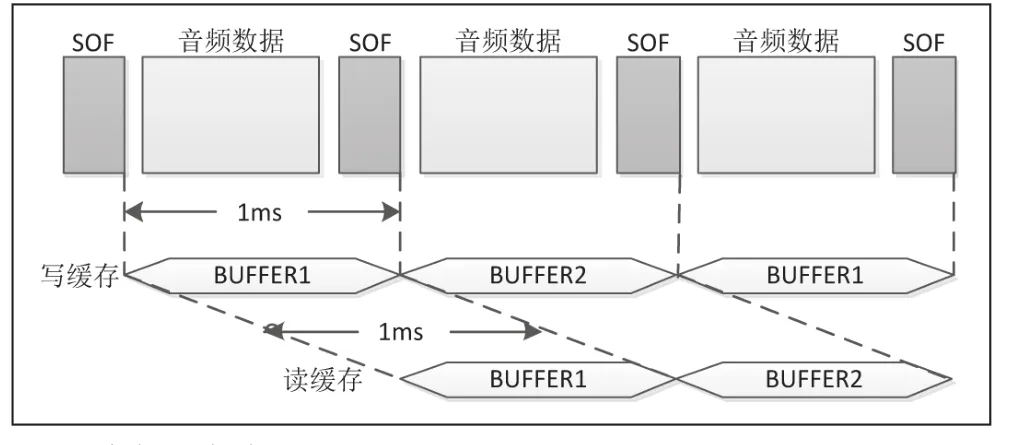

USB在全速模式下使用同步传输方式进行音频数据传输时,USB主机每隔1ms发送一帧数据,并且主机将SOF包作为每个帧的起始,通过此种方式来确保数据的等时收发。只要将USB每毫秒收发的数据量与音频数据的采样率相匹配,便可保证数据收发的同步性,音频采样率FS与每帧发送数据的大小DL的关系如下。

在FPGA中采用乒乓BUFFER的机制实现音频数据的同步存储和读取,并利用USB每帧数据开始时的SOF信号位,将每帧1ms的数据交替存储在两个BUFFER中,并同步对两个BUFFER进行数据读取,只要保证每帧的数据量与音频数据的采样率相匹配便可实现音频的同步收发。

图4 音频同步读写原理图

由于USB控制器与音频解码芯片各自使用的是独立的时钟,为保证数据写入速度和数据读取速度的严格匹配,减少丢包率,开关矩阵使用FPGA内部的PLL进行时钟的调整,使USB控制器时钟与音频解码芯片时钟精确匹配,确保数据的高质量传输。开关矩阵音频同步读写的原理如图4所示。

4 结论

本文所述基于USB的多功能音频同步收发开关矩阵已成功应用于某通信设备厂家,能够对生产调试、环境试验、外场实验等多种测试需求提供有效支持,大大的提高了产品的测试效率,节约了人工与时间成本,并为将来生产线扩容提供了有效支撑,产生了良好的经济效益。