秒脉冲分配网络高精度时延控制设计与实现

2018-07-16刘铁强

刘铁强,霍 婧

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081; 2.卫星导航系统与装备技术国家重点实验室,河北 石家庄 050081)

0 引言

卫星导航系统中,导航、定位和授时都是以“时间”为基础,要实现高精度导航、定位和授时需要有统一的时间频率基准[1]。秒脉冲分配网络作为时频系统的重要组成部分,接收站时频提供的1 pps信号,分配为多路为用时系统的各个分机提供时间基准,确保用时系统各设备工作在统一的时间基准上[2]。

脉冲信号的主要参数包括上升/下降时间、传输时延一致性、幅度、阻抗频率和占空比等[3],其中,传输时延一致性是体现其指标的最重要的参数[4]。因此,如何控制脉冲分配网络末节点1 pps信号时延,实现末节点1 pps相位高度一致成为研究重点。

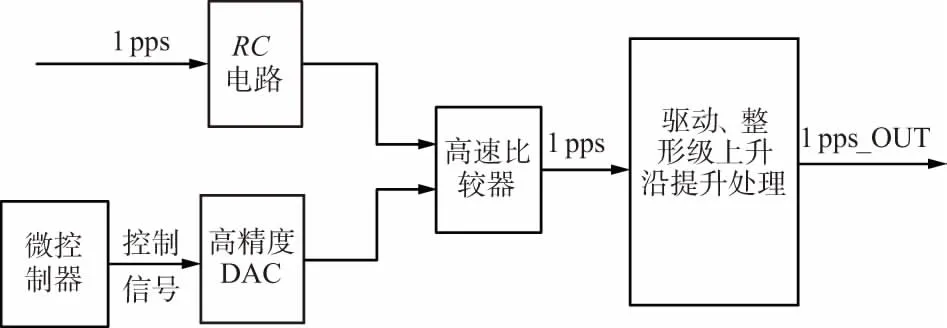

目前1 pps时延调整多采用修正传输电缆的方法来实现,该方法能够实现时延的精确调整,但在工程应用上操作复杂,非常耗费人力、物力。本文研究设计了一种基于高精度DAC控制的秒脉冲分配网络时延调整方法,结合RC充放电电路与高速比较器的特性,通过控制DAC输出电压改变比较器的比较电平,实现1 pps时延的精确调整。该方法实现简单,时延调整范围可控,调整精度高,有效解决通过修正电缆来实现1 pps时延调整所存在的缺陷。

1 秒脉冲分配技术

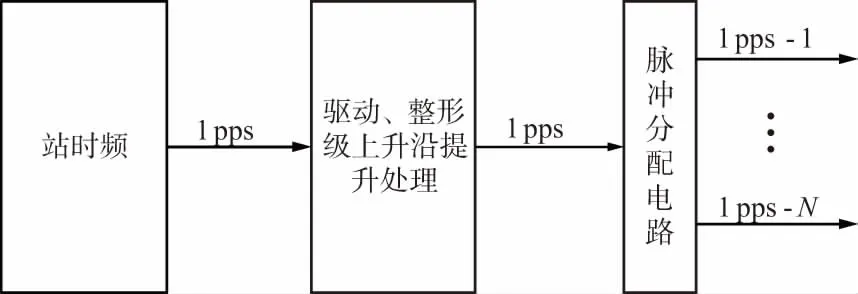

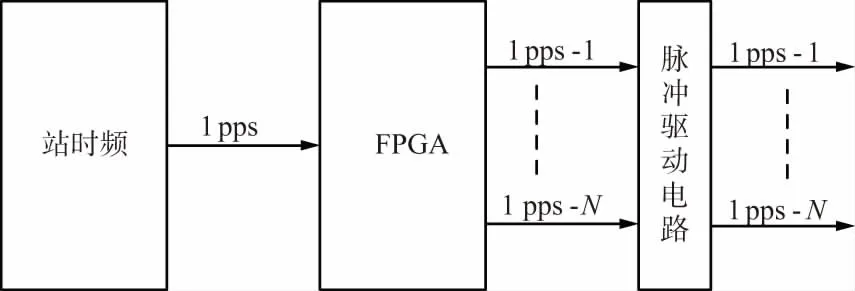

能够实现秒脉冲分配的方法有多种[5],其中基于硬件电路的脉冲整形与驱动分配法与基于现场可编程门阵列的FPGA软模块的脉冲分配法在工程上使用最多[6]。脉冲整形与驱动分配法原理框图如图1所示,基于FPGA软模块的脉冲分配法原理框图如图2所示。

图1中,站时频提供的标准1 pps信号经过前级脉冲整形、驱动及上升沿提升处理后作为后级脉冲分配电路的输入[7],经后级分配电路分成多路1 pps输出;在对脉冲信号做前级的相应处理时,脉冲信号的驱动能力通常要考虑到后级分配电路输出1 pps的数量,以保证输出1 pps的指标[8]。图2中,站时频提供的标准1 pps信号经FPGA和配套外围整形电路分成多路1 pps输出[9]。

图1 脉冲整形与驱动分配原理

图2 基于FPGA软模块的脉冲分配原理

2 传统秒脉冲分配网络设计分析

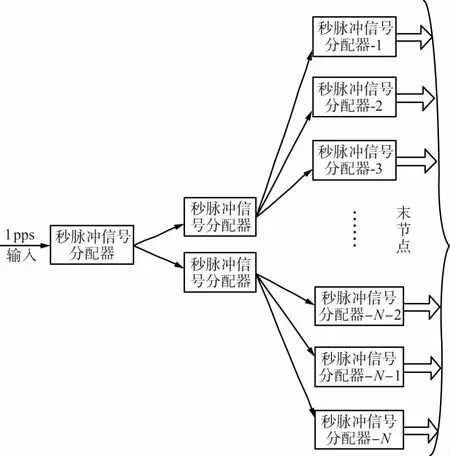

传统的秒脉冲分配网络采用多级脉冲分配的架构,每一级由多个秒脉冲信号分配器组成,接收上一级分配输出得1 pps信号,分配放大后传输至下一级,最后一级分配器的输出定义为分配网络的末节点,为用户提供多路1 pps信号。其原理架构图如3所示。

图3 秒脉冲分配网络架构

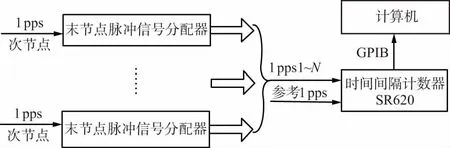

由于各秒脉冲信号分配器内脉冲信号驱动芯片、机箱内以及机箱之间电缆长短等存在差异[10],造成末节点1 pps信号之间相位不一致。目前的解决方法是控制末节点电缆长度,调整各路1 pps信号的时延,达到时延控制的目前,其时延测试框图如图4所示。

图4 时延调整测试框图

从次节点取一路1 pps信号作为时差测量的基准点,接入时间间隔计数器(SR620)的通道A,将末节点输出的1 pps信号依次接入SR620的通道B[11],测量参考信号与末节点各信号的相位差△ti(i=1……N):

△ti=Tref-T620-Ti,

(1)

式中,△ti为末节点1 pps与基准点1 pps相位差;Tref为基准点1 pps相位;T620为SR620自身固定时延;Ti为末节点1 pps相位[12]。

以末节点输出的第1路1 pps作为用时系统的参考点,根据获取的时差数据ti计算其余各路1 pps与参考点的时差△Tj(j=1……N-1):

△Tj=△t1-△ti,

(2)

式中,△Tj参考点1 pps与其余末节点1 pps相位差;△t1为参考点1 pps与测量基准点1 pps相位差;△ti为末节点1 pps与测量基准点1 pps相位差。

获取末节点各路1 pps信号与物理参考1 pps相位差后,计算并修正电缆长度,达到控制末节点1 pps时延的目的,实现末节点各路1 pps信号相位高度一致。

通过该方法可以实现末节点的时延控制,但该方法存在的最大缺陷是如果某台秒脉冲信号分配器发生故障而更换,由于设备之间的差异造成末节点相位发生变化,需要重新修正电缆长度。

3 基于高精度DAC控制的秒脉冲信号时延控制设计

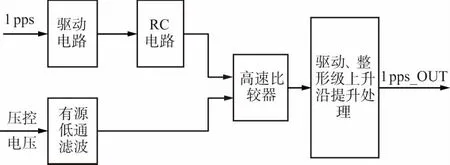

基于高精度DAC控制的秒脉冲信号时延控制设计原理框图如5所示。外部输入1 pps信号经过RC充放电电路后使得其上升沿减缓,控制高精度DAC输出电压值,改变高速比较器的比较电平,实现与1 pps上升沿不同位置的比较,达到对1 pps时延控制的目的,最后整形驱动后输出。该方法即实现了1 pps的时延控制,又保证了1 pps的信号质量[13-14]。

图5 秒脉冲信号时延控制设计原理

3.1 RC充电时间计算

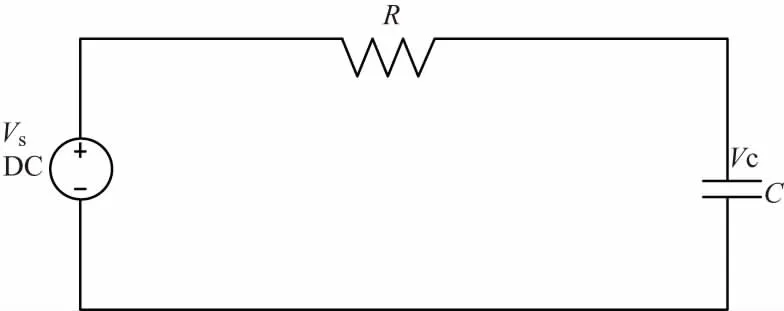

RC充电电路如图6所示。

图6 RC充电电路

直流电源Vs通过电阻R给电容C充电,假设电容C上瞬时电压为Vc,初始电压为V0,则电容的瞬时电压[15]:

Vc=V0+(Vs-V0)*[1-e-t/Rc]。

(3)

如果电容的初始电压值为0,则电容的瞬时电压可简化为:

Vc=Vs*[1-e-t/Rc],

(4)

则充电时间为:

(5)

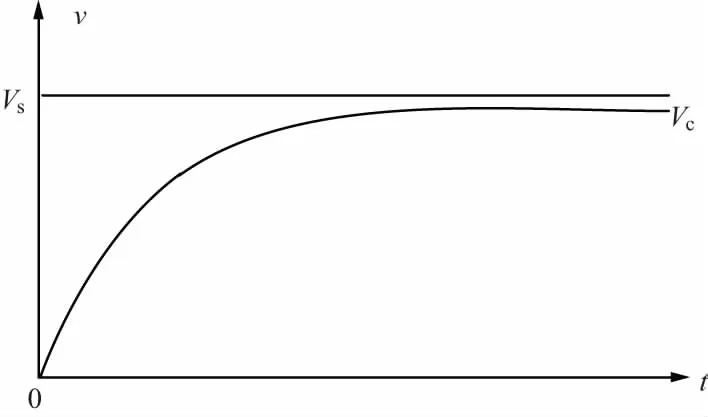

电容C两端电压随时间变化如7所示。

图7 电容C两端电压随时间变化

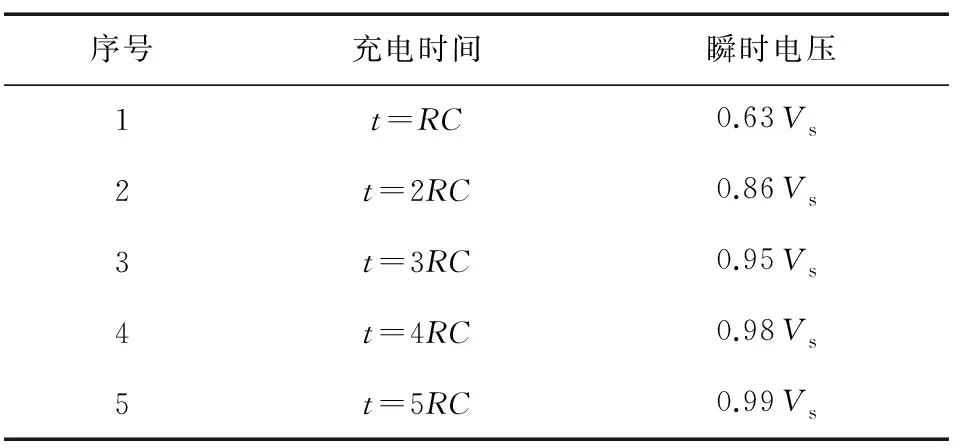

电容C上瞬时电压与充电时间关系如表1所示,经过3个RC后,充电过程基本结束。

表1电容C上瞬时电压与充电时间关系

序号充电时间瞬时电压1t=RC0.63Vs2t=2RC0.86Vs3t=3RC0.95Vs4t=4RC0.98Vs5t=5RC0.99Vs

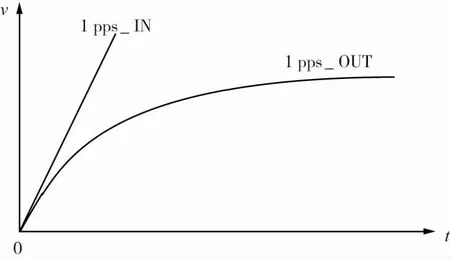

利用RC的充电原理,输入1 pps通过RC充电后其上升沿减缓,减缓时间t=3RC,选择不同的RC值,实现对输入1 pps上升沿的时延控制,其变化如图8所示。

图8 充放电前后1 pps信号上升沿变化

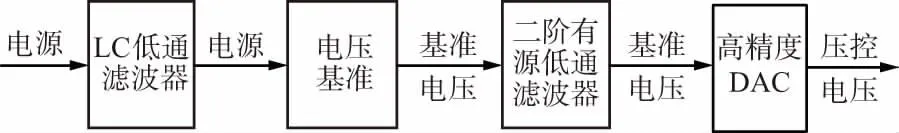

3.2 基于高精度DAC控制的秒脉冲信号时延控制电路设计

将上升沿减缓后的1 pps信号接入高速比较器,与高精度DAC输出电压值进行比较,控制DAC输出不同的电压值,与1 pps上升沿不同位置比较,实现对1 pps信号的时延控制。DAC控制电路如图9所示,1 pps时延调整电路如图10所示。

使用DAC控制1 pps输出时延,其输出电压分辨率影响1 pps时延调整分辨率、DAC输出精度影响1 pps时延控制精确、DAC输出电压的波动,造成比较电平出现波动,使得输出1 pps信号抖动增大,因此要合理选择DAC。

图9 DAC控制电路

图10 1 pps时延调整电路

DAC的输出电压计算公式如下:

(6)

式中,Vout为DAC输出电压;Vref为DAC的基准电压;D为DAC的控制量;N为DAC的分辨率。

由式(7)可知选择高精度DAC的同时还需选择高精度的电压基准。综合考虑以上因素选择12位的高精度DAC以及专用高稳电压基准,其输出分辨率达到0.001 V,控制精度±0.001 V。

4 实验结果分析

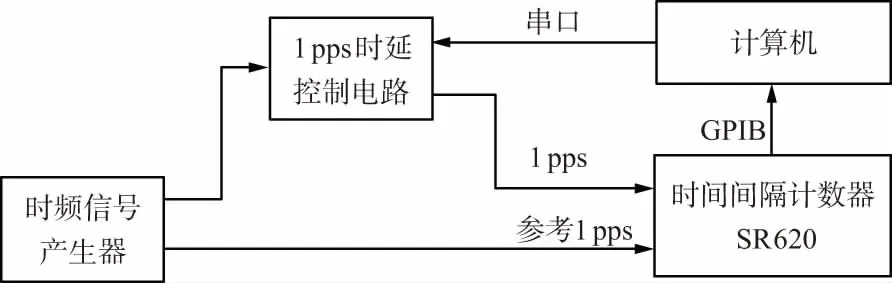

4.1 时延控制测试方法

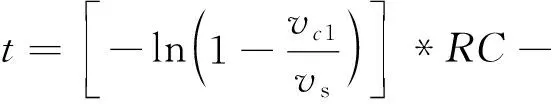

时延控制测试框图如11所示。时频信号产生器产生同源的2路1 pps信号,其中1路作为参考信号接入时间间隔计数器SR620的A通道,另1路通过时延控制电路接入SR620的B通道,使用SR620采集2路1 pps时差值[16],并通过GPIB总线上传至计算机[17]。通过计算机串口调整DAC输出电压值,分析1 pps时延变化。

图11 试验测试框图

时频信号产生器输出1 pps电平为TTL,考虑到1 pps信号低电平的抖动以及高电平的过冲,避免比较后出现干扰脉冲,设计控制电压范围1~4.1 V。电阻R取值100 Ω,电容C取值15 PF,不考虑输入1 pps上升时间,则时延控制范围:

4.2 时延控制测试数据

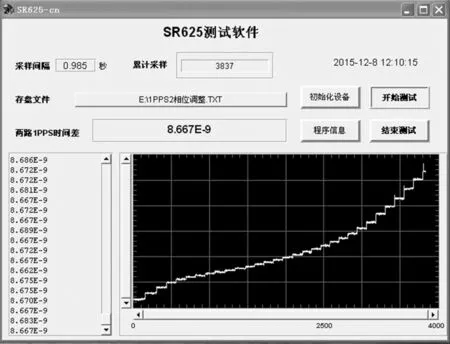

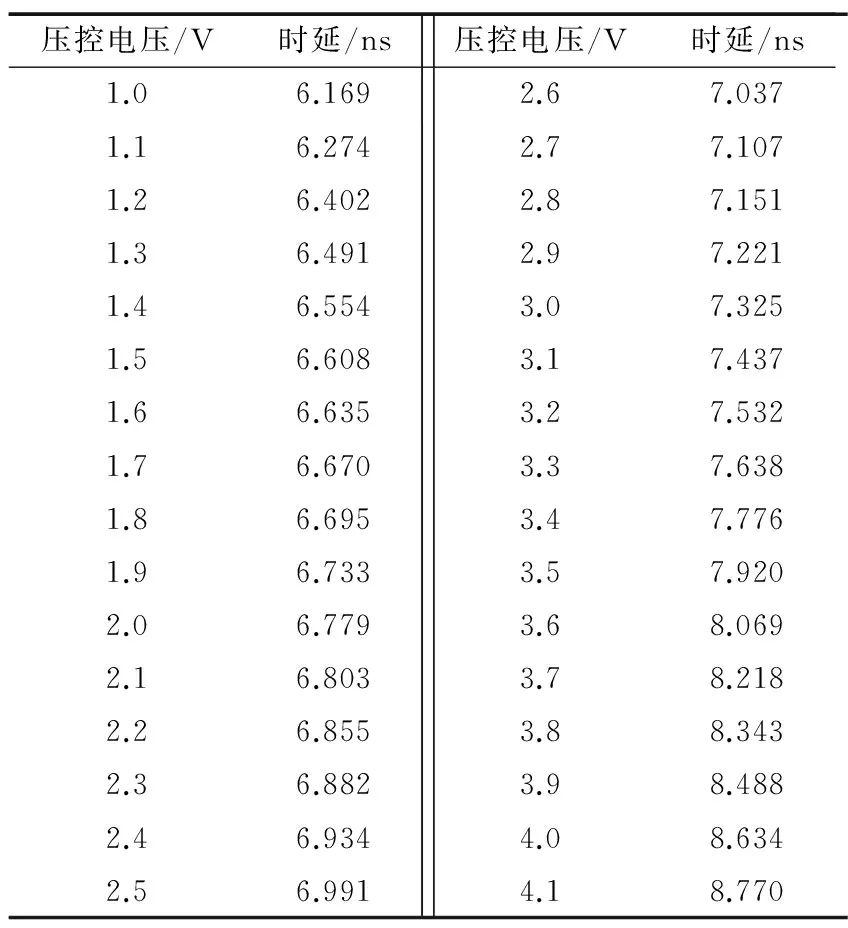

通过计算机串口控制DAC输出电压步进0.1 V,每个点记录100次求其平均值,记录电压在1~4.1 V变化范围下1 pps的时延调整曲线,试验结果如图12所示,符合对数函数曲线。

图12 1 pps时延调整试验结果

记录数据如表2所示,时延变化范围2.6 ns,最小变化5 ps,最大变化150 ps,减小DAC的电压步进值能够进一步提高相位调节分辨率。

表2时延控制测试数据

压控电压/V时延/ns1.06.1691.16.2741.26.4021.36.4911.46.5541.56.6081.66.6351.76.6701.86.6951.96.7332.06.7792.16.8032.26.8552.36.8822.46.9342.56.991压控电压/V时延/ns2.67.0372.77.1072.87.1512.97.2213.07.3253.17.4373.27.5323.37.6383.47.7763.57.9203.68.0693.78.2183.88.3433.98.4884.08.6344.18.770

5 结束语

本文分析了秒脉冲分配网络存在的问题,设计了基于高精度DAC控制的秒脉冲信号时延控制,解决了由于更换设备而造成秒脉冲分配网络末节点相位变化的问题。当前设计的秒脉冲信号时延调整方法需要测量设备辅助,根据测量结果调整1 pps时延达到精确控制的目的,在今后的工程设计中考虑使用微控制器拟合RC充电的时间曲线,达到自动调节的目的。