通用总线转换桥IP核的设计与实现

2018-07-11徐光辉刘文佳

徐光辉,刘文佳

(上海航天电子技术研究所,上海 201109)

0 引言

本文采用将所有子系统模块的总线数据全部集合到基于FPGA实现的总线转换桥模块。通过在模块内部对数据进行控制和管理,解决各个子系统模块中数据交换问题,避免传统方法中效率低下的缺点。

1 总线转换桥的架构

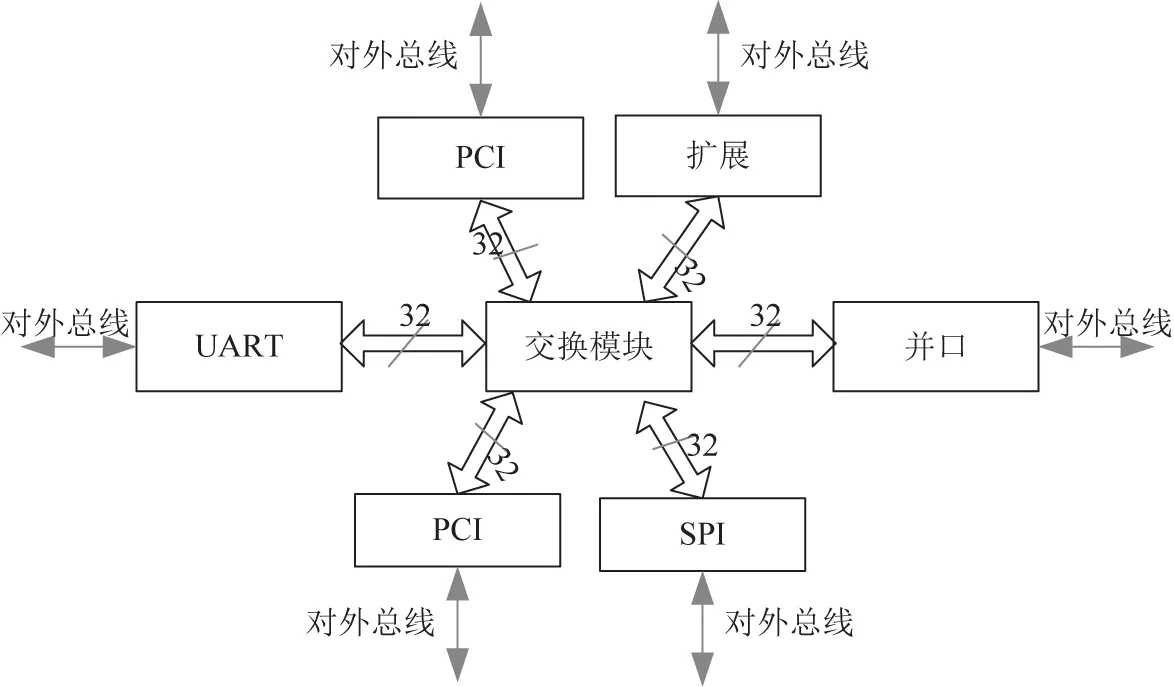

各系统间的总线转换效率直接影响整个雷达系统的性能,本文设计的总线转换桥IP核的结构如图1所示,它在外围实现所需总线接口功能,利用FPGA的可编程的特点及并行运行的特点,所有的外部总线设备都能同时进行数据的发送和接收,所有的数据在交换模块里面实现数据的交换,随后分发到对应的总线模块上。

图1 总线转换桥结构

2 设计与实现

2.1 交换模块

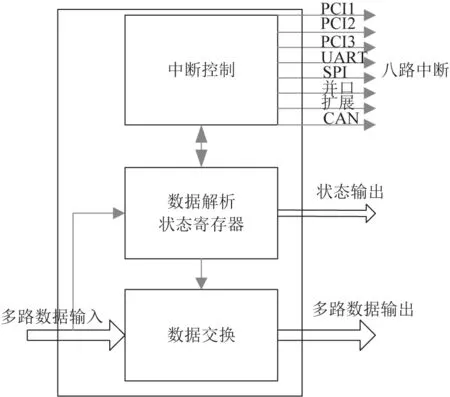

交换模块是总线交换桥的核心模块,它的效率直接影响系统的运行。本文所设计转换桥的交换模块可以将数据交换到各个目的总线上,交换模块的结构图如图2所示,但是需要用户遵循固定的数据封装格式。

图2 交换模块的结构图

图2是交换模块的结构图,其中数据交换单元负责将所有通路上的数据传送到对应的FIFO存储上,以便目的设备来读取相应的数据。中断控制单元的八路中断分别连接到六个总线外设上,当任何一个总线设备需要给其他设备发送数据时必须先产生中断通知目的设备。目的设备根据状态输出来识别时哪个设备需要发送数据,然后向该设备申请读数。数据解析状态寄存器决定该数据的目的地。

2.2 UART模块

通用异步收发器是一种异步串行通信总线,通信的发送方和接收方各自有独立的时钟,传输速度由双方约定。

该串口模块主要由接收中断和串口中断实现数据的收发。接收FIFO和接收控制共同组成接收逻辑,功能主要是从转换桥模块接收32位的数据,通过产生接收中断将分解后8位数据传送到OS中,随后OS将数据发送到串口设备上。发送FIFO和发生控制组成发送逻辑单元,OS接收到出口中断后,读取串口设备的8位数据,并发送请求给发送逻辑。发送逻辑将数据打包成32位数据传送到转换桥模块。

2.3 SPI模块

转换桥中SPI模块用来控制CAN总线数据收发。初始化配置和控制,数据管理模块负责CAN总线上数据的解包打包处理,然后分发到控制模块或者外围的CAN节点上。

发送逻辑的功能主要是从总线转换桥的控制模块上接收32位的数据,然后存储到接收FIFO上,由于一个CAN标准帧需要3个32位的数据字组成,因此数据管理连续读取3次FIFO的数据组成一个标准帧。同样接收逻辑的功能主要是从CAN总线上接收完整的一个标准帧,然后在数据管理里面对进行解包取出有效数据,将其拆分成32位存储到接收FIFO里面。

数据管理主要集中在控制逻辑的设计上,本文采用oneshot编码的有限状态机作为控制,分别定义了9个工作状态。

SPI模块的控制状态机开始处于Idle状态,根据不同条件状态机转移到其他状态,状态机转换条件有不同优先级,复位具有最高优先级。

(1)当收到复位信号时,状态机跳转到Initial状态,此状态进行初始化操作。

(2)当收到数据时进入RX_state状态,此状态时处理接收到的标准帧数据,并将其发送到数据管理模块。

(3)当需要发送数据时进入Read_State状态,此状态时先读取三个发送缓冲区的当前状态,当至少存在一个空闲的发送缓冲区时从数据管理模块读取封装好的标准帧数据,并且将标准帧通过并串转换模块发送。

2.4 PCI模块

本文将PCI模块划分为三个设备,PCI模块的结构图如图3所示。三个设备都有各自的初始化功能和数据处理功能,因此VxWorks会设别到三个中断源:中断A、中断B和中断C。在本设计模块中,VxWork分别给三个模块分配了5、10和12号中断。

图3 PCI模块的结构图

初始化功能主要是设置子设备的设备号、分类号和设备商信息,向系统申请空间大小等。当以上的信息设置成功之后,操作系统设别到该唯一性设备,并能对其进控制与数据收发。

数据处理功能主要就是处理PCI总线的数据,负责将接收的32位数据发送总线上或者将总线上属于自己的数据取出并发送到指定外围设备。

3 总结

基于雷达系统的实际需求,本文设计了一种总线转换IP核的结构,它能够很好的满足使用不同总线的模块间交换数据,实际结果表明该设计能高效、可靠的完成该型号雷达系统的模块间的数据交换,简化了雷达系统中的分系统的复杂性。另外将其封装成IP核后,可以直接应用到其它的工程中,加快工程的开发进度。