超深亚微米导航SoC芯片的低功耗策略

2018-07-10张文华

张文华

(中国电子科技集团公司第二十研究所,西安 710068)

0 引言

随着导航产业的不断发展,导航SoC芯片的设计实现逐渐成为导航技术的核心之一[1]。随着集成电路设计工艺尺寸的不断减小、芯片功能的不断复杂,运算量的不断增加和工作频率的不断提高,SoC芯片的功耗急剧增加,功率密度及散热问题成为影响芯片性能的主要因素,主要体现以下几个方面:

·可靠性问题

功耗的增加会带来芯片温度的升高,对可靠性会带来很大影响[2]。随着温度的升高,金属的电迁移现象会越来越严重,甚至带来短路或断路问题;芯片温度的升高还会带来供电网络的电压降问题,影响电路性能;芯片的寄生效应也会随着温度的升高而加重,电路时钟偏差、时序问题也会变得严重,甚至引起电路功能的错误;温度升高还会增加系统的噪声,从而降低系统的噪声容限。

·散热问题

芯片正常工作时会产生大量热量,必须采用有效的散热措施,否则芯片温度会迅速增加,从而烧毁芯片甚至影响电子系统的应用。一般情况下,可以在封装过程中通过一些设计手段实现散热,陶封器件比塑封器件散热好一些,但是带来的成本增加非常可观。

·设备需求

目前便携式电子设备的使用都依赖于电池供电,而电池的发展速度还远不能满足系统功能的增加和芯片功耗的增长,为了尽可能增加电池的耐久性,改善使用体验,必须寻找有效的低功耗设计方法和技术。

·环境保护问题

功耗问题归根结底是能源问题和环境问题,探索芯片设计中有效的低功耗设计策略,能够提高电子系统的能源利用率,有利于环境保护。

1 功耗组成分析

导航SoC芯片的功耗可分为处理器功耗、通讯功耗和存储器功耗,一般将处理器功耗和通讯功耗归并为逻辑功耗。逻辑功耗由动态功耗和静态功耗组成,动态功耗主要包含开关功耗和短路功耗,开关功耗是指对负载电容充放电引起的功耗,短路功耗是指在信号翻转过程中n管和p管同时导通时的短路电流引起的功耗。静态功耗是由泄漏电流引起的功耗,泄露电流主要由4部分构成:亚阈值沟道泄露电流Isub、栅极隧穿效应电流Igate、有源区寄生二极管反偏漏电流Idiode、稳定状态时的偏置电流及比例电路(比例电流源偏置)电流Idc。

随着特征尺寸的不断缩小,集成电路的功耗分布有极大的变化,在0.18μm及以上的CMOS工艺中,开关功耗为芯片的主要功耗,约占总功耗的70%~90%,在40nm CMOS工艺下,静态功耗占芯片整体功耗的比例已达到50%。

1.1 动态功耗

(1)开关功耗

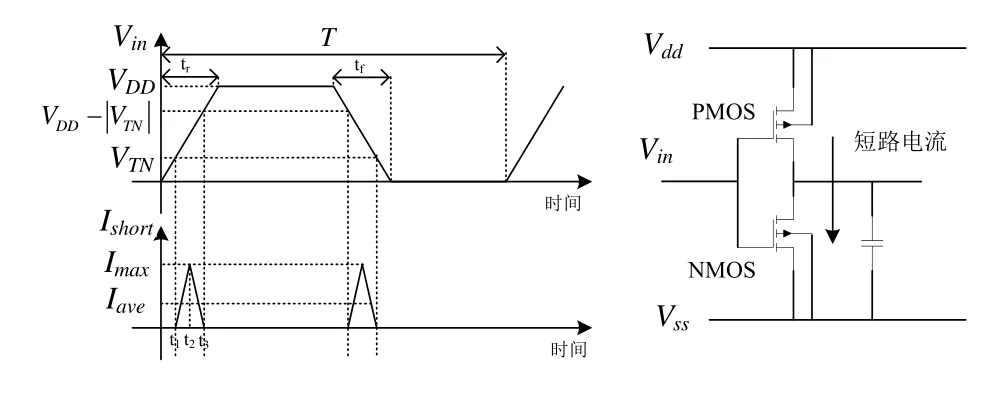

当输入信号 Vin为理想信号,即上升下降时间为0时,随着输入信号的跳变,负载电容的充放电过程会产生开关功耗,如图1所示。

图1 开关功耗示意图

按照实际工作情况引入开关活动性α,表示器件在每个周期开关的可能性。在一个周期T内,开关功耗可表达为:

由式(1)可知,当工作频率一定时,影响开关功耗的主要因素为供电电压VDD,负载电容C及开关活动性α。

·供电电压VDD

由式(1)可知,供电电压对开关功耗影响最大,但供电电压的降低会影响器件的翻转速率,限制最大工作频率,降低电路噪声容限,导致电路性能的下降。

·负载电容C

动态功耗本质上为电路中各节点电容在电平变化过程中充放电引起的功耗。负载电容的大小跟开关功耗成正比例关系。在高跳变率的线网上使用面积更小的标准单元以降低节点电容,走线尽可能短,并使用寄生参数较小的低层金属是降低开关功耗的有效措施。

·开关活动性α

RTL编码设计完成后,开关活动性已经确定,一般由逻辑综合工具对仿真波形通过统计的方法提取出来,在功耗预估中,信号线的开关活动性典型值为0.2,时钟的开关活动性为1。

(2)短路功耗

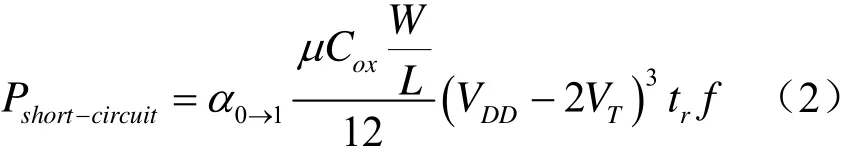

在实际工作中,输入信号并不是理想阶跃波形,从1到0和从0到1的跳变都需要消耗一定的时间,在跳变过程中,存在n管和p管同时导通的情况,在电源和地之间会形成瞬态短路电流,如图2所示。

图2 短路功耗示意图

为了简化分析,设tr=tf,则短路功耗可表达为:

由式(2)可知,工艺参数、晶体管尺寸、供电电压、输入信号的上升下降时间为影响短路功耗的主要因素。在芯片设计中,可通过重组大扇出逻辑门结构、调整逻辑门尺寸使得输入输出波形匹配,以减少p管和n管同时导通的时间;在组合逻辑中,静态电路的毛刺是造成短路功耗的主要原因,通过在跳变频率较高的信号线上加寄存器可阻止毛刺的产生及传递;在电路中尽量保证信号线网的平衡,减少相互等待。

1.2 静态功耗

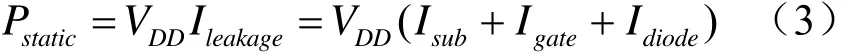

静态功耗主要由泄漏电流引起,泄漏电流包括亚阈值沟道泄露电流Isub、栅极隧穿电流Igate、有源区寄生二极管反偏漏电流Idiode、稳定状态时的偏置电流及比例电路(比例电流源偏置)电流Idc。其中偏置电流Idc存在于模拟电路中,在SoC设计中,模拟电路一般以硬核IP的形式直接应用,偏置电流为其固定参数,此文不做讨论。因此,泄漏电流示意如图3所示。

图3 静态功耗示意图

静态功耗可表达为:

·亚阈值漏电流Isub

亚阈值泄露电流是无跳变状态下源级和漏极之间的电流。随着特征尺寸的不断减小,供电电压会持续降低,亚阈值漏电流会急剧增加。

·栅极漏电流Igate

栅极漏电流是无跳变状态下由晶体管栅极与衬底之间的载流子隧穿效应引起的漏电流。随着特征尺寸的不断减小,栅极漏电流随着栅极氧化物厚度的减小急剧增大,目前一般通过采用高k介质来减小越来越严重的栅极漏电流。

·源/漏极反偏漏电流Idiode

源/漏极反偏漏电流是无跳变状态下源/漏极各自的pn结上有强大的电场时形成的漏电流。

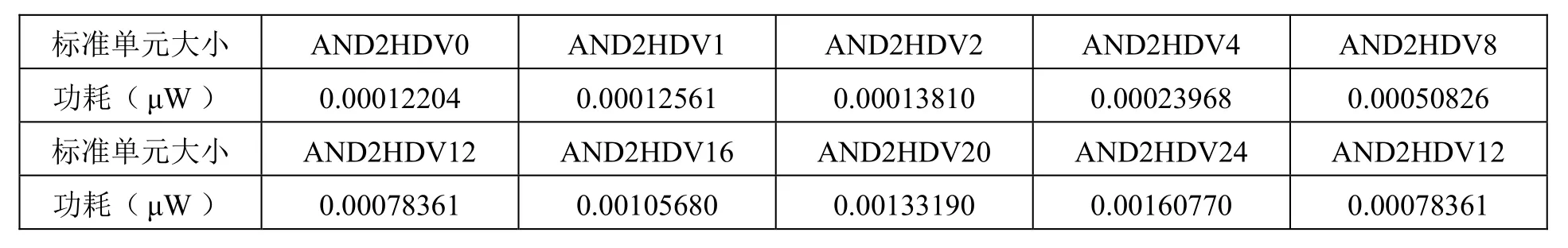

在稳定工作状态,只要为芯片供电,泄露电流就一直存在。当芯片的设计工艺确定后,静态功耗一般采用查找表的方法,可以建立与其输入状态、温度、沟道长度等参数相关的静态功耗多维表格。以SMIC 65 nm为例,不同尺寸的二输入与门功耗如表1所示[3]。

表1 二输入与门静态功耗查找表

1.3 存储器功耗

在SoC芯片的设计中,往往需要频繁读写存储器,存储系统功耗日益增加,现在已成为SoC芯片功耗的重要组成部分,存储器功耗主要包括:(1)程序和数据存储器访问相关的功耗;(2)存储器单元内部的功耗。在当前微处理器结构中,存储器系统的功耗比重可能高达40%[3],因此对存储器系统的功耗的优化非常重要。

目前 SoC芯片中主要有两种存储单元的实现方式,一种是通过MemoryCompiler自动生成能够满足不同容量、速度和尺寸要求的存储器模块,内嵌于SoC芯片中;一种是将存储器裸芯通过SiP形式与SoC芯片封装进同一个外壳中,以一个整体实现SoC芯片功能,不论哪种形式,存储器模块确定以后,其自身功耗是固定的,一般只能从系统架构级对功耗进行优化。

2 低功耗技术

2.1 低功耗设计方法概述

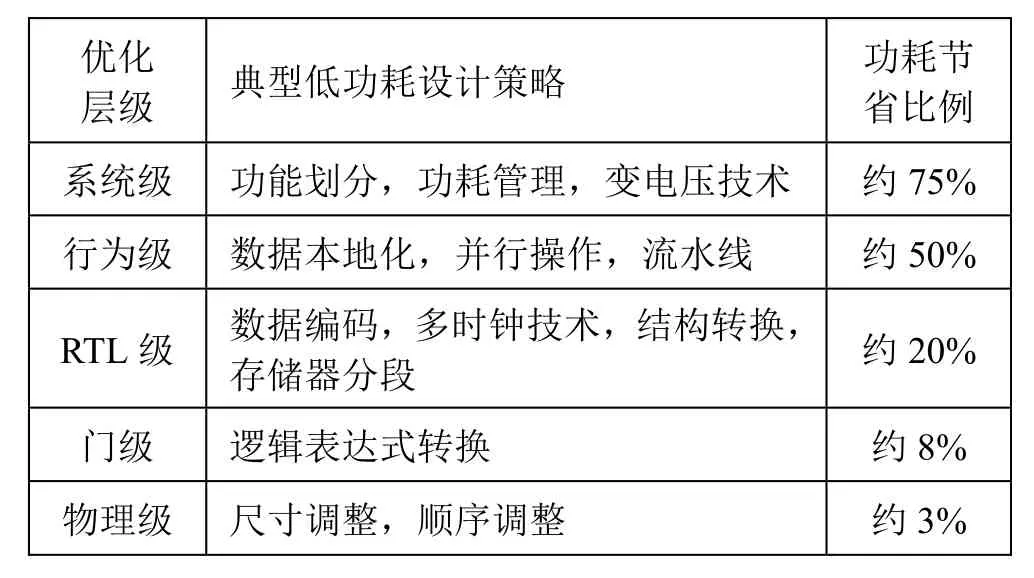

在SoC设计中,性能、功耗和面积是相互联系和制约的主要因素,需要在整个设计过程中进行不断的迭代和折中。在系统级、行为级、RTL级、门级和物理级等各个设计层次上,可以采用多种低功耗设计策略,主要如表所示。

设计层次越高的优化策略对功耗的优化效果越明显。系统级优化包括软硬件协同设计、存储器系统的多级cache划分、外存备份、算法优化及协同综合等方法。行为级优化包括优化流水线级数、最小化指令集、并行操作和优化流水线结构、高频时钟由内部PLL产生、电源管理等方法和存储器架构划分等方法。RTL级优化包括降低器件数量、操作数隔离等技术。门级优化包括简化逻辑和映射电路、利用反相器进行时钟树综合等方法、尽可能使用静态逻辑器件、尽量减少活动性高的信号经过的标准单元数量等方法。物理级优化包括扇出的优化、晶体管大小调整、分块时钟树和毛刺消除等方法。

表2 典型低功耗设计策略

2.2 SoC芯片中低功耗设计手段

根据第1节的分析可知,芯片的功耗与工作电压、开关频率和负载电容等因素密切相关,要降低芯片功耗,就必须找到合理的低功耗设计技术来减小这些因素的影响。

(1)存储器(系统级)

常见的存储系统低功耗策略是从系统架构设计层面上尽可能减少存储器需求,从算法上尽可能减少存储器的访问次数。另一种有效方法是通过多级cache来实现存储系统的层次化,并将存储系统划分成多个子存储模块,有选择的使能各子模块,对各子模块应用适当的功耗管理策略,消除或降低处于闲置状态的存储模块的功耗[4]。但是这种方法需要增加额外的译码逻辑电路,在减少功耗的同时增加了芯片面积,同时后端版图设计需面对大量小存储器模块,增加了布局和时序收敛难度,增加了可观的工作量。

(2)门控电压(行为级)

当芯片的某些模块不工作时,可以切断其电源,当这些模块又要恢复工作时,再恢复其供电,这种降低功耗的方法叫做门控电压技术[5]。门控电压技术大幅减小了模块漏电流和晶体管的开关活动,可以有效的降低芯片整体的功耗。但同时也带来了一些新的设计挑战,包括电源控制模块、门控电源网络、隔离单元、保持寄存器等单元的设计。

电源控制模块是一个用来控制指定模块电源的关断和打开的逻辑电路,需要精确控制其关断和打开时间;门控电源网络是由大量源漏连接的晶体管组成,其作为电源开关摆放在常开电源轨和受门控的器件单元之间,当开关打开的时候,供电电源被连接到模块中各个逻辑单元上,当开关关断的时候,各个逻辑单元的供电电源被有效的切断;隔离单元用于在切断模块电源后保持一个已知的、稳定的输出,以保证后续逻辑的正确与稳定;快速恢复断电前状态的方法是可以采用保持寄存器,但保持寄存器比普通寄存器占据更大的面积,且其中的影子寄存器需要常开电源供电,增加了电源网络的复杂性,另一种办法是在电源关断前将模块寄存器中的数据复制到模块外部的存储器中,当唤醒的时候再复制回来,但是需要一定的恢复时间。

门控电源技术可以结合多电压域设计,不同功能的模块可以设计成不同的工作电压并且在不工作的时候切断其的电源,灵活的供电策略可以大大减小整颗芯片的功耗。

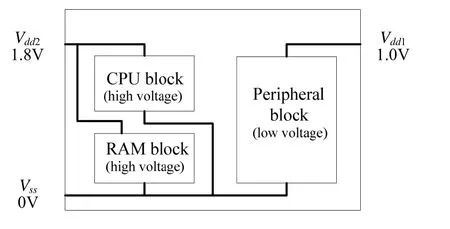

(3)多电压(RTL级)

按照第一章的分析,功耗和电压的平方成比例关系,如果供电电压降低50%,功耗会降低75%,在 CMOS电路中动态功耗和静态功耗的总和也基本可以达到这样的降低幅度,因此,降低功耗最有效方法便是降低整个电路的供电电压。

SoC芯片中不同的模块可能会有不同的速度要求,例如,CPU单元和RAM单元一般会比外设单元工作在一个更快的频率上。供电电压的降低可以有效减少功耗,但是会增加标准单元传输延迟,限制工作频率。因此,在RTL设计阶段,会为CPU和RAM分配较高的工作电压,而对工作频率较低的模块分配较小的供电电压,在保证芯片性能要求的基础上尽量减小功耗,如图4所示。

图4 SoC芯片多电压分布示意图

(4)门控时钟(门级)

在SoC芯片设计中,当寄存器在很长时间内数据不发生变化时,可通过切断其时钟输入来避免寄存器的数据翻转和刷新,尽量减少不必要的信号翻转,将此段时间内相应寄存器的动态功耗理论上减小到0。

门控时钟是一种成熟的低功耗设计方法[6],一般的通过标准单元库中提供的带门控寄存器来实现。通过综合工具PowerCompiler自动找出长时间内数据不发生变化的数据路径,并在该路径的时钟网络中合理的位置插入时钟门控单元,减少不必要的时钟信号翻转,并在逻辑综合中选用门控时钟寄存器来替换普通寄存器。门控时钟对于那些需要在很多时钟周期保持相同的数据的寄存器上应用十分有效。关断时钟的输入会杜绝那些不必要的开关活动,否则寄存器在每次时钟到来的时候都要重新载入一遍数据,造成无谓的电流消耗。门控时钟属于门级低功耗设计方法,不需要增加额外的电源网络设计,也不必对RTL编码进行修改。

(5)多阈值电压工艺(物理级)

0.13μm及以下的CMOS工艺都支持不同阈值电压的晶体管,在这种工艺下,一个标准单元库可以提供两种或三种不同阈值电压的标准单元,在综合和布局布线时根据逻辑时序的需要放在不同的位置。例如,一个标准单元库可以提供两种反相器:一种由低阈值电压的晶体管组成,另一种用高阈值电压的晶体管。低阈值电压的单元有着更高的速度,但同时存在更大的亚阈值漏电流,静态功耗可观。高阈值电压的单元有更小的亚阈值电流,但是速度却变差。在物理设计实现中,可在满足性能及速度要求的基础上,通过功耗优化命令在时序裕量较大的路径上将低阈值器件或者标准阈值器件替换为高阈值器件[7],达到降低功耗的目的。具体命令为:setOptMode-efforthigh optLeakagePower

3 结束语

在超深亚微米导航SoC芯片设计中,功耗是制约芯片工作频率、影响芯片功能的主要因素之一。本文在分析SoC芯片功耗重要性的基础上,详细研究了SoC芯片中动态功耗、静态功耗和存储器功耗的基本原理,对供电电压、信号跳变率、工艺参数等影响功功耗的主要因素做了分析和讨论。最后,分别从系统级、行为级、RTL级、门级和物理级提出了各自有效的低功耗设计策略。