基于Linux操作系统下TDC电路的数据处理研究

2018-06-14赵建军

余 进,赵建军,刘 立,赵 恩

(昆明理工大学理学院,云南 昆明 650500)

0 引言

随着信息技术的发展,时间精度越来越高,卫星通信、车载设备、无线传感网络的不断发展,对于时间的精度越来越高。脉冲星因具有很好的稳定性,其发射的X射线信号可以作为天然信标,引导航天器等在宇宙中的自由航行。时间测量电路是 X射线脉冲星导航的重要组成部分,通过采集到的 X射线脉冲作为触发信号获取此时刻的时间,该时间精度达到皮秒级。

本文的数据处理电路是基于中国科学院西安光机所的X射线脉冲星导航的合作项目,最后的测试阶段均在西安光机所完成。时间测量电路是X射线脉冲星导航后端电路的重要部分,前端电路由西安光机所研发。现阶段的所有研究全是基于地面模拟系统上进行的。本文的基于Linux系统下的TDC电路的数据处理对于细时间的精度具有较好的效果,有一定的创新性。

1 系统简介

时间数字转换技术,又称时间数字转换器(Time-to-Digital Converters,简称 TDC)技术,TDC技术广泛的应用于时频测量、航空航天、卫星导航、雷达定位、激光测距、核物理和粒子物理探测等领域,并且这些领域的先进水平与时间间隔测量的精度密切相关。我国对脉冲星的研究滞后于国外,在早期的研究,国内团队主要集中于对脉冲星的计时观测,国家对该领域的投入很大,也取得了一些瞩目的成就,在X射线探测成果卓著[1-3]。X射线脉冲星导航系统国内外都还处于地面模拟阶段,并没有真正的应用于航天测试阶段。中科院有一整套的地面模拟系统,本文的研究是在中科院西光所的地面模拟系统下对BO531CRAB星座的X射线仿真源模拟上进行的。ZedBoard开发板是近年Xilinx公司推出的产品。该开发板采用Xilinx 7系列芯片,等级速度为-1。ZedBoard具有2个ARM-9的硬核,用户可以单独对 FPGA 进行设计,也可以与 ARM进行协同设计[4]。本文的硬件电路基础为 Xilinx公司的Zynq-7000系列的ZedBoard开发板,此开发板集成了FPGA和ARM-9两种技术,使得设计系统可以利用FPGA技术实现TDC硬件电路对数据高精度的采集。在嵌入式 Linux系统的控制下,以中断的方式通过AXI总线进行可靠的数据传输,利用硬件实现历元叠加和数据的整合,从而实现对TOA数据的计算。其原理设计如图1所示。

图1 X 射线拼接探测时间测量电路构成Fig.1 X-ray splice detection time measurement circuit composition

2 基于SOPC的嵌入式Linux系统

基于SOPC技术的嵌入式系统设计方案主要有两种:一种是基于FPGA的嵌入式硬核微处理器方案;另一种是基于FPGA的嵌入式软核微处理器方案[5]。用户在使用软核处理器时,可以根据系统设计的具体要求,对软核处理器的外围设备进行搭建,使整个嵌入式系统在硬件结构、功能、资源等使用方面符合设计要求。软核 IP大部分由 FPGA公司自行开发与设计,软核具有的特点是灵活性高、可移植性强、允许用户自行配置。但是软核IP又存在不足,软核没有硬核性能稳定,处理速度比硬核慢,模块的预测性较低。基于FPGA的嵌入硬核IP的微处理方案,利用IP核植入技术在FPGA中预先植入嵌入式硬核处理器。通过FPGA芯片中的逻辑资源和嵌入式开发工具提供的外围设备IP软核,构建以硬核处理器为系统核心的片内外设和接口。硬核处理器构建的嵌入式系统具有很强的数据处理能力,且硬核处理器本身并不占用FPGA资源。利用嵌入硬核处理器的FPGA器件构建的嵌入式SOPC系统具有较强的稳定性和更快的处理能力,弥补了软核微处理在稳定性和处理速度的不足。利用Xilinx公司的Virtex-II Pro系列的FPGA芯片中植入的ARM-9双硬核微处理器,一方面可以利用可编程器件FPGA其在硬件电路上设计方便的强大优势,另一方面可以充分利用微处理器在数据处理方面灵活的特点,使得嵌入式系统设计在数据采集与处理部分可以实现高效的SOPC系统,系统框架如图2所示。

图2 嵌入式系统设计框架Fig.2 Embedded system design framework

Linux操作系统的移植目的是可以在 ZedBoard开发板ARM处理器上运行Linux操作系统。Linux系统移植可以分为以下过程:

①为了实现跨平台的编译环境搭建,需要安装针对 ARM 的交叉编译工具链。所谓交叉编译工具链就是基于不同的硬件平台需要不同的编译工具集[6]。

②通过交叉编译工具链编译Linux内核,同时可以对内核进行裁剪达到节省资源的目的。

③制作引导内核的U-Boot启动文件。

④建立Linux系统下完整的文件系统。

⑤建立device tree来管理系统硬件资源。

3 硬件系统的搭建

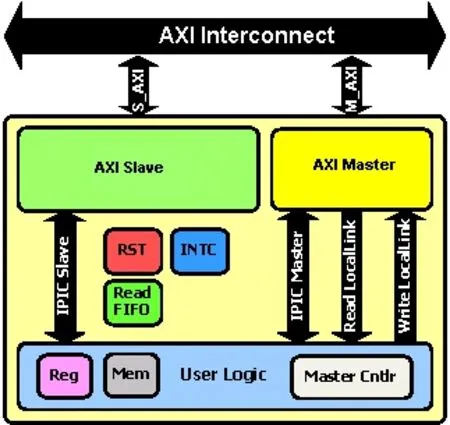

采用Xilinx公司的Design Tools开发套件来进行硬件系统的搭建,目的是实现TDC硬件电路模块和ARM的通信。两者之间通信的桥梁是AXI总线,AXI总线是ARM处理器的总线结构,AXI总线结构如图3。AXI总线采用的是FPGA技术,可以利用网表、例化等方式实现TDC在总线上的挂载。添加三个寄存器实现对TDC电路的控制和读取数据操作。

图3 ARM 处理器的AXI总线结构Fig.3 AXI bus architecture of ARM processor

对时间测量还需要解决垮时钟域的问题。一般同步不同时钟域间的数据传输有两种方法:一是在不同时钟域之间采用握手机制,二是异步FIFO[7]。本文是采用第二种方法,加入了 FIFO缓存单元实现传输速率的匹配。利用 FPGA技术设计的 FIFO数据的存入设计状态图如图4所示。

图4 FIFO 数据的存入设计状态图Fig.4 Storage design state diagram of FIFO data

(1)ini状态:TDC电路模块初始化以及系统复位。

(2)S1状态:TDC数据输出端口dout数据锁存,等待操作系统对端口的数据进行读取。

(3)S2状态:操作系统读取一次TDC输出端口的数据结束状态。

当操作系统通过AXI总线读取一次 TDC的测量结果结束时,S2状态机进入复位状态或者进入S1状态。TDC电路模块通过 TDC控制器中的状态机S1状态与S2状态的交替执行,实现了操作系统对TDC测量结果的正确读取。

4 数据采集模块TDC的设计

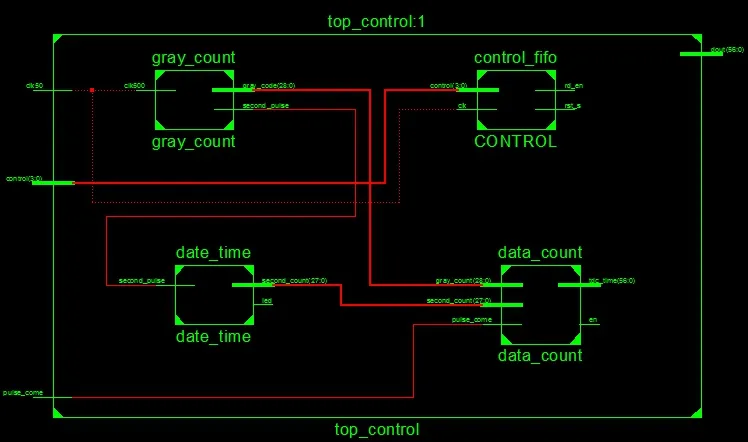

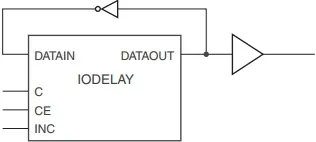

对于时间的测量是高能物理实验中的一个重要测量参数。目前,对于时间测量的方法主要有两种:一是采用专用的时间测量芯片(ASIC TDC);二是采用基于FPGA的时间数字转换电路。专用的时间测量芯片大多都是针对具体的应用而开发的,对于设计的灵活性,普遍性存在一定的不足[8]。本文采用FPGA技术利用Xilinx公司的Zynq-700系列芯片XC7Z020,封装为 CLG484,设计时间测量电路TDC。TDC电路的设计分为粗时间和细时间相结合的测量方法,秒以上的时间计数为粗时间计数,秒以下的时间计数为细时间计数。粗时间采用对主频的计数的方法,为秒、分、时、日,月、年计数,如表1所示。在主频以下的细时间部分分为两部分来计量,一部分通过倍频技术进行精度纳秒级的计数,另一部分通过延迟78 ps的IODELAY延迟单元模块(如图6)进行精度皮秒级的计数。同时TDC电路的设计采用格雷码计数的方式。使得该时间测量电路系统的设计具有精度高,成本低,应用领域广泛等特点。为了保持计数同步,需要设计有记忆功能的寄存器传输级(RTL)电路,其电路图如图5所示。数据采集模块TDC的设计有如下三个部分。

表1 TDC 电路的数据格式表Tab.1 Data format table of TDC circuit

图5 TDC 电路的RTL图Fig.5 RTL diagram of TDC circuit

4.1 IODELA Y的设计

延迟78 ps的设计:

module ABC ( clk200,d0 );

input clk200;

output d0;

IDELAY #(

.IOBDELAY_TYPE("FIXED"), // "FIXED" or"VARIABLE"

.IOBDELAY_VALUE(1) // Any value from 0 to 31 //0为主频同步不延迟,1为最小的时钟延迟:78 ps

以此可以计算出1 s时的延迟参数为:1000/78=12,为 1000 MHz,XC7Z020芯片的最大的数值为31个,具体可以在综合仿真布线之后的FPGA Editor查看器件布局布线。但不能超过开发板的最大频率。

图6 IODELA Y延迟单元模块Fig.6 IODELAY delay unit module

4.2 倍频的设计

将主频50 MHz主频时钟通过倍频技术提高到500 MHz,精度达到2 ns,倍频采用Clocking Wizard 3.5的IP核,Input Jitter设置为0。当2 ns的时钟周期记数到 1 s时,作为粗时间的时钟计数单元。而2ns到1 s的计数方式采用格雷码计数。

4.3 格雷码计数

格雷码是一种无权码,其编码特点是任意两相邻代码间只有一位数码不同,这对代码的转换和传输很有利,因为它大大减少由一个状态到下一个状态时电路中的模糊状态,提高了电路的抗干扰能力,所以格雷码是一种错误最小化的编码。格雷码计数一类是用于定时,另一类是用来计数,用在脉冲沿的计数或地址的判断,如判断 FIFO传输来的数据量是否足够或者 FIFO的读/写地址是否已经达到满状态,来决定下一步动作[9-10]。采用格雷码计数运用在模块状态机的方案设计上设计方案,可以很好的减小误差,达到错误最小化。

5 数据处理部分硬件电路模块

由于脉冲星周期的极端稳定性,脉冲星可作为一个天然时钟[11]。数据采集前端TDC模块对于脉冲星 X射线采集的数据需要经过大量的光子数据累计,才能还原出脉冲星的脉冲轮廓。对脉冲轮廓还原一般方法是利用软件实现,可将数据传入上位机利用 MATLAB来实现[12]。但此种方法造成了资源浪费且无法做到小型化实时性,更无法用于航天器。在此基础之上提出,开发 Linux操作系统下的应用程序来处理TDC的数据,此方法提高了系统应用的灵活性节能性可以做到设备处理数据的小型化实时化,但考虑到数据处理效率的问题之后,得出了一种更加优化的设计方法,对于数据处理的方式采用硬件电路实现的方法。将此硬件系统挂载到 Linux系统下,通过Linux的控制,将TDC电路模块的数据传到数据处理模块,对数据进行历元叠加,经过历元叠加后得到的数据(TOA),以提供给后端模块进行导航。

6 结语

本文基于X射线拼接探测时间测量电路的研制课题背景,针对TDC电路的测量提出了基于Linux系统下任意格式的数据处理与文件生成。此设计提高了时间测量的实时性以及设备的小型化,在航空航天、卫星导航、工业控制、智能家居、环境监测等领域具有很好的应用前景和实用价值。

[1] 张敏. 皮秒分辨率的FPGA-TDC技术研究[D]. 西安: 西安电子科技大学, 2013.

[2] 侯天蕊. 脉冲星信号特征识别与处理[D]. 哈尔滨: 哈尔滨工业大学, 2014.

[3] 赵恩. 基于ZedBoard开发板的Linux OS下的X射线高精度TDC系统的研究[D]. 昆明: 昆明理工大学, 2017.

[4] 陆佳华, 潘祖龙, 彭竞宇, 等. 嵌入式系统软硬件协同设计实战指南[M]. 北京: 机械工业出版社, 2014. 27-37.

[5] 王伟. 基于FPGA的SOPC嵌入式系统设计[J]. 淮北职业技术学院学报, 2013, 12(1): 137-138.

[6] 唐海峰. 基于FPGA的时间测量电路的研究[D]. 昆明: 昆明理工大学, 2016.

[7] 于海, 樊晓桠. 基于FPGA异步FIFO的研究与实现[J]. 微电子学与计算机, 2007, 24(3): 210-216.

[8] 赵恩, 赵建军, 高霞芳, 等. 时间测量电路系统的设计[J].新技术新工艺, 2016, 9: 11-13.

[9] 叶卫东, 谢建华. 格雷码计数器的低功耗分析与设计[J].兵工自动化, 2006, 25(4): 64-66.

[10] 李莉. 基于FPGA的多位格雷码计数器[J]. 科学技术与工程, 2009, 9(23): 7158-7161.

[11] 刘琳. 脉冲星的积分轮廓的高斯拟合及谱指数的研究[D].重庆: 西南大学, 2011.

[12] 吴亚平, 赵建军, 吴光敏, 等. X射线脉冲星导航硬件脉冲轮廓累积研究[J]. 航空学报, 2016, 37(2): 662-668.