基于FPGA的相位测量仪

2018-05-30桂林电子科技大学信息科技学院桂邦豪

桂林电子科技大学信息科技学院 桂邦豪

1.引言

相位测量作为一种重要的信号检测技术,已广泛应用于电力、机械、航空航天、医疗、化工等各个领域,而其性能往往对所应用的系统起着重要的作用。目前,国内相位计生产厂家或研究单位明显存在着技术老化问题,其采用的器件、方法和技术与发达国家相比有较大的差距。同时,随着国防和科教等的发展又迫切需要高精度、高性能的相位计。

2.FPGA芯片介绍

本次设计采用杭州康芯电子有限公司生产的以Altera 公司生产的FPGA器件::Cyclone EP1C3T144C8N为主体的适配板作为数据采集电路硬件的核心,该适配板提供了一片集成度为15万门的EP1C3T144C8N,一个20MHz时钟,一个JATG下载模式,一个AS模式下载口,使用起来十分方便。其中它所提供的20MHz时钟可直接用来作为数据采集时所用的基准信号源。

Altera Cyclone FPGA是目前市场上性价比最优且价格最低的FPGA。Cyclone器件具有为大批量价格敏感应用优化的功能集,这些应用市场包括消费类、工业类、汽车业、计算机和通信类。器件基于成本优化的全铜1.5V SRAM工艺,容量从2910至20060个逻辑单元,具有多达294912bit嵌入RAM。Cyclone FPGA支持各种单端I/O标准如LVTTL、LVCMOS、PCI和SSTL-2/3,通过LVDS和RSDS标准提供多达129个通道的差分I/O支持。每个LVDS通道高达640Mbps。Cyclone器件具有双数据速率(DDR) SDRAM和FCRAM接口的专用电路。Cyclone FPGA中有两个锁相环(PLLs)提供六个输出和层次时钟结构,以及复杂设计的时钟管理电路。这些业界最高效架构特性的组合使得FPGA系列成为ASIC最灵活和最合算的代方案。

3.设计的理论分析

FPGA数据采集电路测量正弦波信号频率的原理是:在正弦波整形后得到的方波信号的一个周期为Tc秒的数据采样信号进行计数,其计数结果乘以1/Tc,就是被测正弦波的频率,单位为Hz。测量正弦波信号周期的原理是:在正弦波信号整形后得到的方波信号的一个周期为Tc秒的数据采样信号进行计数,其计数结果乘以Tc秒,就是被测信号的周期,单位为秒。测量两个同频信号的相位差,关键就是要测出两个同频正弦波信号起点的时间差△t,若△t测出,则根据:△a=△t×360°/t即可求出相位差△a,因此其测量原理与测量正弦波信号周期的原理相似。

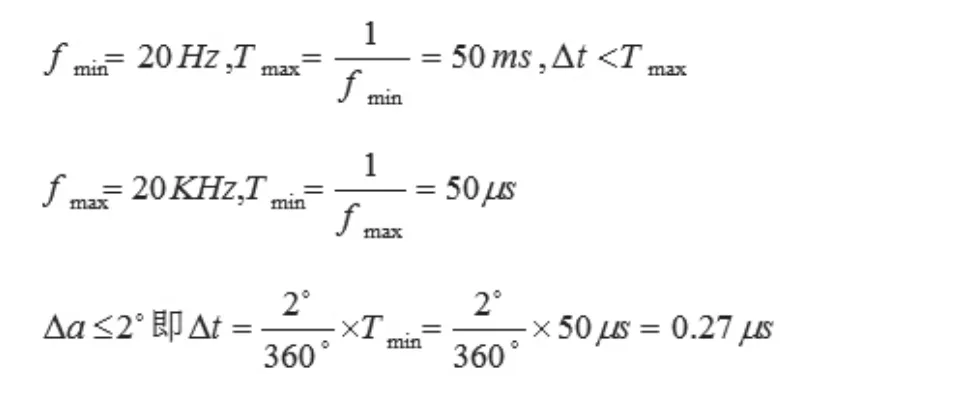

本数字式相位测量仪的要求是测试并显示两路输入信号的频率范围在20Hz~20kHz,测试并显示信号a,b的相位差,相位差的变化范围为:a = 0°~359.9°,相位差的显示分辨率为0.1,要求测量相位差的绝对误差 ≤ 2°。由此可知:

由以上分析可以知道,要保证系统要求的精度,必须采用高于1/0.27uS=3. 7MHz的采集速度对信号周期进行计数,为进一步提高测量精度,同时为了便于计算,我们采用了10MHz方波作为FPGA数据采样信号,FPGA在10MHz时钟信号作用下对待测信号的周期进行计数,并对两个同频正弦信号所对应的时间差进行计数,分别得到19位的数字量,19位的数字量的物理单位是0.1us。本设计采用20MHz的信号进行二分频,得到10MHz的数据采样信号,其采样的周期为0.1us。

为了实现中低频测量精度的要求,我们可以采用10MHz的信号来循环计数被测信号的周期和两个同频正弦信号的相位所对应的时间差值,时间单位为0.1us。也就是说,计数的周期和相位差所对应的时间差值的精度是0.1us。利用被测信号来刷新采样计数,在20Hz时,刷新的频率可以精确到10Hz,20kHz时达到10kHz,可以实现高频多测量,低频少测量的效果,时间计数精确可靠,为后面单片机的数据处理提供了稳定、可靠的数据源。

4.FPGA数据采集电路系统组成

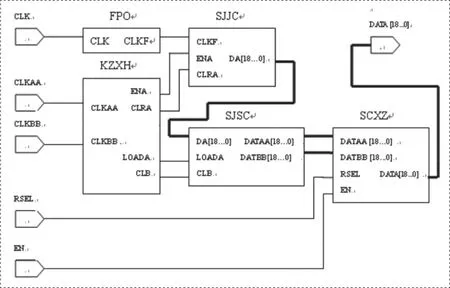

根据以上设计思想,FPGA数据采集电路可以设计成五个模块,他们分别是:失重信号分频模块FPQ,测量控制信号发生模块KZXH,被测信号有关时间检测模块SJJC,数据锁存模块SJSC和输出选择模块SCXZ,整个系统组成框图如图1所示。

图1 FPGA数据采集电路系统组成框图

其中时钟信号分频模块的FPQ作用是:将输入的20MHz的信号分频成10MHz的控制基准时钟信号CLKF。测量控制信号发生模块KZXH的作用是:根据两路被策信号整形后得到的方波CLKAA和CLKBB,产生有关的控制信号,包括时间检测使能信号ENA,时间检测清零信号CLRA,锁存频率数据控制信号LOADA,锁存两被测信号相位差数据控制信号CLB。被测信号频率和相位差数据检测模块SJJC的作用是:在控制信号ENA和CLRA的控制下,对测控基准时钟信号CLKF进行计数和清零,以便获取有关频率和相位差数据。数据锁存模块SJSC的作用是:在LOADA的上升沿将频率锁存在DATAA中,在CLB的下降沿时将相位差数据锁存在DATAB中。输出选择模块SCXZ的作用是:根据单片机发出的控制信号EN和输出数据类型选择信号RSEL,将被测信号频率数据或相位差数据输出。

5.软件设计

程序利用VHDL语言进程之间的并行关系同时对被测信号的周期和相位差值进行计数。并使用Quartus II对其进行编译及时序仿真。

FPGA数据采集电路的功能就是实现将待测正弦信号的周期、相位差转变为19位的数字量。并将数据存放到锁存器中等待单片机的取数。

根据系统的整体设计方案,FPGA数据采集电路的输入信号有:CLK—系统工作用时钟信号输入端;CLKAA,CLKBB—两路被测信号输入端;EN—单片机发出的传送数据使能信号,在EN的上升沿,FPGA向单片机传送数据;RSEL—单片机发出的传送数据类型信号,当RSEL=0时,FPGA向单片机传送被测信号的频率数据,当RSEL=1时,FPGA向单片机传送被测信号的相位差数据。FPGA数据采集电路的输出信号有:DATA[18…0]—FPGA到单片机的数据输出口,由输出控制信号EN和RSEL控制。其应实现的功能就是负责对被测信号频率数据和相位数据的实时测量。

6.Quartus II仿真

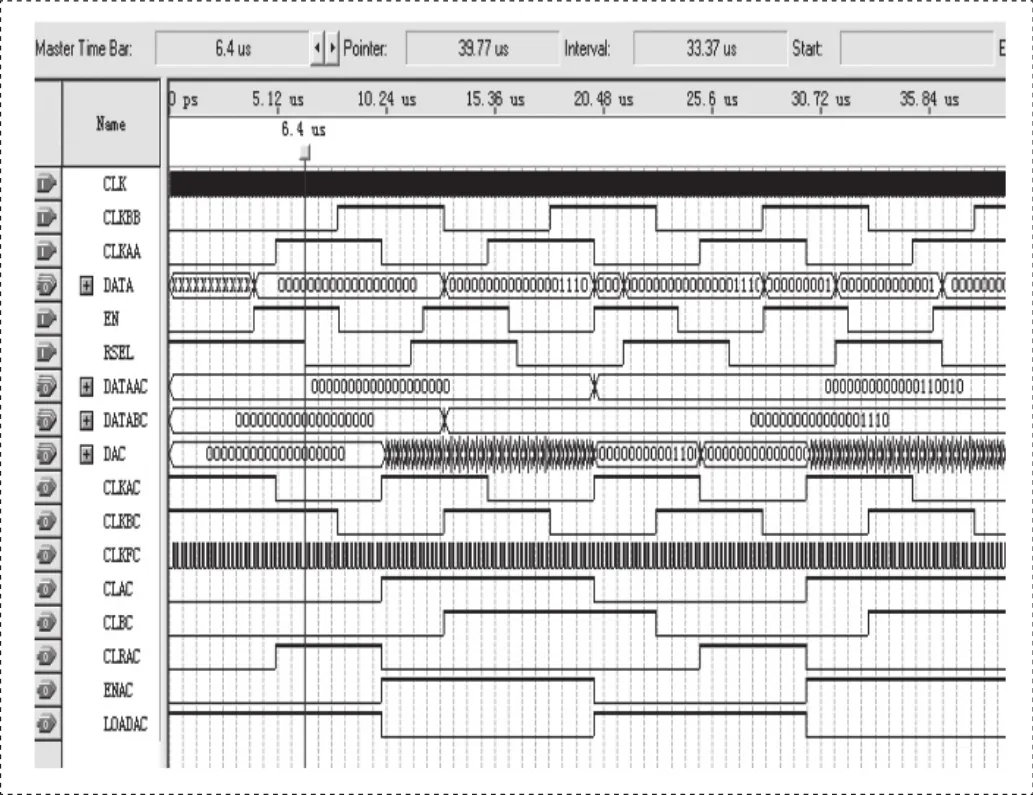

主要使用Quartus II对已经编写好的VHDL程序进行时序仿真。根据需要对各个输入信号设定初值后进行仿真,可得到正确的波形图,如图2所示。

图2 FPGA数据采集仿真图

7.总结

本文论述的基于FPGA的相位测量仪,充分利用了FPGA器件的特性,将数据采集分为五个模块,采用了10MHz的控制基准时钟信号CLKF,将相位差转变为19位的数字量,得到较为简单的硬件电路,简化了软件编程,整个系统超过了设计的要求。

[1]汪伟,黄芳玲,等.CPLD在相位测量中的应用[J].仪器仪表学报,2003(24).

[2]金宁,汪伟,等.高精度数字检相电路设计[J].中国计量学院学报,2002(1).

[3]王振江.VHDL数字电路设计与应用实践教程[M].北京:机械工业出版社,2006.1

[4]VHDL Landuage Reference Guide,Aldec Inc.Henderson NV USA,1999.