一种高效多模式雷达数字下变频的设计

2018-05-23,,

,,

(1.中国人民解放军 92941部队94分队,辽宁 葫芦岛 125001; 2.上海航天电子技术研究所,上海 201109)

0 引言

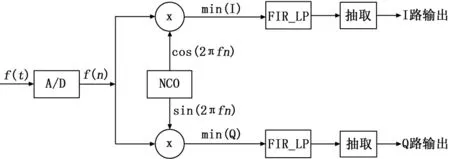

传统的数字下变频过程包括A/D转换、数字鉴相(混频)和FIR低通滤波,其经典结构如图1所示[1]。其中NCO为数字振荡器,通过两个乘法器完成混频然后经过低通滤波和抽取完成数字下变频。经典结构可以很好的完成确定带宽下的数字下变频工作,但现代雷达的发展对雷达性能提出了新的要求。其中包括一部雷达应该可以工作在不同信号带宽的工作模式下;雷达应该具有更高的信号带宽等。雷达工作在不同信号带宽的工作模式下可以实现不同的战场需求,如搜索、成像、侦查监听等。

提高雷达的信号带宽可以提高雷达的距离分辨能力,而且使用宽带和超宽带雷达信号结合成像算法可以实现雷达成像[2]。本文针对以上两个要求,提出了一种高效多模式数字下变频的设计方案。结合设计实例和实验数据分析,证明了该方案可以同时满足宽带模式下的高速数据处理和窄带模式下高抽取率的滤波器性能。使得不同带宽的工作模式下,雷达可以使用同一个接收前端完成雷达信号的采集。

图1 经典数字下变频实现结构

1 四倍中频采样

1.1 中频直采采样率要求

对于宽带雷达中频信号,回波信号的频带范围为:

f0-B/2≤f≤f0+B/2

(1)

其中:f0为回波信号的中心频率,B为回波信号的带宽。为了保证DDC后频带不产生混叠,中频设定应满足:

f0>B/2

(2)

雷达回波的处理多采用中频直接采样的方法,中频直接采样可以在信号中频段就完成信号的数字化,可大幅度提高信号质量,同时有效避免模拟正交调制带来的幅度和相位不一致等。但随着雷达信号带宽的增加,中频的中心频率也需要一并提高。根据采样定理,中频直接采样的采样率应满足以下关系:

fs≥2(f0+B/2)

(3)

因此针对宽带雷达信号,中频信号采样需要较高的采样率。高采样率对AD器件提出了较高的要求,宽带雷达信号更是要求AD器件的采样率应达到GHz的量级,随着当代AD器件的迅猛发展,市场上已经有相关产品可以满足需求。同时,高采样率意味着采样后的数字信号具有较高的数据率,高数据率的问题通常通过数据并行化的方法解决,如fs为3.6 G的采样率下,FPGA是不可能完成相关处理的,但可以将3.6 G的数据划分为16路225 M的数据流,并将FPGA内部的功能模块按照并行数据流的方式设计。

1.2 四倍中频采样原理

高速实时混频处理要求高精度的乘法器,需占用较多的逻辑资源。如16路225 M的数据流完成混频处理,需要占用32个高速乘法器,并需要复杂的NCO控制电路。而采用四倍中频采样技术,可以解决上述问题,并且可以为后续的滤波处理提供便利。

根据式(3),采样率应大于2倍中频与带宽的和;结合式(2)信号带宽小于2倍中频,为了充分利用数字带宽,信号带宽应接近2倍中频。因此满足采样定理的最低采样率应接近四倍中频,所以采用四倍中频采样既满足了采样定理,又充分利用了数字带宽,在不考虑节省系统资源的情况下,四倍中频采样的选择也是较优的。

四倍中频采样原理[3]如下:

设中频回波信号为f[n],混频输出为fI[n],fQ[n],则有:

(4)

混频器NCO的输出取决于中频f0与采样频率fs的比值。将NCO输出值量化后按照次序与输入信号相乘。需要使用高效乘法器完成实时乘法运算,量化过程中可能出现一定的量化误差。如果取特殊采样频率fs=4f0,振荡器的输出是4个特殊值的序列重复,即:

(5)

此时,混频计算简化为置零和输入信号的符号选择,混频处理也不会带来因为量化带来的误差。I,Q两路的输出为:

(6)

显然,四倍中频采样条件下,鉴相输出具有间隔为0的特点;后续设计可以利用此特点简化滤波器结构。原来的乘法器和NCO系数控制也简化为符号选择操作,大大减少了资源占用。

2 并行抽取滤波器设计

2.1 抽取滤波原理[4]

并行抽取滤波器的设计主要有两个方面,一个是抽取滤波,一个是滤波器的并行性[3]。

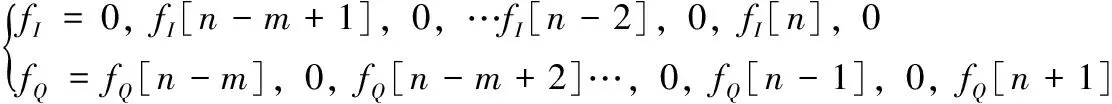

为了计算方便设定滤波器阶数m为奇数,滤波器系数为h0,h1…hm。滤波器的输入由式(6)提供,具有间隔为0的特点,设混频器的输出为:

(7)

设抽取前滤波输出为yI[n],yQ[n],则:

(8)

式(8)表明,抽取前的滤波器输出中,每一个滤波输出只与一半的混频输入和一半的滤波器系数有关。现在计算yI[n-1],yQ[n-1],其结果表示如下:

(9)

即I,Q的每一个滤波输出只与一半的混频输入和一半的滤波器系数相关,但与相邻的滤波输出相关的是不同的滤波器系数。

以此类推,设k为整数,可以得到结论:

(10)

(11)

此时,如果进行抽取滤波,且抽取因子取2的整数倍,则抽取后的I路和Q路输出将分别只与一半的的滤波器系数和滤波器输入有关。因此在FPGA中实现滤器器的计算流程时至少可以降低一半的输入和一半的滤波器系数,并且降低一半的乘法器使用。这是常规的抽取滤波器做不到的。以第二小节中3.6 GHz采样的中频回波为例,16路的输入数据流经过混频后应该输出间隔为0的16路I路混频信号和16路Q路混频信号并将其作为低通FIR滤波器的输入。32路225 M的数据流需同时进行滤波运算,需占用大量的FPGA资源和高速乘法单元,普通FPGA器件很难满足要求。如果采用并行抽取滤波的方式,无论采用式(10)或式(11),I路和Q路的滤波器输入数据流都可以直接降低到8路,将极大的减少逻辑资源和高速乘法器的占用,使得DDC模块在FPGA上的实现成为可能。

图2 并行滤波结构框图

2.2 并行滤波器结构设计

并行抽取滤波器的另一个问题是并行滤波。高速串行数据流通过并行化转变为并行的低速数据流,滤波器要求对并行到达的数据同时滤波,产生并行的滤波输出[5]。所以并行滤波要解决的是具有相位关系的数据(本应该有时序差别)并行到达时如何滤波的问题。

图3 设计实例实现结构图

以4路并行滤波为例,设滤波器阶数为m。根据滤波器的卷积原理,每个滤波器的输出结果与当前输入和当前输入之前m个输入数据相关。根据滤波原理和并行输入的特性,设计并行滤波器的实现结构如图2所示:同时到来的4路数据存入长度为4+m的桶形移位寄存器组,存入的数据与位于其之前的(移位寄存器内部相对位置)m个数据一起组成相应的滤波模块的输入。当前通过并行例化4个滤波器,并将4个滤波器的输入与相应寄存器组的寄存器相关联,每个时钟,桶形移位寄存器的每一个寄存单元向前移位4个寄存器单位,组成下一个时钟滤波模块的输入。同时滤波器输出方面,每个时钟由并行的4个滤波模块输出对应于4路输入的滤波输出,4个滤波输出保持了相对于4路输入信号的时序关系,至此并行滤波完成。

通过并行滤波结构,结合抽取滤波的方法实现了对并行到来的高速数据实时滤波的要求。桶形移位寄存器的设计实现了滤波的并行化,抽取和四倍中频采样降低了系统内部运行的数据率。

3 设计实例和实验数据分析

3.1 不同带宽雷达工作模式的DDC

雷达宽带工作模式是数据率最高的工作模式,当雷达工作在其他带宽时,可以通过滤波器系数动态配置的方法修改宽带滤波器的系数,复用滤波器结构。然后根据输出数据要求的数据率,进行数据抽取。

当雷达工作在窄带模式时使用的发射信号带宽远远小于宽带带宽(差别在500倍以上),实际的抽取因子D达到100~1 000时,要求设计的数字滤波器的带宽较窄,同时为了抑制高频噪声叠加效应,同样要求过度带也较窄。要实现这样的数字滤波器在工程实践上几乎是不可能的,因为滤波器系数将会达到几百甚至上千阶。解决方法为采用多级抽取滤波,即通过多个滤波器与抽取器级联[6],上一级滤波器选择适当的通带和阻带滤除部分无用频段,抽取后数据进入下一级继续滤波,下一级滤波器在抽取后的数字频段基础上再选择适当的通带和阻带系数滤波、抽取。使用多级抽取的方法,可以极大的减少计算量,只要满足式(12),即可保证抽取过程不混入过多的高频杂波[7]。其中k和l是两级滤波器的抽取因子,D为等效的总的抽取因子。而且由于第一级抽取后数据率降低为原来的1/k,后一级的滤波器为低速或直接串行数据流的滤波器即可。

D=k×l(k,l是大于1的整数)

(12)

3.2 设计实例结构

在某雷达接收机中,系统采样率为3 600 MHz,回波信号中心频率为900 M,具有三种不同的工作带宽,分别是: 4 M带宽工作模式,输出数据率10 M,暂定为模式1; 50 M带宽工作模式,输出数据率100 M,暂定为模式2; 1 600 M带宽工作模式,输出数据率1 800 M暂定为模式3。根据不同工作模式下的不同要求,设计其DDC实现结构如图3所示。

经过高速AD采样的3 600 MHz数据率的回波信号在FPGA接口处分成16路225 M的低速数据流进入FPGA。由于采用了四倍中频采样和因子为2的并行抽取滤波模式,混频后的16路数据I,Q两路各选相关的8路数据进入第一级滤波器。工作状态选择信号(Mod_Sel)决定当前的工作模式,当雷达工作在模式3时,滤波器选择相应的滤波系数(记为系数1),滤波完成直接输出8路并行的DDC结果(等效于1 800 M串行数据率);当雷达工作在模式2时,滤波器选择模式2滤波器系数(记为系数2),输出的8路滤波结果经过因子18的抽取器输出1路数据率为100 M的DDC结果;当雷达工作在模式1时,前端复用模式2的处理结构,第一级滤波器选择系数2,输出的滤波结果经因子为18的抽取器抽取输出1路数据率为100 M的滤波结果,在100 M的输出数据上级联一级窄带低通滤波器(其滤波器系数记为系数3),同时再次以因子10抽取滤波结果,输出10 M数据率的 DDC结果。

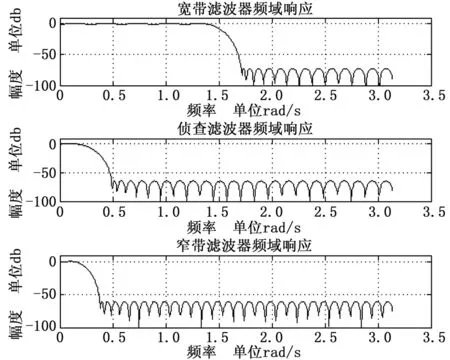

使用到的三种滤波器频域响应如图4所示。

图4 滤波器频域响应

宽带滤波器频域响应图对应于系数1所代表的低通滤波器幅度频域响应;侦查滤波器频域响应图对应于系数2所代表的低通滤波器幅度频域响应;窄带滤波器频域响应图对应于系数3所代表的低通滤波器幅度频域响应。三种滤波器具体设计参数如下表(设计方法为等纹波):

表1 滤波器参数设计表

以上结构提供了一种不同带宽模式下雷达回波使用同一结构处理的方案。首先通过4倍中频采样技术简化了I/Q鉴相过程,直接省掉了混频乘法器,同时提高了混频精度(NCO序列无量化误差)。利用雷达同一时间只会工作在一种工作模式下的特点,设计实现了功能模块的最大可能的复用。其中第一级滤波器通过滤波器系数的动态配置在三种工作模式下分别完成了要求的滤波器性能。相比使用独立的滤波器设计,资源占用减少到非复用模式下的1/3。

3.3 实验结果

为方便观测,使用点频信号输入。通过在chipscope工具上录取数据,使用matlab观测的方式验证实验结果。

实验一:将设计实例的工作模式设定为模式一,设置输入的点频信号信号频率为902 MHz,采集实例最终输出的结果如图5所示。

图5 模式1(902 M)DDC输出频谱

模式一为窄带工作模式,工作带宽4 MHz,最终输出的数据应该是数据率为10 MHz、信号频率为2 MHz的数字下变频结果,观测图形与预期结果相符合。

实验二:将设计实例的工作模式设定为模式二,设置输入的点频信号信号频率为925 MHz,采集实例最终输出的结果如图6所示。

图6 模式2(925 M)DDC输出频谱

模式二为侦查工作模式,工作带宽50 MHz,最终输出的数据应该是数据率为100 MHz、信号频率为25 MHz的数字下变频结果,观测图形与预期结果相符合。

实验三:将设计实例的工作模式设定为模式三,设置输入的点频信号信号频率为1 700 MHz,采集实例最终输出的结果如图7所示。

图7 宽带模式(1 700 M)DDC输出频谱

模式三为宽带工作模式,工作带宽1 600 MHz,最终输出的数据应该是数据率为1 800 MHz、信号频率为800 MHz的数字下变频结果,观测图形与预期结果相符合。参差的其他多条谱线为AD器件带来的谐波分量。

通过实验验证结果可知,本文提出的DDC结构,实现了预期的数字下变频性能。

4 结论

本文针对雷达系统不同带宽工作模式共用同一个信号接收前端的应用需求,提出了一种高效多模式可实时切换的DDC设计方案。采用了四倍中频采样技术降低了计算复杂度、减少了逻辑资源占用;同时设计了一种并行的抽取滤波器解决了高数据率的宽带雷达信号在FPGA中实时处理的问题。最后给出设计实例和实验结果,验证了设计的正确性。

参考文献:

[1] 刑 燕. 中频采样和数字正交器的原理及工程实现[D]. 南京:南京电子技术研究所, 2003.

[2] 陈 洁. 超宽带雷达信号处理及成像方法研究[D]. 北京:中国科学院研究生院,2007.

[3] 张炳煌,雷 宏. 超宽带SAR数字正交解调器设计[J].电子测量技术,2006, 29(6):36-39.

[4] 徐尚中,何东健,万海军. 基于FPGA的DDC中抽取滤波系统的设计[J]. 微计算机信息, 2008, 24(9-2): 132-133.

[5] 张峻涛,王 平,傅石雨. 超高速并行滤波结构FIR的FPGA实现及应用[J]. 通信对抗,2013,32(1): 36-39.

[6] 柏晓锁,施春荣. 基于FPGA及PC机的级联数字抽取滤波技术[J]. 雷达与对抗, 2009, 3(3): 41-43.

[7] 陈朝阳,孙剑伟,郑兆青,等.多级滤波算法的ASIC实现[J]. 华中科技大学学报,2006,34(2):4-7.