一种基于FPGA的LCD显示方案设计

2018-04-23张佃青王宇红王慧铮

张佃青 詹 雄 杨 立 王宇红 王慧铮

(南瑞集团中电普瑞科技有限公司,北京 102200)

LCD显示模块为电力系统控制保护装置和其他工业控制装置提供了友好的人机接口。电力系统控制保护装置集测量、控制、监视、保护、通信等多种功能于一体,是在电力系统或电力设备发生故障和不正常运行情况时,用于快速切除故障,消除不正常状况的重要二次设备[1]。

继电保护新原理的出现,灵活交流输电、直流输电等新技术、设备的大量应用,智能化变电站的提出与推广,对控制保护装置的功能、性能提出了更高的要求,对装置内的核心处理器芯片的性能也提出了更高的要求[2-3]。目前控制保护装置中广泛采用高性能DSP、ARM、POWERPC等处理器芯片[2,4-5]。

为了减轻装置其他CPU的负担,目前电力系统控制保护装置 LCD显示的主流方案是单独配置一套带有ARM芯片的智能嵌入式LCD模块,由装置内的通信管理插件通过RS485或CAN等通信方式将显示内容传给智能LCD模块。该方案技术成熟,但系统略显复杂,需要开发处理器芯片以及LCD模块ARM芯片2种芯片的硬件和软件,对于软硬件后期维护带来不便。

本文在目前控制保护装置中负责对外通信的通信管理插件上,在广泛采用的POWERPC+FPGA硬件架构的基础上,提出了一种LCD显示方案,POWERPC通过基于Qt开发的显示模块应用程序,将显示数据通过LINUX系统LCD驱动的Framebuffer设备快速传输给FPGA,而FPGA则实现显存数据存储及LCD控制器功能。该方案取消了独立显示系统,其CPU开销小,简化了LCD显示系统设计,使开发者只需关注 Qt显示模块应用程序开发和维护,不用考虑LCD模块ARM芯片软件开发和维护,为控制保护装置提供了一种灵活有效、简便经济的LCD显示方案。

1 控制保护装置系统架构

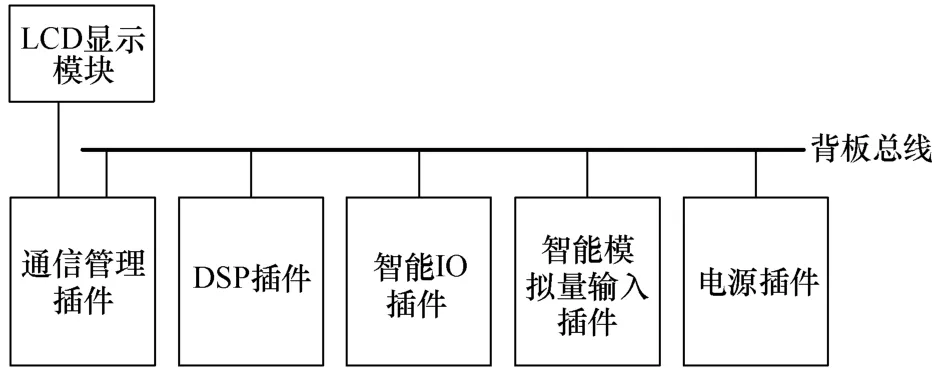

控制保护装置的具体功能是:接收模拟量数据、保护相关的开入量,执行数据运算和逻辑判断,输出调节指令或保护动作;提供通信接口、人机接口界面及录波回放等功能。控制保护装置系统架构采用分布式多处理器并行运算技术的架构[2],如图 1所示,主要包括DSP插件、智能IO插件、智能模拟量输入插件、电源插件、通信管理插件和LCD显示模块。装置可以灵活配置DSP插件、智能插件的种类和数量来满足不同工程应用需求。

图1 控制保护装置系统架构框图

DSP插件的处理器采用定点或浮点DSP,具有强大的数字信号处理能力,主要功能是通过背板总线从智能IO插件收集开入量信息,从智能模拟量输入插件获取电参量采集数据,执行复杂的电力电子装置控制调节实时算法或继电保护逻辑运算,从本插件相关接口输出调节控制指令或通过智能 IO插件输出保护动作指令。在一块DSP插件还无法完成控制保护相关算法时,可以配置多块DSP插件进行并行处理,协同完成相关算法。

智能 IO插件包括开入量采集模块和开关量输出模块两种。开入量采集模块对输入的开关量采用光耦隔离技术,转换成与插件内后级数字电路相匹配的低压数字信号,插件内的CPU对各路开关量数据信号进行采集和处理,并将开入量状态信息通过背板总线传递给装置其他智能插件。开关量输出模块接收相应DSP插件的控制命令,输出信号继电器或操作继电器接点信号。操作继电器接点接入跳、合闸回路,由启动逻辑和保护逻辑协同控制,实现保护动作指令的可靠输出。

智能模拟量输入模块用于完成对从传统互感器变换输出的交流电压、交流电流信号,或直流电压信号进行隔离、信号调理及模数转换,经过标幺化等数据处理,将采集数据通过背板总线传递给装置其他智能插件。

通信管理插件负责装置的通信、录波回放及LCD显示控制功能等。该插件通过背板总线收集模拟量数据和开关量数据,收集各插件的状态信息,经处理器芯片完成录波回放功能,执行协议转换处理,实现装置的对外通信;同时该插件通过由FPGA构建的LCD控制器完成LCD的显示控制。

LCD模块相对简单,仅包括LCD显示屏及LCD显示接口电路。该模块一般背附在装置前面板。

电源插件用来给装置其他插件和 LCD显示屏提供电源。

2 控制保护装置LCD显示硬件设计

2.1 总体设计

在装置的通信管理插件上予以实现。系统硬件采用POWERPC+FPGA架构,主要由POWERPC模块、FPGA模块、背板总线接口电路和LCD接口电路组成,如图2所示。

图2 LCD显示总体架构框图

该硬件通过背板总线与装置其他板卡实现内部通信,POWERPC通过芯片的LocalBus总线获取相关信息,完成103、104或IEC61850等规约转换,实现装置的对外通信。同时,PowePC通过基于Qt开发的显示模块应用程序,将显示数据由LINUX系统LCD驱动的Framebuffer设备通过LocalBus总线快速传输给 FPGA。而FPGA则实现显存数据存储及LCD刷屏及显示功能。该系统与目前普遍使用的通信管理插件原理上的区别在于,不再采用 RS485等通信方式与智能 LCD模块通信,而是通过 LCD接口电路由接插件直接与LCD屏连接。

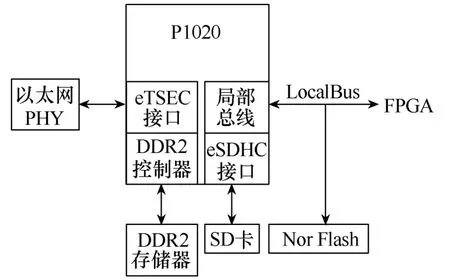

2.2 POWERPC模块设计

POWERPC模块组成如图3所示,选用Freescale公司的P1020作为处理器,该芯片是专用的网络通信处理芯片,双核,每核时钟最高频率各为800MHz[6]。通过内部DDR2控制器外扩DDR2存储器,为程序运行和数据动态处理提供存储空间,其型号为MT47H64M16HR-3ITE,容量为 64M×32bit,速度为667MHz;通过eSDHC接口外扩SD卡,为应用程序、大量数据存储提供空间,其型号为03-SDSDAA-008G,容量为8G;通过LocalBus局部总线外扩Nor Flash存储器,用来存储Bootload程序和系统程序,其型号为 S29GL01GP12TFI01,容量为 64M×16bit,同时通过该局部总线与FPGA通信;通过eTSEC接口外扩以太网PHY芯片,实现对外通信。

图3 POWERPC模块框图

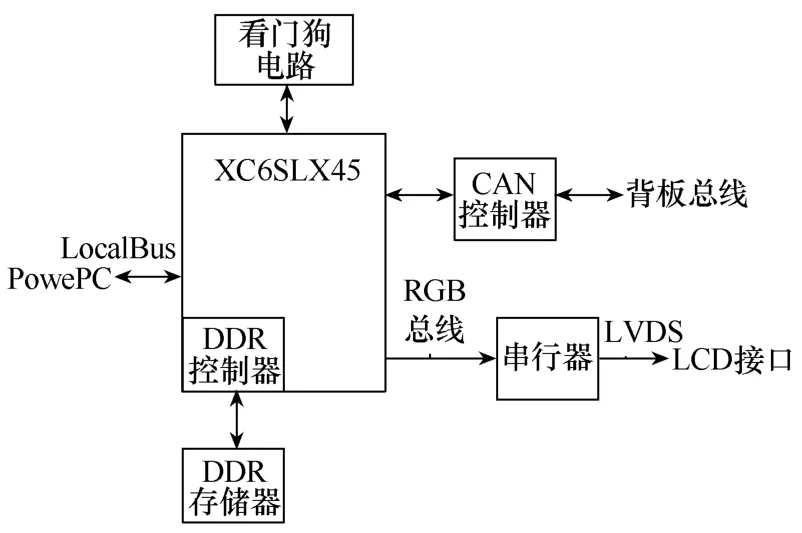

2.3 FPGA模块及外围电路设计

FPGA模块及外围电路组成如图4所示,FPGA选用Xilinx公司的Spartan6系列的XC6SLX45,该芯片具有6822个SLICE,43661个逻辑单元,116×18kb的块RAM,8个DCM时钟管理单元,2个DDR控制器[7-8]。

图4 FPGA模块及外围电路框图

DDR存储器选用 MT46V16M16CY,容量为16M×16bit,用作显存,存储容量较一般的 SRAM容量要大,可以满足分辨率为 640×480及以上的LCD显存要求。CAN控制器选用SJA1000,用作与装置其他板卡通信。串行器选用 DS90C383,用来将FPGA输出的16个TTL电平的RGB信号串行化成4对LVDS信号,用以提高LCD接口信号的电磁兼容性能。看门狗电路选用IMP706,用以监视电源电压的正常情况,监视FPGA和POWERPC的程序运行情况。

3 LCD显示软件设计

设计了以显示屏分辨率为640×480的LCD显示功能软件。LCD显示部分的系统软件设计主要包括基于FPGA的LCD控制器设计、Linux系统下LCD显示驱动程序设计和LCD显示应用程序设计。

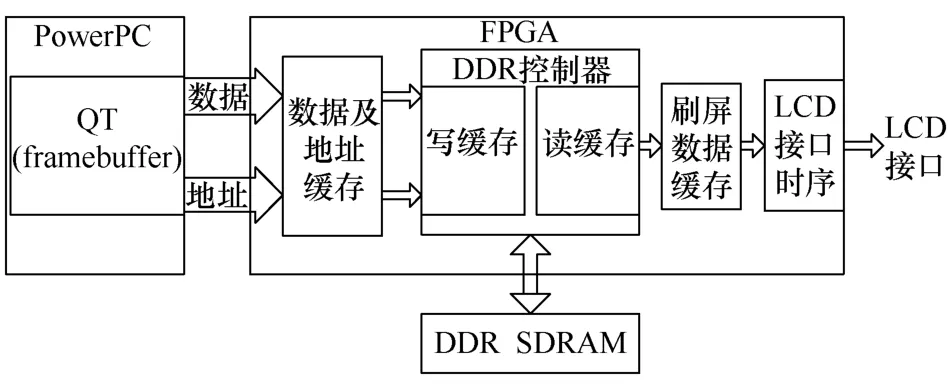

3.1 LCD控制器设计

LCD控制器主要包括与POWERPC接口的数据及地址缓存、DDR双端口控制模块、LCD刷屏数据缓存和LCD接口时序控制等模块组成,示意图如图5所示。

图5 基于FPGA的LCD控制器功能框图

DDR控制器由 Xilinx ISE开发环境的 CORE Gen模块中的MIG工具调用和配置对应的DDR控制器IP形成。该控制器支持多端口操作模式[9-10],实际设计为2个端口,一个端口用于接收POWERPC的显示RGB数据,并存入DDR显存相应的单元中,一个端口读取DDR的显存数据,用于LCD刷屏显示。

DDR SDRAM芯片时钟频率可达到100MHz,但 DDR应用的接口带宽与数据的操作方式有很大的关系。在地址连续存取方式下,效率高,接口带宽高,在地址不连续随机存取方式下,效率低,接口带宽也低。为了支持显示数据的随机存取,设计了POWERPC接口的数据及地址缓存模块,用以提高POWERPC LocalBus总线访问速度,以便LocalBus总线可以挂载其他接口数据。设计LCD刷屏数据缓存,用来匹配LCD接口控制时序。

图6给出LCD接口控制时序,其中VSYNC为场同步信号,HSYNC为行同步信号,CK为像素时钟信号,RGB为像素RGB数据。液晶显示屏的刷新频率为 60Hz,即 VSYNC为 60Hz,而一场则由480个行同步信号组成,则HSYNC为至少28.8kHz。同理可得 CK至少为 18.5MHz。程序实现时,由FPGA的 10MHz时钟输入信号经过时钟管理模块DCM产生一个20MHz的时钟信号CLK,作为LCD接口的主时钟。场同步信号 VSYNC、行同步信号HSYNC、像素时钟CK都由主时钟CLK产生。

图6 LCD接口控制时序

3.2 LCD显示驱动程序设计

LCD显示驱动采用Linux内核标准FrameBuffer帧缓冲设备驱动架构,如图7所示,FrameBuffer设备文件为/dev/fb0。

图7 FrameBuffer驱动架构

FrameBuffer驱动采用 OF_Platform机制,在POWERPC设备树文件中添加p1020-lcd设备。

FrameBuffer驱动加载后,向 Linux内核注册FrameBuffer Platform驱动,内核根据设备树会匹配该设备,并在Probe函数中完成LocalBus显存物理地址映射虚拟地址、FrameBuffer fbinfo帧缓存信息结构体固定及可变屏幕参数设置、操作函数 fb_ops结构体注册、注册FrameBuffer设备。

应用程序接口函数在fbmem.c中定义。

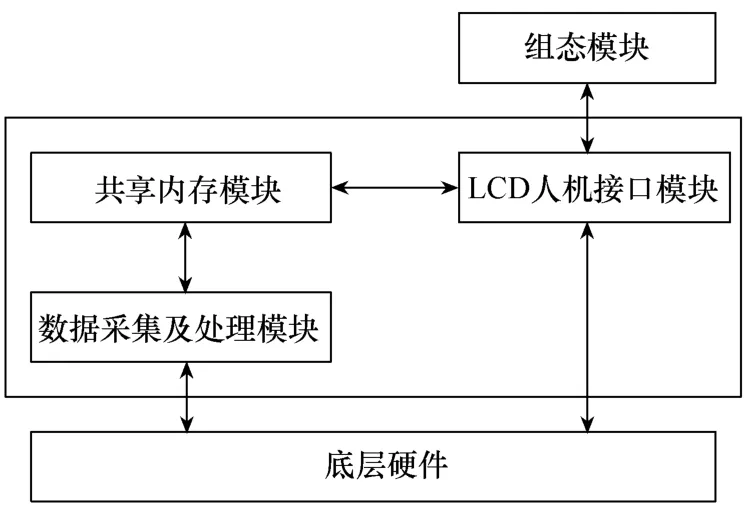

3.3 LCD显示应用程序设计

LCD显示应用程序整体结构包括主要数据采集及处理模块、共享内存模块、LCD人机接口模块和组态模块,如图8所示。结合LINUX系统特点,应用程序采用多进程、多任务和共享内存数据库,各个进程或任务以共享内存数据库为中心进行数据交互和消息交换。

图8 LCD显示应用程序整体结构

数据采集及处理模块负责与监控后台或装置内部其他插件进行数据通信,获取监控信息和装置状态信息,并将相关相关信息映射到共享内存区。

共享内存模块提供动态内存共享。应用进程利用接口函数读写数据库对象,在应用进程间收发消息;实现了内存数据实时更新及并发性协调,以确保内存数据的安全性。

组态模块使用 Qt的控件库来创建嵌入式图元库,同时通过一个xml格式的配置文件,自动产生不同的组态画面,实现图形组态,以便于LCD人机接口模块调用。

LCD人机接口模块从共享内存区获得需要可视化的数据,完成显示界面的初始化,根据设计好的图形界面生成对应的命令序列,通过Qt的LCD接口Framebuffer设备实现LCD的显示控制。

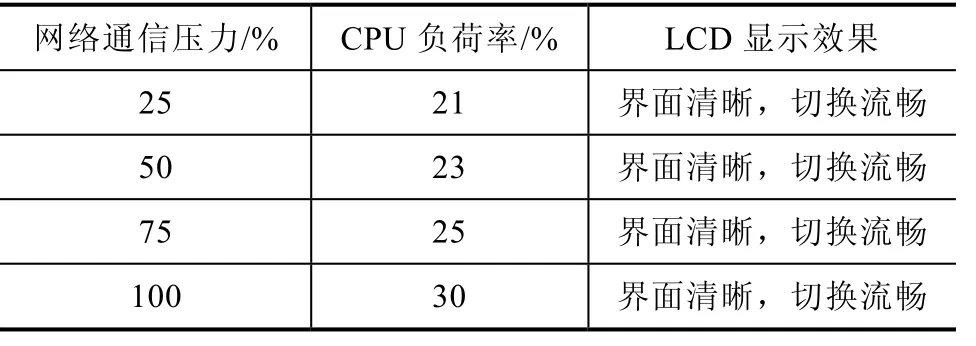

4 测试结果及工程应用

通信管理插件程序按照工程应用功能要求进行设计,实现了IEC61850 MMS协议通信、录波、人机接口等功能。在此基础上,测试所设计的插件是否同时满足通信和LCD显示的要求。测试插件在不同网络通信压力下CPU的负荷率及LCD显示情况,见表1。

表1 不同网络通信压力下CPU负荷率

测试结果表明,不同网络压力下,CPU的负荷率不高于30%,LCD显示界面清晰,界面切换流畅,插件同时满足了通信和显示的要求。

该通信管理插件及 LCD显示系统通过了第三方测试,已在特高压串补工程控制保护装置中得到应用,目前运行稳定。

5 结论

本文基于POWERPC+FPGA的硬件架构,提出了在电力系统控制保护装置通信管理插件上实现LCD显示的方案,并加以实现。POWERPC通过基于 Qt开发的显示模块应用程序,将显示数据通过LINUX系统LCD驱动的Framebuffer设备快速传输给FPGA,而FPGA则实现显存数据存储及LCD控制器功能。

该方案取消了独立显示系统,其CPU开销小,简化了LCD显示系统设计,为控制保护装置提供了一种灵活有效、简便经济的LCD显示方案。

[1] 邰能灵, 范春菊, 胡炎. 现代电力系统继电保护原理[M]. 北京: 中国电力出版社, 2012.

[2] 李响, 刘国伟, 冯亚东, 等. 新一代控制保护系统通用硬件平台设计与应用[J]. 电力系统自动化, 2012,36(14): 52-55.

[3] 李岩, 刘涛, 黎小林, 等. 南澳多端柔性直流输电工程控制保护系统体系架构[C]//第五届电能质量及柔性输电技术研讨会论文集, 广州, 2014: 513-518.

[4] 刘益青, 高伟聪, 魏鹏, 等. 基于MCU+DSP多处理器构架的微机保护硬件平台设计[J]. 电力系统保护与控制, 2010, 38(10): 89-91, 95.

[5] 成敬周, 张举, 康怡, 等. 基于可编程芯片及数字信号处理器的微机保护硬件平台设计方案[J]. 电工技术杂志, 2004, 24(12): 78-82.

[6] Freescale. P1020 QorIO integrated processor reference manual[Z]. 2013.

[7] Xilinx. Spartan-6 family overview[Z]. 2012.

[8] Xilinx. Spartan-6 FPGA data sheet[Z]. 2011.

[9] 吴连慧, 周建江, 夏伟杰. 基于FPGA的DDR3多端口读写存储器管理设计[J]. 单片机与嵌入式系统应用, 2015, 14(1): 71-74.

[10] Xilinx. Spartan-6 FPGA memory interface solutions user giude[Z]. 2011.