基于FPGA的大比例系数高精度I/F电路设计

2018-04-13程远超赵新强吕成方

程远超,黄 伟,赵新强,吕成方,杨 洋

(1.北京航天时代惯性仪表科技有限公司,北京 100039;2.北京航天控制仪器研究所,北京 100039)

0 引言

电流频率转换电路(I/F转换电路)是一种将输入的模拟电流信号转化为数字量频率信号的电路[1],即一种模数转换器。随着技术的发展,这种模数转换器的形式是多种多样的[2-3],如V/F转换电路[4]、基于DSP+FPGA的高分辨I/F电路[5-6]、AD652芯片等。对于目前经典I/F转换电路来说,其精度一般能达到3×10-5量级,温度系数在1×10-5左右,能满足大多数任务需求。但根据实时应用背景高精度大比例系数的要求下分析,能满足该比例系数要求的三元变宽电路[7]其工作频率需要至少540kHz,而三元等宽电路则需要1080kHz。随着工作频率的提高,分立器件的开关特性会变差,进而导致线性度变差,难以满足指标要求。在量程一定时,线性度与比例系数是矛盾的,二者不能同时兼顾,所以迫切需要一种比例系数和非线性误差精度指标满足其他性能指标优良的电流频率转换电路来满足任务要求。基于A/D转换芯片的转换电路具有较高的采集速度,但受限于其体积和成本原因,实际非线性精度比较低且难以满足要求,而将二者优势综合起来则可克服上述问题,进而设计高精度IF转换电路,本文介绍的电流频率转换电路即是基于FPGA+A/D+经典IF电路设计的。

本文对比其他方案只选用FPGA,而未使用DSP或单片机[8-9]等,优点是器件结构更简单,减少了数据传递过程,运算和处理速度大大增强。通过对经典电路进行一系列优化,FPGA控制A/D转换器对I/F电路中的积分电压采样,将采集到的电压值进行扩展运算,使电路比例系数达到90000个/(s·mA)。通过对转换电路进行测试,其非线性精度达到2×10-5,温度系数优于5×10-6,满足任务要求。本文重点介绍基于FPGA的高精度I/F转换电路的几个关键技术。

1 原理介绍

在经典I/F电路中,只有积分电压Uj超过门槛电压Uth时,电路才会输出脉冲。高精度I/F电路是在不改变频标的前提下,在积分阶段对Uj进行采样,根据采样点电压并依据对应算法计算出均匀输出的脉冲,实现比例系数的提高,高精度I/F电路设计原理如图1所示。

根据I/F电路原理,在积分阶段中,积分电压为:

Uj=U+I×t

(1)

其中,U为初始电压,I为输入电流,t为积分时间。从式(1)可看出,当输入电流I为一定值时,Uj和t为线性关系。故可将Upp(积分电压峰峰值)均匀分成K份,每份输出1个脉冲,即积分电压Uj每变化Upp/K输出1个脉冲,避免了达到门槛电压才输出脉冲的现象,提高了对小电流的分辨能力。

Upp可在反馈阶段中计算得出,计算公式为:

(2)

其中,If为恒流源,f为频标。从式(2)可看出,Upp与输入电流I有关,当输入电流无穷小时,Upp有最大值。

经典I/F电路和高精度I/F电路的结构分别如图2、图3所示。高精度I/F电路是在传统I/F电路的基础上增加了A/D转换器和数据处理器,利用积分时间对积分电压Uj进行采集,并根据相应的算法均匀输出脉冲,来实现比例系数的提高。

由于噪声的影响,Uj的波形并不规则,将影响采集结果,使每个积分阶段的脉冲输出个数不相同。因此,在反馈阶段内需对脉冲个数进行校准,确保每个周期脉冲输出个数是原始脉冲的K倍。

FPGA作为数据处理器承担所有的控制、数据处理及扩展计算,此外触发器的功能也可在FPGA中实现以简化硬件电路,同时还具有计数功能,可将原始脉冲数和扩展脉冲数以串口的形式发送给计算机,以便于标定和导航计算。

2 硬件电路设计

2.1 恒流源设计

恒流源电路的主要功能是提供基准电流,由于I/F转换电路是根据电量平衡原理进行精确量化,恒流源的变化对转换电路的性能影响最大,是电路设计中最重要的部分之一。对基准电流影响关键的器件是稳压基准源和精密电阻,稳压基准选用LM199AH,其参数如下:电压值为6.8V~7.1V,温度系数为3×10-7~1×10-5,长时间稳定性典型值是2×10-5/1000h。选用RMK5025型精密电阻,其阻值允许偏差在±0.1%,电阻温度特性在±2×10-6。保证恒流源性能稳定,可以大大提高转换电路的温度特性,恒流源输出稳定性及温度特性的提高也有利于I/F电路精度的提高。

2.2 A/D模块

AD976是一个16位逐次逼近型模数转换器,+5V供电,同时外接2.5V基准电源,两者均配备滤波电容,减少电源对采集电压值的影响,最大100mW功耗,采样率为200kHz,电压输入范围为-10V~10V。图4中,3R50用来为补偿内部失调和增益的调整,输出方式为高速并行接口方式输出。

2.3 FPGA及供电模块

FPGA主要完成转换电路所需的各接口时序逻辑电路、JK触发器逻辑电路、分频、计数等功能,简化了硬件电路,同时还具有计数功能可将原始脉冲数和扩展脉冲数以串口的形式发送给计算机,方便对该转换电路的标定。RS422通信所需的波特率由频率为18.432MHz的晶振输入至FPGA分频获得。

如图5所示,FPGA芯片采用双电源供电方式,即内核2.5V和I/O口3.3V分别供电,电源控制芯片为TPS70358。其中,TPS70358的5V电压由外接二次电源提供。为减小供电电源的噪声和干扰对FPGA的影响,在TPS70358的3.3V和2.5V输出引脚附近分别接22μF和47μF的钽电容进行滤波,同时每个电源输入引脚就近串接0.1μF电容滤波。

3 FPGA设计

FPGA模块设计如图6所示。

分频1模块输出频标,分频2模块提供采样时钟,分频3模块提供计数输出时钟;JK触发器模块是根据比较器的输入信号,用硬件语言实现JK触发器的功能;逻辑判断模块的功能是根据JK触发器的输出信号进行正向积分、正向反馈、负向积分及负向反馈4个状态的判别;扩展计算模块是根据电路的状态进行相应的计算输出扩展脉冲;计数模块是对原始脉冲和扩展脉冲进行计数,在计数输出时钟的作用下将数据传给串口通信模块;串口通信模块将原始脉冲和扩展脉冲的个数以数字的形式通过串口发送给计算机;该模块同时实现对A/D的控制、数据采集、运算及扩展脉冲输出。

主要程序流程如图7所示,实际输出脉冲数为理论计算脉冲数减去前一个周期中多放出的脉冲数。

4 试验结果

4.1 原始和扩展比例系数对比

该I/F转换电路的扩展比例系数设计值为原始比例系数值的40倍,但扩展比例系数是通过高速A/D采集积分电压变化计算出的,并通过原始比例系数进行校正,所以扩展比例系数和原始比例系数的比值趋近40,1mA和6mA的比例系数对比如表1所示。

由表1数据可知:扩展比例系数与原始比例系数的比值约为40,表明测试结果与理论设计一致,达到了预期扩大比例系数的目的,同时实现了电路分辨率的提高。其中,波形图如图8所示,与设计预期一致。

表1 X通道电路原始比例系数和扩展比例系数对比

4.2 线性度及重复性

将电路板置于55℃恒温箱中,对电路进行通电并保温30min,电压测量采用安捷伦3458A,输入电流用5700A,测得该电路板的线性度如表2所示。

表2 3个通道线性度

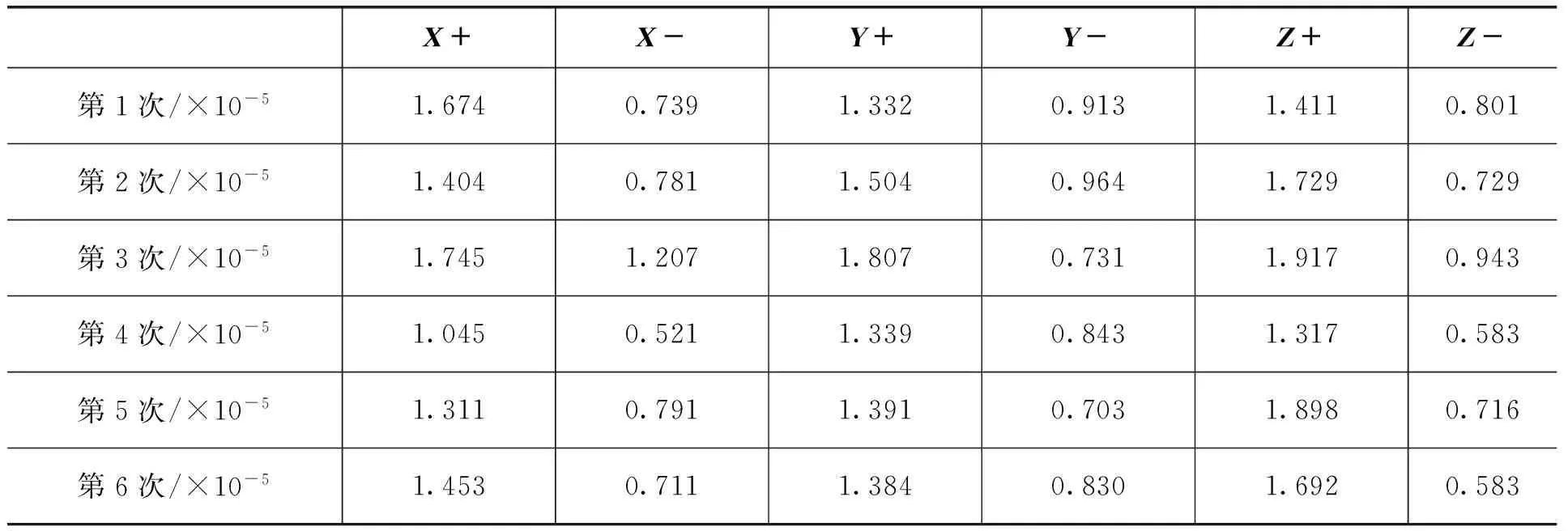

经过试验测试验证,该I/F转换电路的3个通道的线性度均能达到2×10-5以内,满足任务使用需求。同时,对电路板进行重复性测试,表明电路板重复性良好,重复性测试数据结果如表3所示。

表3 3个通道线性度

4.3 比例温度系数测试

通过对I/F电路进行温度设定,选择25℃、35℃、45℃、55℃、65℃五个温度点进行测试。

保证所有测试条件一致,仅改变电路单板测试时的温度,对电路输入±1.25mA的电流,以25℃时的比例系数为基准,其余各温度点比例系数的温度系数结果如表4所示。

表4 比例系数温度特性

结果表明以25℃为基准,电路在所选4个温度点的温度系数均优于5×10-6,属较高精度。

4.4 稳定性和分辨率

4h稳定性测试条件为:在55℃温箱中,温度稳定后通电,分别提供给电路板0mA和±1.25mA电流,测量电路的稳定性,分别如图9~图11所示。

由图9~图11可知,每10s零位极值最大变化量为2个,零位均值为0.109个,零位稳定性优于2×10-7。在±1.25mA电流输入时,比例系数扩大40倍后,其极值变化噪声相比原始比例系数噪声扩大了7倍,所以其有效分辨率提高了约5.7倍;同时扩展比例系数1σ稳定性为1.71×10-6,而原始比例系数为1.05×10-5,实现了比例系数分辨率和稳定性提高的预期。

5 结论

本高精度I/F电路方案在任务需求牵引下,通过对经典I/F 转换电路改进设计,在满足线性度和稳定性的前提下,实现转换电路比例系数的提高,更加精确实时地传递出加速度计的真实输出,同时,较同类其他大比例系数I/F转换电路节省了器件,进一步降低了成本。综上所述,该方案满足任务需求,同时可适用于其他更广泛的应用当中。

[1]宋雪杰, 王晓东, 韩军海. 电流/频率转换类型综述[J].导航与控制, 2009, 8(1):31-38.

SONG Xue-jie, WANG Xiao-dong, HAN Jun-hai. The analysis of the type of the current/frequency converter [J]. Navigation and Control, 2009, 8(1):31-38.

[2]吴南涛, 邢京慧, 王建国.Σ-Δ型模/数转换方式地研究[J].导航与控制, 2011, 10(1):41-44.

WU Nan-tao, XING Jing-hui, WANG Jian-guo. Study on theΣ-Δ ADC.[J]. Navigation and Control, 2011, 10(1): 41-44.

[3]张天光.捷联惯性导航技术(第2版)[M].北京: 国防工业出版社, 2007.

ZHANG Tian-guang. Strpdown inertial navigation techno-logy (2th) [M].Beijing: National Defense Industry Press, 2007.

[4]孟俊芳, 鲁浩, 张彦.弹载开环光纤陀螺V/F变换器设计[J].电光与控制, 2009,16(5):90-92+96

MENG Jun-fang, LU Hao, ZHANG Yan. Design of a V/F converter used in missile-board O-FOG [J]. Electronics Optics & Control, 2009, 16(5):90-92+ 96.

[5]牛清红, 张春熹, 宋凝芳. 用A/D 和FPGA实现的加速度计数据读出系统[J].中国惯性技术学报, 2006,14(1):63-66.

NIU Qing-hong, ZHANG Chun-xi, SONG Ning-fang. Output system of high precise & wide measuring range accelerometer [J].Journal of Chinese Inertial Technology, 2006, 14(1):63-66.

[6]王晓东, 黄伟, 车鹏宇, 等. 高分辨率电流频率转换电路设计[J].导航与控制,2014,13(5):28-31.

WANG Xiao-dong, HUANG Wei, CHE Peng-yu, et al. The high resolution design of the current/frequency converter [J]. Navigation and Control, 2014, 13(5):28-31.

[7]陆元九. 惯性器件(下) [M]. 北京: 中国宇航出版社, 2009.

LU Yuan-jiu. Inertial device(2rd) [M].Beijing: China Aerospace Press, 2009.

[8]张亚薇, 张志文.一种高精度I/F变换器的研究[J].生命科学仪器,2009, 7(12):52-54.

ZHANG Ya-wei, ZHANG Zhi-wen. A kind of high-precision I/F converter [J].Life Science Instruments, 2009, 7(12):52-54.

[9]胡少青.高精度加速度计的数字读出电路设计与实现[D].北京航空航天大学, 2001.

HU Shao-qing. The design and realization of high preci-sion accelerometer data acquisition circuit [D]. Beijing University of Aeronautics and Astronautics, 2001.