基于FPGA的风电机组振动监测系统设计

2018-04-11邓艾东

龙 磊,邓艾东

(东南大学火电机组振动国家工程研究中心,江苏 南京 210096)

0 引言

风力发电机组单机容量向兆瓦级以上的发展,对风力发电设备的可靠性和安全性提出了更高的要求。大型风电机组工作环境恶劣,风机传动系统故障率高。目前,通常采用定期检修方式对其进行维护。但由于机组自带的运行监控设备不足,很难准确掌握风电机组传动系统的运行状况。这往往导致系统部件发生损坏时无法及时排除故障,大大降低了设备的利用率[1-2]。振动信号在众多特征信息中能够有效判断风机传动系统的运行状态[3-5]。配备完善的振动状态监测系统,对于及时发现传动系统故障、合理安排检修及提高机组的经济效益具有重要意义。

本文以风机传动系统为监测对象,设计了一种以ARM为主控制器、FPGA为从控制器的风电机组振动监测系统。利用FPGA对数据的高速处理能力和增强型直接内存存取(enhanced direct menory access,EDMA)的高速数据传输能力,解决了风电监测系统对采集数据的实时获取和保持数据准确性的问题。本文重点介绍了FPGA逻辑控制模块。

1 系统总体设计方案

本文研究的风机传动监测系统主要分为两个部分。第一部分主要实现数据的采集、预处理、传输、存储等功能,包括模拟信号处理、FPGA电路逻辑控制及ARM嵌入式平台等模块。第二部分为应用层软件程序。本系统采用基于TCP/IP的C/S软件体系结构:整个硬件平台完成对数据的采集、服务请求和数据时/频分析;上位机作为客户端,对采样速率、周期、点数、通道等参数进行控制;应用层软件和上位机之间的通信选用TCP/IP通信协议。系统总体框架如图1所示。

图1 系统总体框架示意图

2 系统硬件设计

2.1 模拟信号预处理

本系统将风机传动系统的振动信号作为监测参数,并行采集传输8通道振动信号。系统可支持涡流、速度、加速度3种类型传感器的接入。每个通道都包括间隙电压、位移、速度、加速度等信号的调理电路。系统能根据传感器的类型自动选择相应的预处理电路[6]。为了提高信噪比,信号采用差分输入。当采用电涡流传感器时,信号接入前要进行分压处理,然后对信号进行差分放大,经低通滤波后获得间隙直流电压信号,以判断涡流传感器的静态安装位置。接入加速度传感器时,先通过8阶抗混叠低通滤波器和2阶高通滤波器,获得加速度信号;再分别通过一次积分和二次积分得到速度和位移信号。每次积分前都需要进行隔直处理,以免发生积分偏置。

每个通道输入信号经过预处理后,得到振动加速度、速度和位移信号。信号被接入模拟选择开关DG409DY-E3。通过FPGA控制模拟选择开关选择信号,并将信号送入8通道16位高速A/D转换器AD7606进行转换,从而实现了8通道输入信号的并行采样。涡流传感器间隙电压是慢变信号,采用普通A/D转换器即可。1个通道的振动信号预处理框图如图2所示。

图2 振动信号预处理框图

传动系统低速轴或高速轴的转速可通过测速齿轮来测量。转速脉冲接入FPGA进行数字倍频后,可实现振动信号滤波中心频率的自跟踪和振动信号A/D转换频率的自适应。

2.2 FPGA模块设计

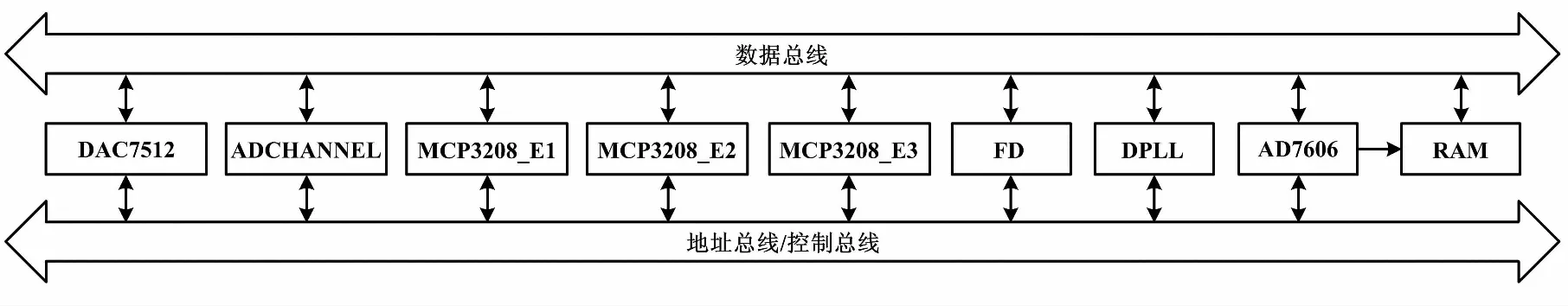

图3 FPGA功能实现框图

数字锁相环模块的主要功能是实现N倍频,即使输出信号的频率Fout是输入信号Fin的N倍。数字锁相环是一个相位反馈控制系统,其输入信号通常为脉冲信号,通过与提取的参考相位比较,使最后得到的分频与所需的频率十分接近[8-9]。通过FPGA内部的数字锁相倍频器,产生振动信号A/D转换的触发信号和抗混叠滤波器Max291的时钟频率。将输入频率为f的转速脉冲信号作为数字倍频器的输入,通过数字倍频器自动输出128f(或其他需要的倍频)脉冲,并将其作为A/D触发信号,再由A/D转换器对8通道振动信号进行同步采样。由于数字倍频器能提供满足精度要求的转速脉冲倍频信号,从而保证了精确的整周期采样。8路采集通道分别采样1 024点后自动缓存数据,由软件输出控制指令,从缓存器读取采样数据。同时,将该转速脉冲信号作为FPGA中另一个数字倍频器的输入,并输出所需的倍频信号作为滤波器芯片Max291的时钟频率,从而实现滤波中心频率随转速频率变化的自动跟踪功能。

DAC7512模块主要实现对FPGA时钟的分频、数据的同步读写。MCP3208的功能是对采集信号进行A/D转换。AD7606模块主要模拟8路信号,并在采样完成后通过FPGA的控制,将转换的数字量存储到RAM缓存中,供上层及时读取。本系统中,AD7606采用并行数据模式,ncs上升沿将使总线变为高阻态;设模拟输入为±5 V,转换时间为4 μs,采集保持时间为 1 μs,最大吞吐速率为200 Kb/s。AD7606的首要任务是设置采样触发信号和Max291滤波器时钟信号。其代码为如下。

convst<=conv_x when regs_rw(0)(3)=‘1’else cony;

max291_clk(0)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(1)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(2)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(3)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

本文开展农业资源承载力分析主要运用农林牧渔业总产值、粮食总产量、农林牧渔业总产值、农业用水量、总供水量5个评价指标,其数据主要来源于2002—2017年内蒙古统计年鉴、2010—2016年巴彦淖尔市水资源公报。

max291_clk(4)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(5)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(6)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

max291_clk(7)<=conv_e when regs_rw(0)(6)=‘1’else max291_clk_i;

采样触发信号分为外部采样时钟信号conv_x和内部采样时钟信号con_y。寄存器reg_rw(0)(3)存储了AD7606采样信号的具体采样方式:1代表外部采样,0代表内部采样。振动信号采集方式分为有转速和无转速两种,其初始状态由软件设置。运行中,系统可以自动、有效判断转速信号失效状态。当有转速信号时,为防止频谱泄漏,必须进行周期采样(连续采样1 024点),即以外部采样触发方式(conv_x)输出A/D触发信号并控制数据的存储。当无转速或转速失效时,系统自动从有转速采集切换到无转速采集状态。此时为软件触发方式,并由软件产生A/D转换触发信号,由用户设定采样频率,以等时间间隔采集信号。

2.3 ARM与FPGA的数据传输

FPGA与通用存储控制器(general purpose memory controller,GPMC)的连通关系如图4所示。

图4 FPGA与GPMC连通关系图

在本系统中,FPGA与ARM主芯片之间采用EDMA方式进行数据传输。EDMA主要用于控制存储器与存储器、存储器与外设、外设与外设之间的数据传输。其工作流程为:向CPU发出请求,使控制器获得总线控制权;CPU继续执行内部操作,EDMA控制器辅助数据传输,数据传输完成后向CPU发出中断信号,并将总线控制权交还给CPU[10]。ARM嵌入式平台作为本系统的主控单元,其主要功能是完成对A/D采样的数据读取,以及实现FPGA与上位机之间的通信。本系统嵌入式平台选用成都英创的ESM335X系列和开源的嵌入式Linux系统。ESM335X基于ARM Cortex-A8,具有丰富的外设、工业接口、可编程实时单元和工业通信子系统[11]。为实现不同功能,FPGA增设了相应参数寄存器。ARM通过其内部通用存储控制器GPMC端口实现对FPGA相关寄存器的读写,包括FPGA的数据采集速率、倍频等参数的设置。

3 系统软件设计

本系统采用C/S体系结构,软件设计平台为Linux操作系统,编程软件为Eclipse IDE for C/C++,选用C语言作为编程语言。系统软件的主要功能是采集振动信号,实现与上位机的通信,并将数据传送给上位机。当上位机向应用层软件发送数据时,应用层软件对上位机指令进行监测,有利于接收处理信号。应用层软件与上位机之间采用TCP/IP通信协议,通过Linux中的套接字(Socket)通信。套接字包含3部分:将数据发送到目的端的IP地址、传输层协议和数据传送使用的端口号[12-14]。结合这3个参数,同时绑定一个Socket,就能实现应用层与传输层之间的数据通信。具体创建套接字,设置IP地址、协议和端口号的程序代码如下。

if((listenfd=socket(AF_INET,SOCK_STREAM,0))==

-1)

{

perror(">>>create socket error ");

exit(-2);

}

int opt=SO_REUSEADDR;

setsockopt(listenfd,SOL_SOCKET,SO_REUSEADDR,&opt,sizeof(opt));

//reuse address in bind

bzero(&server,sizeof(server));

server.sin_family=AF_INET;

//Use TCP

server.sin_port=htons(PORT);

server.sin_addr.s_addr=htonl(INADDR_ANY);

采用创建子进程的方式,对上位机指令进行实时监测。应用层总体实现流程如图5所示。

图5 应用层总体实现流程图

4 结束语

本文将振动信号作为监测参数,采用ARM和FPGA作为硬件核心,构建了风电机组传动链振动状态监测系统。

系统软件层作为客户端,实现了传感器类型、采样速率、采样周期等相关参数的控制以及与上位机的通信功能;系统硬件部分则作为下位机,对振动信号进行采集、处理、存储与传输。利用FPGA强大的逻辑和数据处理能力,实现了振动信号全自动采集、振动信号滤波中心频率的自跟踪与A/D转换速率的自适应。通过EDMA,实现了FPGA与ARM之间的数据高速传输,使得本系统在具备大量数据处理能力的同时,保证了数据的稳定和准确性,可满足大型风电机组振动状态实时监测和分析的需求。

参考文献:

[1] 王效,刘晓光.基于ARM的风电齿轮箱振动监测系统设计[J].发电技术,2013,34(2):16-19.

[2] 程启明,程尹曼,王映斐,等.风力发电系统技术的发展综述[J].自动化仪表,2012,33(1):1-8.

[3] 李勇,胡育文,黄文新,等.变速运行的定子双绕组感应电机发电系统控制技术研究[J].中国电机工程学报,2008,28(20):124-131.

[4] 夏长亮,张茂华,王迎发,等.永磁无刷直流电机直接转矩控制[J].中国电机工程学报,2008,27(3):25-35.

[5] 杨建刚.旋转机械振动分析与工程应用[M].北京:中国电力出版社,2007.

[6] 路遥,江汉红,芮万智.基于ARM的风电机组远程监测系统的设计[J].船电技术,2015,66(2):9-12.

[7] 王慧中,沈燕妮.基于DSP+ARM的风电机组状态监测系统研究[J].电气自动化,2011,33(6):26-28.

[8] 韩宏宇.基于FPGA的风电监测系统数据采集单元设计[D].北京:北京化工大学,2011.

[9] 张夏疆,田新启.CPLD数字倍频原理在旋转机械振动信号采集中的应用[J].工业控制计算机,2009,22(5):9-10.

[10]但永平,彭洪涛,王东云,等.EDMA在图像数据快速传输中的应用[J].液晶与显示,2013,3(1):99-104.

[11]TI.AM335X:ARM Cortex-A8微处理器开发方案[J].世界电子元器件,2014(3):19-21.

[12]韦东山.嵌入式Linux应用开发完全手册[M].北京:人民邮电大学,2008.

[13]ROBERT L.Linux内核设计与实现[M].陈莉君,康华,译.北京:机械工业出版社,2011.

[14]JONATHAN C,ALESSANDRO R,GRGE K H.Linux设备驱动程序[M].北京:中国电力出版社,2006.