数字通信信号载频实时估计算法与实现

2018-04-03中国人民解放军32090部队安佰强董旭明杨铁新

中国人民解放军32090部队 安佰强 周 强 董旭明 杨铁新

0 引言

载频是数字通信信号最基本的参数之一,对载频进行实时、准确的估计,是对通信信号进行调制识别和分析,对通信设备进行有效侦察和干扰的前提。关于载频的估计,已经有很多成熟的算法,但这些算法不是需要调制类型等先验知识,就是计算方法复杂,不利于进行实时估计。本文通过对常用的时域载频估计法和频域载频估计法进行对比分析,并对频域载频估计法中的频率居中法进行改进,以最少的计算资源获得最大的载频估计精度,并且非常容易在FPGA上实现。

1 基本原理

时域法载频估计,通过计量一定数量的信号周期总共占有多长时间来推算载波的频率。设对接收到的信号以fs的频率进行采样,数出一段信号极性改变n次的时间,设这段时间有m个采样点,即这段时间为m/fs,则信号的载频可以估计为:

由于m为整数个采样时钟周期,因此对时间计量的最大精度为一个采样时钟周期,所以载频估计的相对精度为,当m较小时,误差会很大。

频域法载频估计,对接收到的信号做FFT变换,将时域信息变换成频域信息。频谱上的峰值对应的频率点即为信号载频。设采样频率为fs,傅立叶变换点数为N点,频谱峰值对应频点为m,则载频为:

利用这种方法估计载频,理论上的估计精度为:

随着FFT变换点数N的增加,载频精度也会随之提高。但实际上,这种方法没有充分利用其它频点的信息,在有噪声时很难精确估计载频。

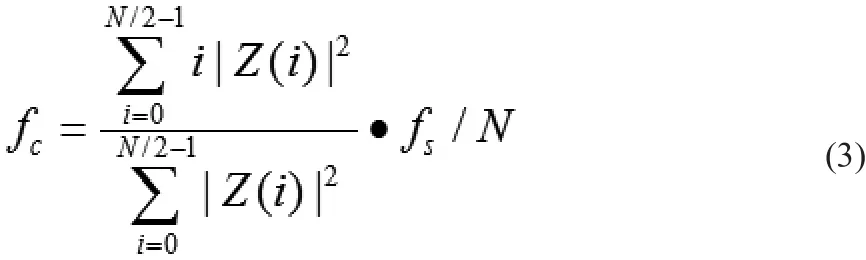

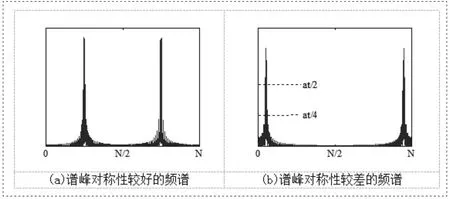

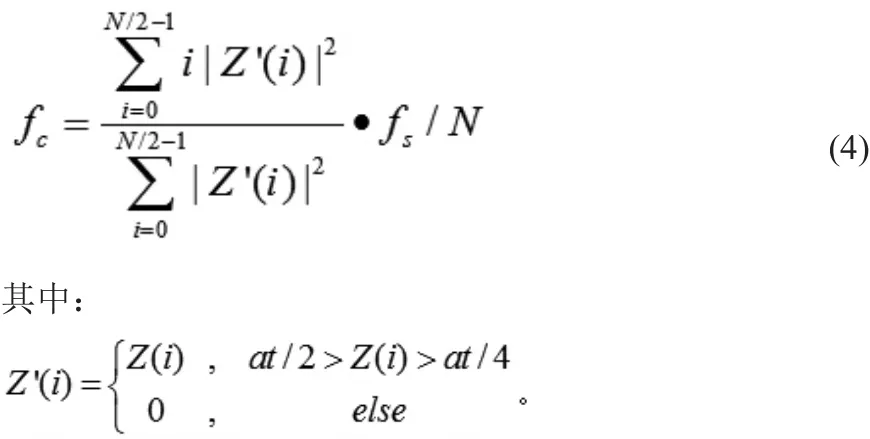

频率居中法是基于上述方法的一种改进,它充分利用了各个频点所携带的频率信息,具有精度高、受噪声影响小的特点。其计算公式为:

式中,Z(i)为信号的FFT变换,fs为采样频率,N为FFT变换点数。

频率居中法实际上是依据频谱峰值左右的对称性来估计载频的。这种方法虽然提高了估计精度和抗噪声能力,但同样具有一定的局限性。如图1所示,当频率峰值接近频谱边缘时,频谱峰值的对称性会遭到破坏,从而产生较大误差。

图1 频率居中法载频估计

改进频率居中法,令at =max(Z),以at/ 2和at/ 4为门限,截取频谱谱峰对称性较好的中间一段数据,再按(3)式进行计算,可表示为:

采用这种方法,在频谱谱峰对称性受到破坏的情况下,仍能够比较精确的估计出信号的载波频率。

2 算法仿真

以QPSK调制信号为例,在不同的噪声条件下分别用两种方法对QPSK调制信号进行载频估计。

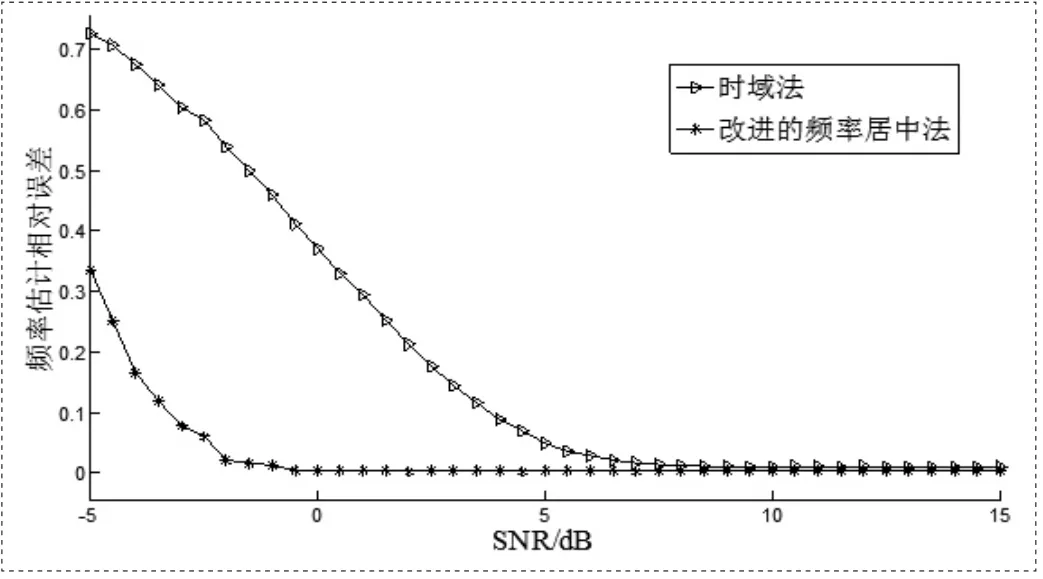

假设信号载频fc=25MHz,码元速率fd=1MHz,采样频率fs=100MHz,每个噪声条件下积累50次估计结果并求平均值。仿真结果如图2所示。

图2 时域法与改进的频率居中法载频估计抗噪性能比较

通过仿真对比分析可得,在较高的信噪比下,时域法和改进的频率居中法对信号载频的估计精度相差不大,但随着信噪比的降低,时域法估计误差明显增大,而改进的频率居中法变化不大。在信噪比低于0dB的情况下,频率居中法仍可以较好的估计出载波频率。

3 在FPGA上的实现

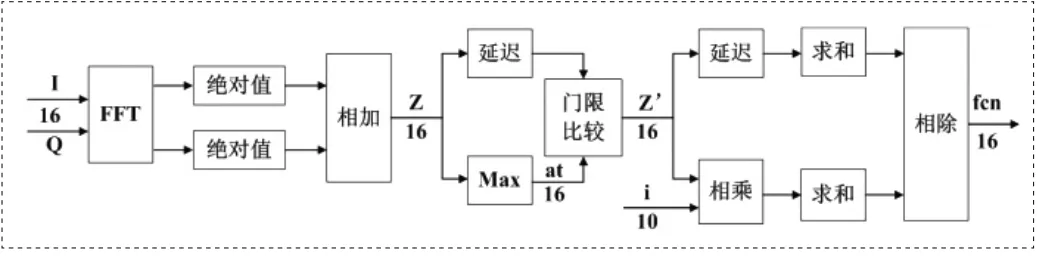

数字通信信号经过采集处理以后,以I、Q两路正交信号的方式传输到FPGA上,其中每路信号以16bit有符号二进制数表示。载频估计算法的实现流程如图3所示。图中对应变量符号的数字代表变量符号所使用的二进制位数。

由图3所示中可以看出,整个计算流程主要包括一个FFT模块、三个乘法模块和一个除法模块,这些都是占用FPGA资源较多的模块,可以直接使用Xilinx提供的IPCore,其中FFT的IPCore设置为流水线工作模式,并选择“Scaled”。其它IPCore都支持流水线处理方式。

图3 载频估计流程图

图中输出结果fcn对应为FFT的频谱点数,换算成载频为。在本系统中,FFT设置为2048点,即N= 2048,采用改进的频率居中法来估计载频,误差应该小于fs/N,继而推断出可以采用16bit二进制数表示fcn,其中高11bit代表整数部分,低5bit代表小数部分。对整数和小数位的设置可以通过除法的IPCore完成。

载频估计的输入是两路正交I、Q信号,各用16bit二进制符号数表示,经过FFT傅立叶变换求出频谱后,用32bit二进制无符号数表示频谱幅度Z。i的最大取值为N/ 2-1,即1023,可以用10bit二进制无符号数表示。因此,乘法模块Z(i)●i的两路输入信号的位宽分别为32bit和10bit。在之后的求和过程中,信号的位宽还会增加,除法模块的输入位宽也会随之增大。这些增加的位宽超出了计算结果fcn的需要,使得采用的乘法和除法IPCore浪费了大量的资源。

可以通过优化算法来节约这部分资源。载频的估计,关键在于求频谱谱峰所对应的频点位置,对谱峰的幅度并不关心。因此,在计算频谱时可以不使用占用资源较大的乘法器,而直接将经过FFT变换的两路正交信号取绝对值相加。通过这种方法不仅节约了资源,而且降低了数据位宽,进而降低了后续计算模块使用的资源。优化后的算法流程如图4所示。

图4 优化的载频估计流程图

优化前后使用资源的情况如表1所示。

表1 载频估计算法优化前后资源使用比较

从表中可以看出,对算法做适当的优化,可以节约大量的片上资源,并降低算法的实现难度。在ISE11.3版本中的除法IPCore,被除数和除数位宽最大为32bit。因此需要对输入的位宽做取舍,选择被除数位宽32bit,除数位宽22bit。虽然优化前后的除法IPCore使用资源相同,但是优化前除法输入位宽舍去的比优化后的要多,其计算精度不如优化后的除法模块。

4 结论

本文提出的优化的频率居中法可以在较高的信噪比下对通信信号进行载频实时估计,在FPGA中实现时,能够降低算法实现难度,节约片上资源。

[1]李坡.宽带数字侦察接收系统关键技术研究与实现[D],长沙国防科学技术大学博士学位论文,2010.

[2]阙隆树.数字通信信号自动调制识别中的分类器设计与实现[D].西南交通大学硕士学位论文,2010.

[3]胡建伟,汤建龙,杨绍全.使用小波变换的MPSK信号调制类型识别[J].电路与系统学报,2006,11(3):130-134.

[4]王立乾,赵国庆,郑文秀.基于现代谱估计的PSK信号频率估计方法[J].现代电子技术,2003,23:44-47.