一种应用于高精度数模转换器的LVDS信号接收器的设计

2018-03-09戈益坚徐静

戈益坚+徐静

【摘 要】LVDS信号是一种低功耗、高速度的信号传输技术,其具备低功耗以及低噪声的优良特性,非常适合作为高精度数模转换器的输入信号。本文介绍了一款高精度数模转换器内部的LVDS信号接收器电路,分别介绍了信号接收器的预放大器、电压比较器、整形缓冲器电路的设计,并对系统整体进行了功能性验证。

【关键词】LVDS信号;共模抑制比;差分放大器

中图分类号: TN792 文献标识码: A 文章编号: 2095-2457(2017)35-0086-002

An LVDS Signal Receiver Designed for High Precision Digital Analog Converter.

GE Yi-Jian XU Jing

(Jiangsu Information Vocational and Technical College,Wuxi Jiangsu 214153,China)

【Abstract】LVDS signal is a kind of low-power, high-speed signal transmission technology. It has the characteristics of low power consumption and low noise and is very suitable for the input signal of high-precision digital-to-analog converter. This paper introduces a LVDS signal receiver circuit inside a high precision digital-to-analog converter, introduces the design of signal receiver pre-amplifier, voltage comparator, shaping buffer circuit, and the functional verification of the whole system.

【Key words】LVDS signal;Common mode rejection ratio;Differential amplifier

1 LVDS信号

传统的高速数字采集系统的信号一般采用LVTTL信号,LVTTL信号在传输过程中存在信号传输速度慢、误码率高、抗串扰能力弱、功耗较高等缺陷,为了克服这一系列的缺陷,研究人员开始研发新一代的低电压差分信号传输标准,LVDS(Low-Voltage Differential Signaling)信号标准应运而生。LVDS信号标准是由美国国家半导体公司(National Semiconductor)提出的一种低功耗、高速度的信号传输技术,LVDS信号一般采用1.2V的偏置电压作为基准,提供较低的电压摆幅(一般为350mV)以及较低的低的驱动电流(一般为3.5mA),在一对线路上传输差分信号,其最高传输速率可达3.1Gbps,同时由于其低电压摆幅以及低驱动电流的特性,使其具备低功耗以及低噪声的特性。由于LVDS信号具备以上的优点,所以非常适合作为高速高精度数模转换器的输入数字信号标准。

2 LVDS信号接收器电路设计

LVDS低压差分信号经过数模转换器芯片内部集成的LVDS信号接收器处理后转换为CMOS数字信号,供后续电路模块进行处理。LVDS信号接收器电路由预放大器、电压比较器、整形缓冲器三个模块构成,基于CSMC 0.18um CMOS工艺所设计的LVDS信号接收器电路如图1所示。

LVDS输入信号首先加在由P1、P3、P3、M1、M2、M3、M4这七个MOS管所构成的与放大器电路的输入端DATA_P、DATA_N两端,该运算大器电路采用的是一种Lee负载的差分放大电路结构,其中P1为一个PMOS电流源,当栅极电压V_BIAS为0时,可以为差分放大器提供1mA的输出电流。M1、M2、M3、M4这4个NMOS管构成了一个LEE负载结构,这4个MOS管负载均采用二极管接法,二极管接法的MOS管的小信号等效电阻阻值为

req=■(2)

根据以上模型,当输入信号为差模小信号时,得到LVDS接口电路预放大器电路的差模小信号等效电路模型如图4所示。

图2中,vid/2为输入差模小信号,gmP2为P2管的跨导,roP2为P2管的小信号等效内阻,gmM1、gmM2分别为M1、M2管的跨导,roM1、roM2分别为M1、M2管的小信号等效内阻。vod/2为差模输出信号。可以计算出当输入信号为差模小信号时,LVDS预放大器的差模输出信号的表达式为:

■=g■·■(3)

因为M1管与M2管的设计参数完全一致,所以可得:

gmM1=gmM2(4)

roM1=roM2(5)

将式(4)、(5)代入式(3)可得LVDS预放大器的差模小信号增益Avd为:

Avd=■=■(6)

当输入信号为共模小信号时,得到LVDS接口电路预放大器电路的小信号等效电路模型如图5所示。

图3中,roP1为P1管的交流小信号等效电阻,vic为共模输入小信号,voc为共模输出小信号。可以计算出当输入信号为共模小信号时,LVDS预放大器的共模输出信号的表达式为:

voc=■(7)

將式(3-4)、(3-5)代入式(3-7),可得

voc=■(8)

LVDS预放大器的共模小信号增益Avc为:

Avc=■=■(9)

由式(6)、(9)可以计算出LVDS预放大器的共模抑制比(Common Mode Rejection Ratio,CMRR)的表达式为:

CMRR=■=■(10)

而传统的电流镜负载结构的差分放大器该的共模抑制比的表达式为;

CMRR=■=(1+2gmProP1)gmN(roP||roN)(11)

式(11)中,gmP为PMOS管P2、P3的跨导,gmN为NMOS管M1、M2的跨导,roP为PMOS管的小信号等效电阻,roN为NMOS管的小信号等效电阻。

将式(10)与式(11)对比可以发现,采用Lee负载结构所设计的预放大器的共模抑制比比采用电流镜负载的差分放大器大一个数量级,从而对LVDS信号输入端的共模噪声有更好地抑制作用。

输入信号经过预放大器的放大之后双端口输出至由P4、P5、M5、M6这四个MOS管构成的电压比较器,电压比较器电路主要实现以下三个功能:

(1)将预放大器双端口输出的信号进一步放大,提升电压比较器的比较精度;

(2)将双端输入信号转成单端输出信号;

(3)将输出最大电平从3.3V转换为1.8V;

由于电压比较器输出的信号波形的摆幅、上升沿下降沿的陡峭程度还不能达到CMOS数字信号的要求,所以需要在电压比较器的输出端接一个又两级CMOS反相器构成的整形缓冲器,由于CMOS反相器可以将输入端缓慢变化的波形快速翻转,从而大大地降低输出端波形的输出上升时间以及输出下降时间,整形缓冲器的电路结构如图5所示。

3 LVDS信号接收器仿真

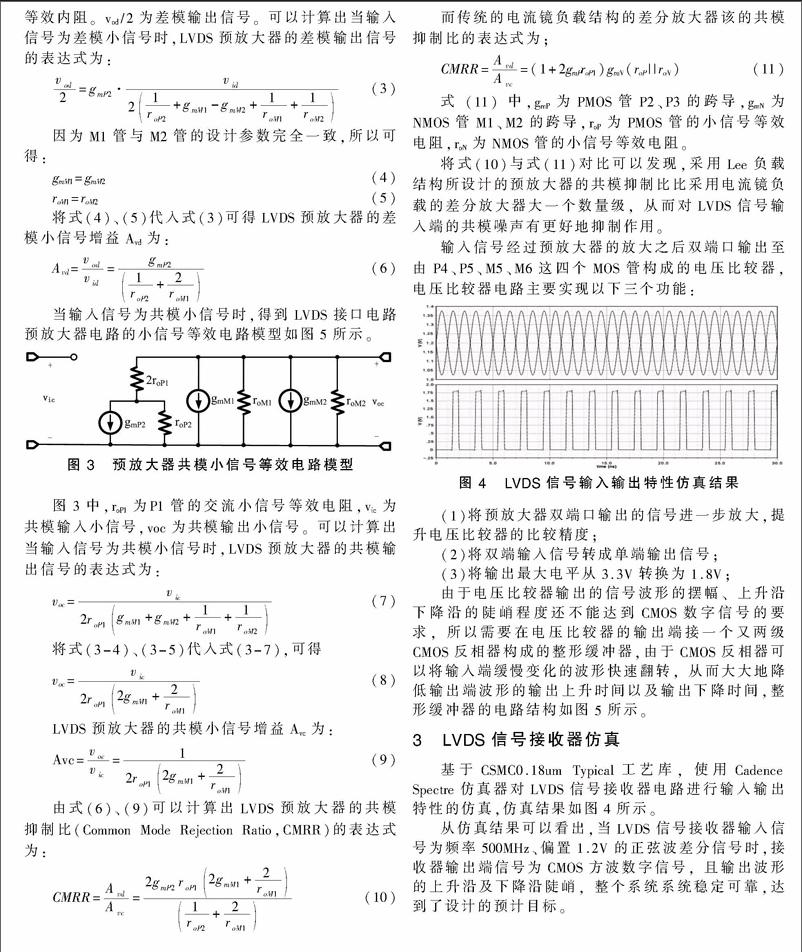

基于CSMC0.18um Typical工艺库,使用Cadence Spectre仿真器对LVDS信号接收器电路进行输入输出特性的仿真,仿真结果如图4所示。

从仿真结果可以看出,当LVDS信号接收器输入信号为频率500MHz、偏置1.2V的正弦波差分信号时,接收器输出端信号为CMOS方波数字信号,且输出波形的上升沿及下降沿陡峭,整个系统系统稳定可靠,达到了设计的预计目标。endprint