基于CPCI总线的卫星和地面设备交互方法

2018-03-08王红光

王红光,穆 强,刘 博

(北京空间飞行器总体设计部,北京 100094)

0 引言

本文介绍了一种在卫星地面测试阶段通过标准CPCI机箱配置数据传输模块实现卫星数据传输的应用方法,将1553B总线接口介入星载数据网络,直接获取卫星多系统的下行数据,实时性显示数据,弥补了远距离测控通信信道余量和容量的不足,对于数据变化快的数据能够实时采集和传送,提高了数据获取的速率。同时,将RS-422接口与星载设备直连模式,完成上行数据注入及指令发送和数据下行,保证了数据信息的快捷传送,保证高可靠的数据通信和安全性要求,可以缩短测试过程中应急响应时间。

该种数据传输方式保证了遥控及遥测信道的信息快速、可靠传送,减少延时传送带来的漏判等情况,对于多个分系统或者子系统协同测试的情况下,发现问题后能够迅速定位,作为排查问题的方式,对于有效载荷等数据量大的终端数据下行,为其提供了上、下行信道及其它系统间信息交换的快速通道,遥测更新速率快,在地面电性能综合测试时作为判读手段,提高了测试效率。

1 系统设计

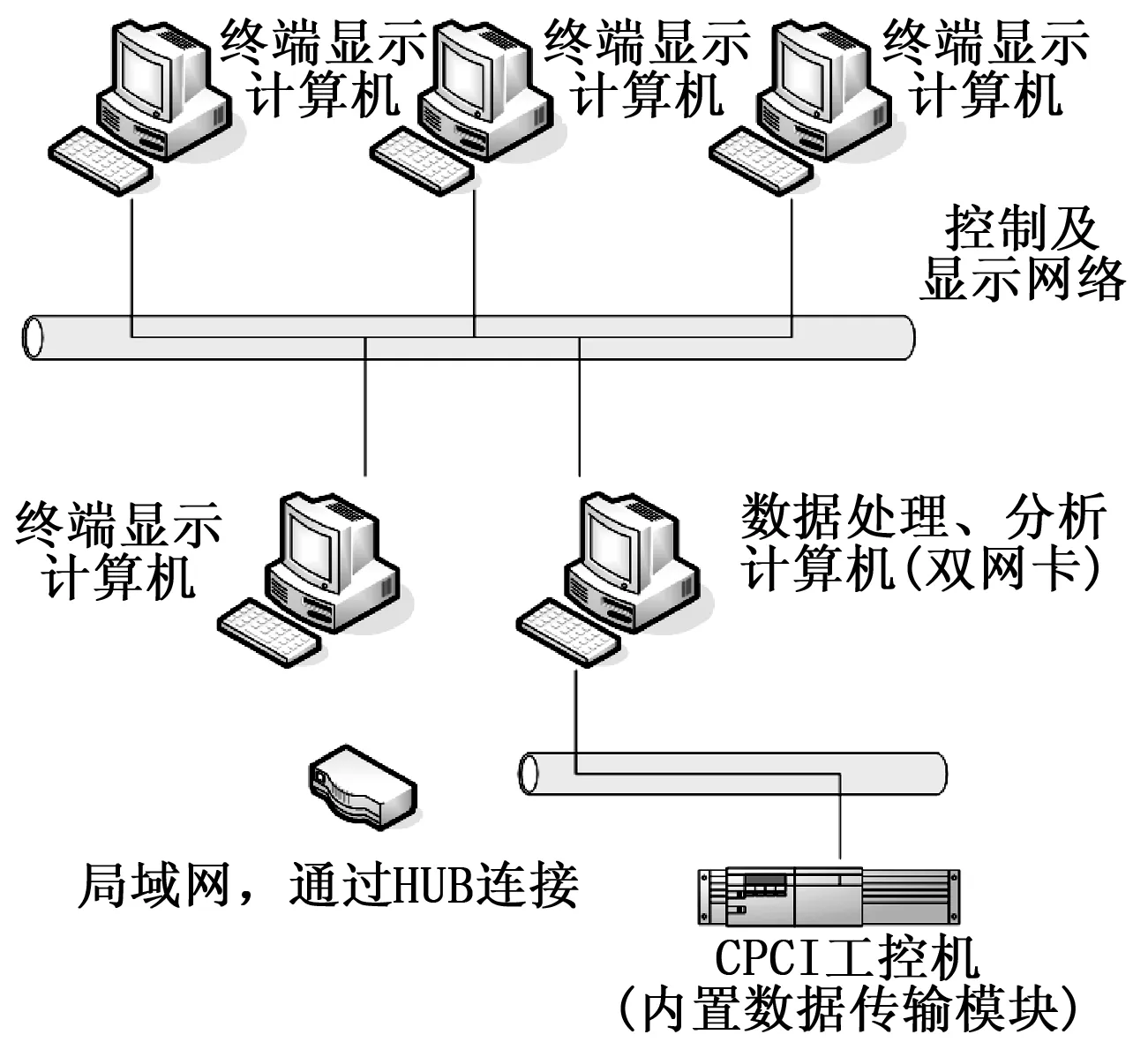

本系统采用上、下位机的网络结构,上位机采用通用计算机,配置双网卡接收下位机数据,同时作为数据处理和分析计算机,下位机由CPCI工控计算机及数据传输模块组成。上位机运行主控监视、显示软件,下位机远程运行工控系统软件及数据传输模块嵌入式软件,如图1所示。

图1 数据传输应用系统关系图

在本系统中,所有采集的原始数据由工控机按照协议格式存储。数据传输模块作为CPCI从设备将采集的卫星数据传送至CPCI主设备,进行组帧、打包并通过以太网发送至上位机,由上位机按照网络协议发送至远程终端用户进行显示、数据分析、处理以及故障诊断,同时可完成打印和存档操作等,或者根据用户需求远程设置1553B总线接口工作模式,完成总线接口控制、监听、仿真,实现数据定制传输和状态控制。

数据传输模块装载在下位工控机中,通过以太网由上位机远程控制实现在线测试,控制完成1553B接口的BCMTRT多种功能转换,进行不同功能模拟的动态设置,充分利用并节省硬件资源,完成1553B总线在线控制、监听和仿真功能,该3种功能的转换通过上位机根据需求而进行工作模式的切换设置。

-总线控制器(BC),由上位机控制启动与被测RT端串行总线通讯,检验RT总线通讯数据的正确性。

-远置终端(RT),模拟一个或多个连接在总线终端上的数据特性,可以灵活的进行远程终端的模拟,模拟31个远置终端,按照1553B总线远置终端的特性进行数据设置,上位机可以对仿真的RT终端的任何数据进行修改,并可根据总线通讯协议对仿真的RT地址、子地址和接收/发送信息有选择的显示。

-总线监视器(MT),监听所有或部分总线终端通讯信息流,由上位机控制监听终端的操作,并传输及显示其监听到的数据。

同时具有多种数据采集传输功能,完成外部1553B总线接口和多路RS-422接口数据传输,并通过以太网将获取的1553B总线原始数据及下位机工作状态信息发送至上位机。2种接口均为通用接口标准规范,采用1553B双余度结构多路传输数据总线,设计为变压器耦合接口方式,接口电路与被测件隔离,保证电气接口的安全性,RS-422总线是一种平衡通信接口,差分传输方式可实现数据远距离传输,采用双线传输提高了抗共模干扰的能力。

按照卫星系统应用的需求,可靠性和安全性是重点考虑的因素,在本系统中,工控机采用低电压隔离供电方式,将220 V交流电压转换为直流24 V电压再供给工控机,实现电源供电隔离,保证被测设备安全性。

2 数据传输模块硬件实现

数据传输模块是基于CPCI接口的标准板卡,数据传输模块板卡插装在4U或者6U的CPCI工控机箱中,板卡尺寸为233.35 mm×166 mm,主要实时接收外部1553B串行数据总线数据和RS-422串行总线数据并进行传输,硬件模块主要由中央控制器、CPCI总线控制器、FPGA、1553B总线控制器、RS-422总线控制器、双口RAM等组成。中央控制器完成外部数据流的接收与处理,双口RAM用于暂存数据,实现原始数据与状态设置等数据交换,各专用接口芯片配置应用寄存器和数据缓存区等,由软件设置状态信息,FPGA芯片实现逻辑控制及时序匹配。数据传输模块硬件结构如图2。

图2 数据传输模块硬件结构框图

2.1 中央控制器设计

为了适应数据传输速率的需要中央控制器选用W77E58控制器芯片,系统时钟12 MHz,片内程序区为32 K字节,该芯片运行速度为传统8051系列的1.5~3倍。中央控制器接外部中断源,以接收外部中断方式控制数据接收。外部配置8 K字节RAM区和8 K字节PROM区。所有控制管脚接FPGA芯片管脚上,根据使用需要,在FPGA内部通过编程对各个功能管脚进行灵活处理和使用。

2.2 CPCI总线控制器设计

数据传输模块与上位机的数据交互通过标准化的CPCI总线来实现,CPCI接口可采用可编程逻辑器件或者专用CPCI总线接口芯片完成,考虑开发的复杂性和系统的稳定性,采用低成本和通用的商用接口芯片,CPCI总线控制器芯片选用PCI9052接口芯片,该芯片是PLX技术公司开发的PCI协议从模式接口芯片,是低成本、低功耗器件,可以完成局部总线到PCI总线的快速转换,扩展适配板卡,部分引脚可直接连接到2 mm密度针孔连接器上,另有AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、STOP#、LOCK#、IDSEL、DEVSEL#、PERR#、SERR#以及RST#管脚接10欧姆的排阻匹配信号,以避免信号的干扰。

CPCI总线控制器包含一个上电时自动加载配置信息的串行EEPROM接口,配置芯片选用ATMEL的93LC46B(64×16 bitEEPROM)器件,内部具有上电、掉电数据保护电路,可使存储的数据不丢失,采用烧写串行EEPROM方法,使用芯片烧写器将数据写入93LC46B,烧写内容为初始化配置参数以及地址空间信息,包括CPCI配置寄存器参数,生产商ID、器件ID号、类码子系统ID号和子系统生产商ID号等。

2.3 FPGA设计

FPGA主要完成对各接口的逻辑和时序控制。包括地址译码、数据锁存、读写时序控制电路、时钟分频及复位控制电路,实现与CPCI高速总线间的数据通信。FPGA可迅速而灵活的修改和进行资源配置,方便了设计人员的配置,减少了逻辑器件,节省了板卡空间,在FPGA管脚排布上尽量将所有的功能管脚连接到FPGA上,在FPGA内部对不使用的管脚进行处理。FPGA芯片选用Altera公司生产的FLEX10K20QC208,该芯片能够提供20万门电路,FPGA功能如图3所示。

图3 FPGA功能框图

在FPGA调试阶段,采用JTAG测试口下载FPGA调试程序,在JTAG配置引脚接上拉1 K欧姆电阻,调试结束后,采用烧写器写入程序到EPROM芯片,固化FPGA程序,系统启动时按照时序自动从EPROM中读取FPGA的配置数据。

2.4 1553B总线电路设计

采用符合GJB 289A-1997《数字式时分制指令/响应型多路传输数据总线》规范的标准1553B总线接口,1553B总线电路一般由总线控制器、总线控制电路、总线供电电路、电阻选址网络(可根据测试需要将总线配置成RT终端模式,通过电阻网络配置相应远置终端)、隔离变压器电路、总线接插件等部分组成。

1553B总线是一种双倍冗余总线结构,所有的节点都同时连结在两条总线上,但只有一条总线工作,另一条作为备份,在正常情况下A总线工作,B总线为备份,当A总线出现故障的情况下,总线控制器自动启动B总线工作[1]。总线控制器内部RAM的容量为4K字,设计零等待工作方式,软件需要读2次完成一次总线RAM或寄存器的操作。与8位CPU芯片连接的总线控制器,将总线控制器的16位数据的高8位和低8位分别与CPU的8位数据相连,同时将数据宽度模式选择引脚(16/8/B)接地,设置总线控制器为8位传输模式[2]。CPU的A0地址位接高低位选择引脚(M/LSB)。这样,CPU读写总线内部缓存数据时,就可以分别对总线控制器16位数据的高、低数据段进行操作。8位模式工作方式下,读取数据前总线控制器内部对数据进行锁存,锁存后分别读取高8位与低8位数据。在设计时考虑信号完整性或者隔离设计,减少干扰源造成数据误锁存的问题。

需要注意的是1553B总线控制器芯片一些输入信号比较敏感,需作特殊处理。复位输入信号为TTL电平形式,抗干扰能力较差,一个很窄的毛刺就会造成芯片复位,为了减少系统信号干扰则需要对该信号进行处理,一般对地加小容量的电容,减少信号干扰的风险,总线控制器的SELECT、STRBD、MEM/REG、RD/WR信号比较敏感,为了防止有干扰信号输入,需要在输入端进行处理,通过串联电阻或者并联电容的方式对线上干扰进行滤除,避免振铃的出现,对于总线控制的长线时钟信号输入应进行整形,采用加斯密特触发器或者串联电阻的方式避免信号线上振铃的影响。

鉴于总线消息发送时对模拟供电的需求较大,即发送消息时需要的电流变大造成模拟供电电压下降,总线控制器模拟供电应与逻辑供电以及其他数字电路供电有良好的隔离,采取的做法是在电路设计中将模拟供电直接连接到电源输出端,逻辑供电以及其他数字电路供电可以通过限流模块连接到电源输出,可以有效减少电压临界造成的系统不稳定情况。以总线接口芯片BU61580为例,接口电路见图4。

2.5 RS-422总线设计

RS-422数据信号采用差分传输方式,它使用一对双绞线平衡传输,有效降低信号传输的干扰程度,硬件包含各4路RS-422发送通道和接收通道,采用点对点的配置方式,包含4个差分发送器和4个差分接收器。

考虑接收端的隔离保护和数据稳定接收,在接收端需要端接电阻和偏置电阻,端接电阻要求其阻值等于传输电缆的特性阻抗,端接电阻接在传输电缆的最远端[3]。偏置电阻的阻值需要根据端接电阻的阻值设计,根据RS-422的通信协议,每次数据传输均以低电平开始,因此接收器在发送器输出禁止的情况下,应保证接收端RX+、RX-之间的电平大于200 mV。为此,需要在RX+、RX-端分别设置上拉和下拉的偏置电阻。为保护发送端不受大电流损伤,在发送端正负线上均串联隔离电阻。隔离电阻的选取还要考虑与端接电阻阻抗匹配的问题,通常1 KΩ的端接电阻,选取510 Ω左右的隔离保护电阻。

2.6 双口RAM设计

该电路允许通过CPCI接口进行读写操作,同时允许中央控制器对其进行读写,完成数据的传输。选用的双口RAM芯片为IDT71342,该芯片为4 K字节双口RAM,同时具有8个地址的SEMPHORE存储空间,提供独立的控制端口,允许异步读写访问,逻辑控制避免同时读写同一地址产生冲突造成数据错误。

2.7 其它

数据传输模块板卡所有器件均采用单一直流+5 V供电,利用底板CPCI接插件+5 V电源供电,在电源输入端加电容去耦,保证供电稳定性。

为了方便验证模块工作状态及进行故障诊断,设置了FPGA工作状态指示灯、CPU工作状态指示灯等,并以不同频度闪烁判定模块是否正常工作,将晶振分频后驱动指示灯闪烁。

3 系统软件实现

卫星与地面设备交互系统的应用软件包括上位计算机软件、下位工控机软件和数据传输模块嵌入式软件组成。

上位计算机应用软件由测试控制、数据处理显示软件、遥测格式比对软件等组成,通过视窗操作界面控制和显示。

下位工控机软件完成与上位机的网络通讯功能,以及控制数据传输模块数据采集和按照相应协议实施总线控制、总线监听和总线终端数据模拟等功能。工控系统主模块控制软件运行在VXworks操作系统下,VXworks操作系统主要功能在于提供应用软件所需的各种进程调度原语、进程间通信原语和底层硬件驱动程序,工控机控制软件工作流程如图5。

图5 下位工控机控制软件工作流程图

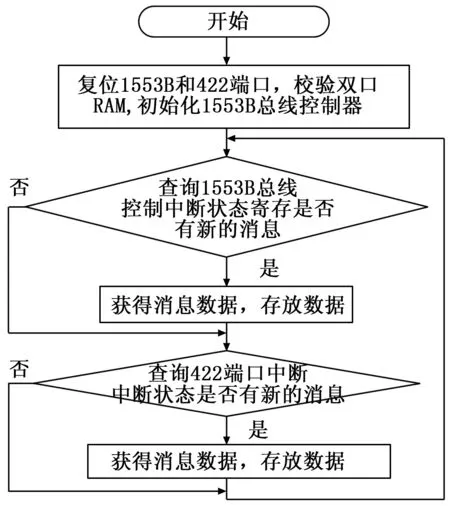

数据传输模块软件实现外部数据接收并将数据分块存储于双口RAM中,下位机工控软件定期查询双口RAM区中数据状态,并通过以太网将数据传送至远程计算机,同时下位机工控软件通过CPCI接口向中央控制器发出复位、中断等功能信号,控制数据传输模块从设备工作,数据传输模块软件实现流程如图6所示。

4 试验验证结果与分析

应用这套测试系统在某深空领域卫星的测试环境中实现了1553B总线协议的动态模拟,增强了仿真的灵活性和真实性,RS-422接口的应用使得上下行数据及时更新,是卫星状态控制的便捷途径,提高了测试应急响应时间,从而保证了测试的安全性,数据传输实时性好,该系统已经在多个卫星综合测试阶段及外场试验中长期稳定工作。

5 结论

本文讨论了基于CPCI总线的卫星和地面设备交互实现方法,采用CPCI工控机作为数据传输模块的安装载体,且工控机对环境适应范围较宽,安全性高,并可适应特殊环境下的长期应用;采用标准的模块板卡使用方便、灵活,便于拆卸和安装;该数据传输模块采用FPGA代替分立元件,采用表贴窄封装器件等措施减小了印制板面积,节省了布局空间;采用专用总线接口控制芯片,通用性好,开发周期短、成本低;同时根据用户使用环境可灵活定制功能,将监视到的数据分类存储和传输。该方案选用开放式标准、模块化设计,便于维护,可移植性好,该数据传输方法经工程实现和验证,通过进一步的分析和验证,模块运行稳定可靠,满足用户使用需求,并经过多种卫星测试系统上推广应用,取得了良好效果。

[1] 史林锋,王斌永,何志平,等.基于FPGA和BU-65170的1553B远程终端设计与实现[J].现代电子技术,2013,36:(14):65-69.

[2] 郭廷源,牛跃华,王红光. 基于单片机的1553B总线数据交换设备设计[J].计算机测量与控制,2013,21(1):195-196,199.

[3] 牛思先,向 征.基于RS-422/485的串行异步通讯接口设计和应用[J].计算机工程与设计 2007,28(10):2472-2474.