基于FPGA的高频数字鉴相技术

2018-02-28张绘王艳涛

张绘 王艳涛

摘要

针对传统模拟鉴相中存在的器件一致性低导致的信号正交性差且易受环境影响等现象,本文提出了一种基于FPGA的高频数字鉴相技术,并通过硬件板卡验证了该技术的有效性。实验结果表明该技术有很大的工程可实现性。

【关键词】带通采样 高频数字鉴相 多相低通滤波

1 引言

宽带探测系统可以很好的利用大带宽信号提供的更加丰富的目标信息和高分辨率,一般用与SAR/ISAR成像等应用,是实现成像雷达的关键技术。但是由于大带宽的影响,整个接收通道的设计十分困难,采用射频直采可有效简化接收通道的设计难度,灵活性更大,是实现数字接收机的关键技术。同时鉴相质量直接决定了后续算法的结果质量,对系统指标十分关键。

本文提出了一种基于FPGA的通用高频数字鉴相技术,采用数字信号处理的方法进行鉴相,提高处理精度。该技术将射频信号直接经过AD采样后得到高频的数字信号,然后通过FPGA进行高频数字鉴相得到用于后端信号处理的I/Q信号,相对于传统的鉴相方法,减轻了前端模拟处理对性能的影响,并且更符合软件无线电技术的发展趋势。

2 高频数字鉴相

如图1所示,高频数字鉴相的处理流程如下:将AD采样得到的数字信号传送到FPGA中,在此过程中,对数据进行了扩位降速处理;通过Matlab设计生成用于在FPGA中实现滤波器的系数进行滤波,由于数据量过大,进行带通滤波时采用了多路并行处理的方法;将Mattab中设计的正余弦信号存入到FPGA的块RAM中,运用读取出的本振信号与带通滤波后的信号相乘实现变频;在多相低通滤波的过程中选择对固定的相位进行滤波处理来达到数据降速的目的,滤波之后的结果就是PQ路数字信号。

2.1 高频AD采样

根据带通采样得知采样频率应满足以下两个关系式

其中B为被采样带通信号的带宽,本文中为130MHz;Fc为被采样带通信号的中心频率,本文中为1.29GHz;m为满足(公式1)和(公式2)的任意正整数;Fs为采样频率,根据(公式1)和(公式2),本文中采用960MHz。

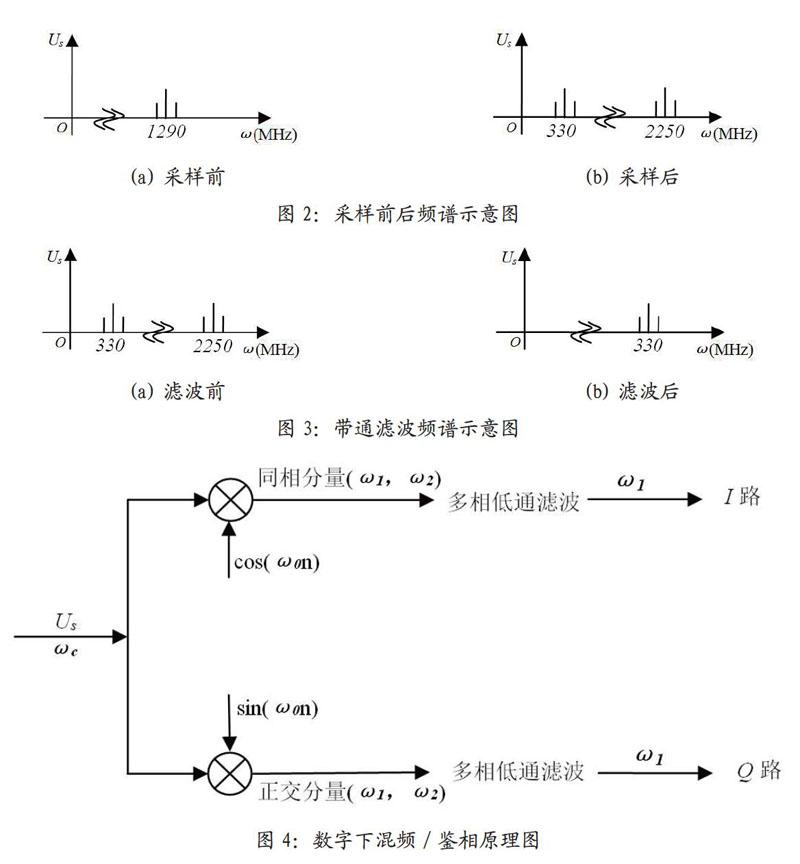

根据采样定理,采样前后的频谱示意图如图2所示。

2.2 带通滤波

根据将信号混频至零载频的需求,只需对靠近零频率的带通采样结果进行下变频就可以实现,所以用中心频率330MHz、带宽130MHz的带通滤波器对前端的带通采样结果进行滤波处理。如图3所示。

2.3 数字下混频/鉴相

对滤取出来的结果进行下变频以及鉴相最终得到I/Q路数字信号。如图4所示。

本次试验中参数设置分别为:

3 硬件实现

硬件实现过程的FPGA程序开发使用XELINX公司的ISE13.2硬件开发工具,FPGA选择的是XC5VLX95T芯片,采用VHDL语言编程的方式实现,系统的采样率为960MHz、输入AD采样的模拟中频信号为1290MHz,带宽为130MHz。

3.1 数据传输

将AD采样得到的数字信号采用JESD204B传输协议传送到FPGA中。在此过程中,AD采样得到的数字信号数据率为960MHz,而FPGA的系统时钟为120MHz,为了满足FPGA的系统时钟的要求,首先通过FPGA内部FIFO对数据进行了扩位降速处理,即FIFO的输入参考时钟为960MHz、输入数据位宽为14位,输出参考时钟为120MHz、输出数据位宽为112位。

3.2 带通滤波

在本文硬件实现过程中,通过Matlab设计生成用于在FPGA中实现滤波的系数文件,该滤波器为16阶的带通滤波器,滤波器的中心频率为330MHz,带宽為130MHz。

为了同时满足960MHz的数据率和120MHz的系统时钟,在FPGA中进行带通滤波时采用多路并行处理的方法,即生成16路乘法通道,一个系统时钟下完成16次乘法运算。

3.3 数字下变频/鉴相

在硬件实现过程中,数字下变频采用的数字本振信号是由Matlab产生的正余弦信号,存入FPGA的BlockRAM中。其中正信号的频率为330MHz。通过Matlab设计生成用于在FPGA中实现多相低通滤波器的系数文件,该滤波器是32阶的低通滤波器,带宽为75MHz。

将FPGA中存储的本振信号与带通滤波后的信号相乘实现变频,其过程如图5所示,在此过程中采用了多路并行处理的方法。

在该硬件实现过程中考虑到系统时钟是120MHz,采样率是960MHz的问题,在滤波的过程中选择对固定的相位进行滤波处理来达到数据降速的目的。

3.4 试验结果

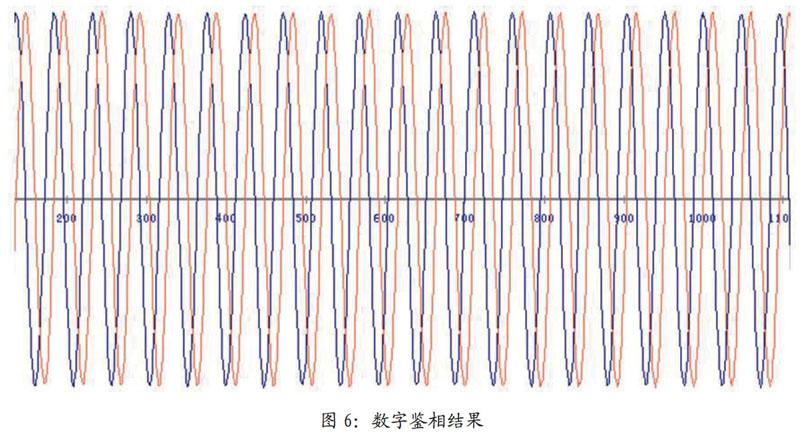

本文中通过信号源给AD板卡提供信号和时钟,信号带宽130MHz,中心频率1.29GHz,采样频率为960MHz,最终通过FPGA中Chipscope采集鉴相结果如图6所示,其中红色和蓝色分别为鉴相后的两路信号。

4 结束语

本文主要介绍了一种基于FPGA的高频数字鉴相技术的实现方法,结合FPGA的实现特点完成了频谱的搬移和相位的鉴别,采用了并行处理的方式降低了数据率并提高了处理的实时性,通过多相滤波的高效结构减少了运算量,节省了大量的FPGA资源,并经过实际硬件测试证明,该技术的FPGA实现运行状态稳定可靠,具有工程可实现性。